高速电路中的过孔效应与设计

描述

随着电子设计向更高速度发展,过孔在PCB设计中的重要性日益凸显。在低频应用中,过孔对信号传输的影响可以忽略不计,但当时钟频率提高、信号上升时间缩短时,过孔引起的阻抗不连续性成为影响信号完整性的关键因素。

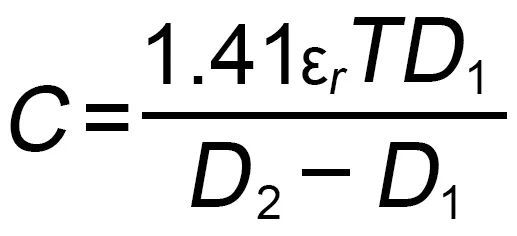

过孔本质上可以视为由电容、电感和电阻组成的参数模型,其特性可通过场提取工具或TDR测试获得。计算公式计算:

D2:过孔区直径:inch;

DI:过孔焊盘直径:inch;

T:PCB厚度: inch;

ε:介电常数;

C:过孔寄生电容:pF

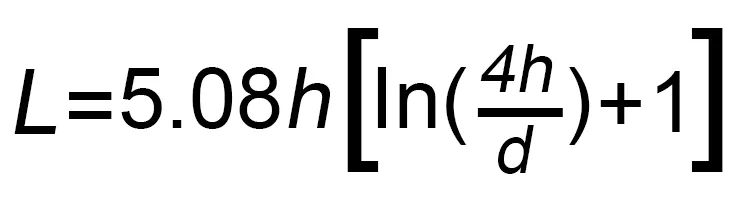

过孔的寄生电容主要受过孔区直径、焊盘直径、PCB厚度和介电常数影响,而寄生电感则主要取决于过孔长度和直径。一般而言,较小的过孔会产生较小的寄生电容.

h: 过孔长度:inch;

d: 过孔直径:inch;

L: 过孔寄生电感:nH

在工程实践中,仿真分析时常将过孔模型近似为1pF电容,TDR测试显示其引起的瞬态阻抗降落约为6-7欧姆。

过孔对信号传输的负面影响主要表现在以下几个方面:

1.改变PCB走线的特征阻抗,引入固有电容

2.造成走线特征阻抗的跳变,导致约5%的负反射系数

3.使信号在层间跳转时改变参考平面和回流路径

4.当参考平面发生变化时,可能导致传输线特征阻抗显著改变

对于上升时间在0.5-1.0ns范围的信号,单个过孔造成的几十皮秒边沿变缓影响相对较小,但多个过孔的累积效应不可忽视。过孔还会延长信号传输时间,一个过孔大约会增加几百皮秒的走线延时,对于长走线而言影响较小。

为减轻过孔带来的不良影响,PCB设计中应当尽量减少过孔数量,在布线换层时优先选择阻抗连续的平面进行切换。值得注意的是,对于频率低于1GHz的信号,相比避免过孔,更应优先考虑内层布线以减小辐射影响。

当信号线必须通过过孔跨层布线时,应在信号过孔附近添加地属性过孔,以提供良好的回流路径。对于多层PCB设计,确保地层作为信号回流的主通道至关重要。在敏感信号必须跨层时,理想的做法是对信号线进行包地处理,使包地线与信号线平行且尽可能靠近,从而维持良好的信号完整性。

-

高速PCB设计中,如何避免过孔带来的负面效应2024-01-05 1077

-

高速pcb中的过孔设计原则2023-08-01 1948

-

高速PCB过孔仿真的流程2023-06-19 2251

-

高速PCB中的过孔设计2023-01-29 1472

-

高速PCB中过孔的问题及设计要求2022-11-10 7208

-

pcb过孔设计中设计电路时对过孔的处理原则 过孔阻抗设计要匹配生产能力2020-12-15 7550

-

过孔的基本概念2020-09-27 12161

-

高速PCB中怎样来设计过孔2020-03-13 2831

-

高速PCB中的过孔设计,你真的懂吗?2019-09-25 3295

-

高速PCB中过孔怎样来设计才合理2019-09-04 904

-

减小高速PCB中过孔的寄生效应带来的不利影响的方法2018-01-27 8002

-

高速PCB过孔的研究2017-11-18 2711

-

如何使用过孔2012-02-02 1963

-

高速电路中过孔设计2009-08-16 751

全部0条评论

快来发表一下你的评论吧 !