LP2998-Q1 用于汽车应用的 DDR 终端稳压器数据手册

描述

LP2998 线性稳压器旨在满足 JEDEC SSTL-2 和 JEDEC SSTL-18 标准 DDR-SDRAM 和 DDR2 内存终止的规范。该器件还支持 DDR3 和 DDR3L VTT 总线端接,带 VDDQ分钟 的 1.35 V。该器件包含一个高速运算放大器,可提供出色的响应 负载瞬变。输出级可防止击穿,同时提供 1.5 A 连续电流 以及 DDR-SDRAM 端接所需的应用中高达 3 A 的瞬态峰值。LP2998 系列 还集成了 VSENSE 引脚,以提供出色的负载调节和 V裁判输出作为芯片组和 DIMM 的参考。

LP2998 的另一个功能是低电平有效关断 (SD) 引脚,提供 Suspend To RAM (STR) 功能。当 SD 被拉低时,VTToutput 将三态 提供高阻抗输出,但是,V裁判将保持活动状态。一 在此模式下,可以通过较低的静态电流获得 SAVINGS ADVANTAGE。

*附件:lp2998-q1.pdf

特性

- AEC-Q100 测试指南,结果如下(SO PowerPAD-8):

- 器件 HBM ESD 分类等级 H1C

- 结温范围 –40°C 至 125°C

- 1.35 V 最小 V

DDQ - 拉电流和吸收电流

- 低输出电压偏移

- 无需外部电阻器

- 线性拓扑

- 挂起到 RAM (STR) 功能

- 外部元件数量少

- 热关断

参数

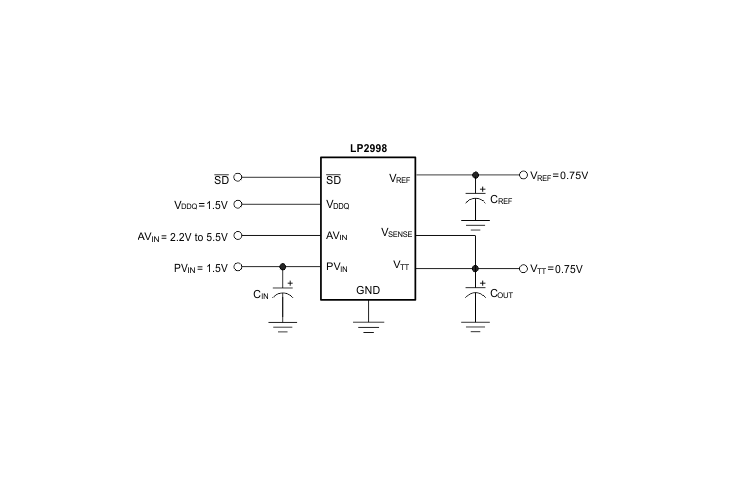

方框图

1. 概述

LP2998-Q1 是一款线性稳压器,专为满足 JEDEC SSTL-2 和 JEDEC SSTL-18 标准而设计,用于 DDR-SDRAM 和 DDR2 内存的终止。该器件还支持 DDR3 和 DDR3L VTT 总线终止,并具有低输出电压偏移、快速瞬态响应和高电源抑制比等特点。

2. 主要特点

- AEC-Q100 认证:适用于汽车应用

- DDR 终止:支持 DDR1、DDR2、DDR3 和 DDR3L 内存

- 低 V_DDQ:最小值为 1.35V

- 高速运算放大器:提供优秀的负载瞬态响应

- 输出阶段:可防止穿透,同时提供 1.5A 连续电流和高达 3A 的瞬态峰值电流

- V_SENSE 引脚:提供卓越的负载调节

- V_REF 输出:作为芯片组和 DIMMs 的参考电压

- 低外部组件计数:无需外部电阻

- 热关断保护:防止过热损坏

- 挂起至 RAM (STR) 功能:通过 SD 引脚实现低功耗模式

3. 应用场景

- 汽车信息娱乐系统

- 工业/医疗设备

- FPGA 供电

4. 引脚配置与功能

LP2998-Q1 采用 SO PowerPAD-8 封装,主要引脚包括:

- GND:接地

- SD:关断引脚,低电平有效

- V_SENSE:反馈引脚,用于调节 V_TT

- V_REF:缓冲内部参考电压输出

- AVIN:模拟输入引脚

- PVIN:电源输入引脚,专用于输出级

- VTT:输出电压,用于连接终止电阻

- EP:外露焊盘,热连接,接地

5. 功能描述

- 线性稳压器:输出 V_TT 能够精确调节至 V_DDQ/2,同时支持源电流和灌电流。

- 高速运算放大器:提供快速负载瞬态响应。

- 分离电源轨:模拟电路和功率输出级采用不同的电源轨,降低内部功耗。

- STR 功能:SD 引脚拉低时,V_TT 输出三态,但 V_REF 保持激活。

6. 电气特性

- 输入电压范围:AVIN 为 2.2V 至 5.5V,PVIN 为 0V 至 AVIN

- 输出电压:V_TT 根据 V_DDQ 调节,例如 V_DDQ = 2.5V 时,V_TT = 1.25V

- 负载调节:通过 V_SENSE 引脚实现远程负载调节

- 静态电流:典型值为 500µA

- 热关断温度:约 165°C

7. 典型应用电路

数据手册中提供了多个典型应用电路,包括 DDR-III、DDR-II、SSTL-2 和 HSTL 应用,以及如何通过反馈电阻进行电平移位。

8. 布局与热设计指南

- 输入电容:应靠近 PVIN 引脚放置,推荐值为 50µF 电解电容或 10µF 陶瓷电容。

- V_SENSE 引脚:应连接到 V_TT 终止总线的中心位置,以提供最佳的负载调节。

- 热设计:通过多层板设计、过孔和铜皮来优化热性能。

9. 封装与订购信息

LP2998-Q1 提供 SO PowerPAD-8 封装选项,具有 RoHS 环保认证。数据手册中提供了详细的封装尺寸、引脚分配和订购信息。

10. 注意事项

- 在使用期间,应遵守数据手册中提供的绝对最大额定值和推荐操作条件。

- 注意静电放电保护,避免损坏器件。

- 数据手册中的信息仅供参考,实际设计时应进行充分的验证和测试。

-

LP2998/LP2998 - Q1 DDR 端接稳压器:设计与应用指南2026-03-18 379

-

Texas Instruments LP2951-Q1低压差 (LDO) 稳压器数据手册2025-07-11 909

-

LP2995系列 DDR 终端稳压器数据手册2025-05-06 896

-

LP2998系列 带关断引脚的 1.5A DDR 终端稳压器数据手册2025-04-29 1187

-

TPS51200-Q1 汽车目录 灌电流/拉电流 DDR 端接稳压器数据手册2025-04-28 1180

-

TPS51200-EP 灌电流/拉电流 DDR 终端稳压器数据手册2025-04-26 1774

-

TPS51200A-Q1 灌电流和拉电流 DDR 终端稳压器数据手册2025-04-25 1360

-

LP3996-Q1 汽车级150-mA,低IQ,双通道低压差稳压器数据手册2025-03-04 898

-

DDR终端调节器LP2998/LP2998-Q1数据表2024-03-28 576

-

灌电流和拉电流 DDR 终端稳压器TPS51200A-Q1数据表2024-03-13 498

-

LTC3617:±6A单片同步降压稳压器,用于DDR终端数据表2021-04-15 912

-

用于 DDR 终端的高效率 ±6A 开关稳压器符合 DDR / DDR2 / DDR3 标准2021-03-21 962

-

用于 DDR 电源及终端的高效率、双通道、±3A同步降压型稳压器符合 DDR / DDR2 / DDR3 标准2021-03-19 1079

全部0条评论

快来发表一下你的评论吧 !