ADF4001 200MHz时钟发生器PLL技术手册

描述

概述

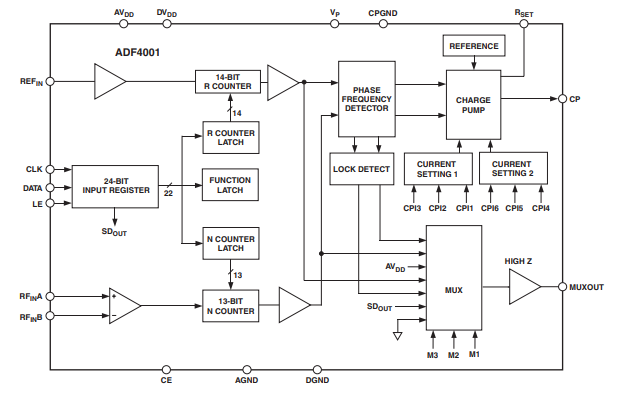

ADF4001频率合成器可用来实现要求极低噪声、稳定基准信号的PLL的时钟源。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器和可编程13位N分频器组成。此外,14位参考分频器(R分频器)允许PFD输入端的REFIN频率为可选值。如果频率合成器与外部环路滤波器和电压控制振荡器(VCO)或电压控制晶体振荡器(VCXO)一起使用,则可以实现完整的锁相环(PLL)。N的最小值为1,这为时钟产生提供了灵活性。

数据表:*附件:ADF4001 200MHz时钟发生器PLL技术手册.pdf

特性

- 200 MHz带宽

- 电源电压范围:2.7 V至5.5 V

- 可编程电荷泵电流

- 三线式串行接口

- 硬件和软件掉电模式

- 模拟和数字锁定检测

框图

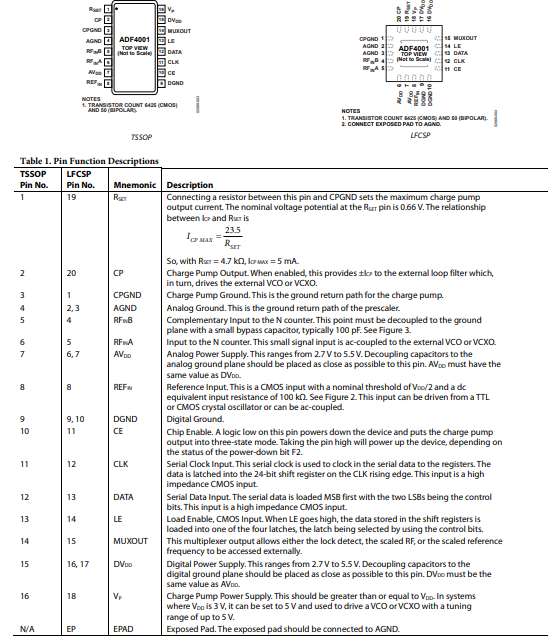

引脚配置描述

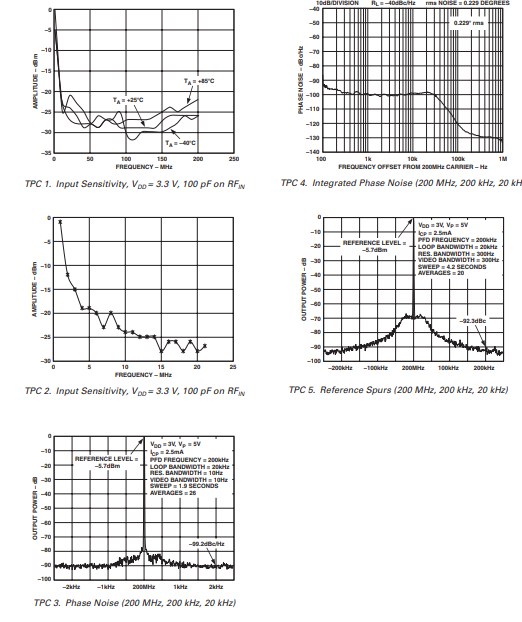

典型性能特征

电路说明

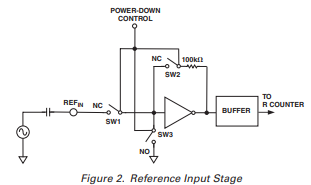

参考输入部分

参考输入级如图2所示。SW1和SW2通常处于闭合状态,SW3通常处于断开状态。当进入掉电模式时,SW3闭合,SW1和SW2断开。这确保了在掉电时参考引脚((REF_{IN}))不会有负载。

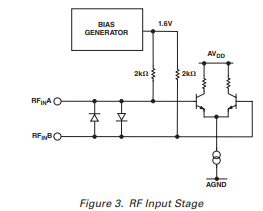

射频输入部分

射频输入级如图3所示。其后接一个两级限幅放大器,以生成N计数器缓冲器所需的电流模式逻辑(CML)时钟电平。

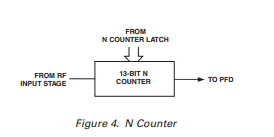

N计数器

N CMOS计数器可在锁相环(PLL)反馈回路中实现较宽范围的分频比。允许的分频比范围是1到8191。

N与R的关系

N计数器与R计数器配合,能够生成间隔仅为参考频率除以R的输出频率。压控振荡器(VCO)频率的计算公式为:

[ f_{VCO} = N×frac{f_{REFIN}}{R} ]

其中:

- (f_{VCO})是外部压控振荡器(VCO)的输出频率。

- (N)是13位二进制计数器的预设分频比(1到8191)。

- (f_{REFIN})是外部参考频率振荡器的频率。

- (R)是14位二进制可编程参考计数器的预设分频比(1到16,383)。

R计数器

14位R计数器可对输入参考频率进行分频,以产生送往鉴频鉴相器(PFD)的参考时钟。允许的分频比范围是1到16,383 。

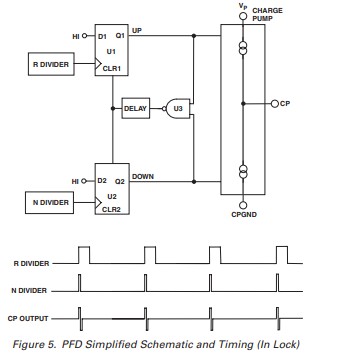

鉴频鉴相器(PFD)和电荷泵

鉴频鉴相器接收来自R计数器和N计数器的输入,并输出一个与两者之间相位和频率差成正比的信号。图5是简化示意图。鉴频鉴相器包含一个可编程延迟元件,用于控制抗反冲脉冲的宽度。此脉冲功能确保了鉴频鉴相器传递函数中不存在死区,并将相位噪声以及参考杂散降至最低。参考计数器锁存(ABP2和ABP1)中的两位控制脉冲宽度(见表III)。

多路复用输出(MUXOUT)和锁定检测

ADF4001系列的输出多路复用器允许通过功能表中的M3、M2和M1控制MUXOUT。表V显示了完整的真值表。图6以框图形式展示了MUXOUT部分。

-

200 MHz时钟发生器PLL ADF4001:高性能时钟解决方案2026-04-20 136

-

MAX9491工厂可编程、单PLL时钟发生器技术手册2025-04-27 1179

-

EVADF4001 ADF4001 评估板2021-06-04 775

-

HMC1031:0.1 MHz至500 MHz时钟发生器,带整数N PLL数据表2021-04-23 903

-

ADF4001:200MHz Clock发电机PLL数据Sheet2021-04-14 1126

-

ADF4001设计文件2021-03-22 903

-

UG-092: ADF4001 PLL频率合成器评估板2021-03-19 819

-

ADF4001 Design Files2021-01-28 865

-

如何创建一个具有200MHz输入和640MHz,160MHz输出的时钟发生器?2020-08-11 2053

-

EVAL-ADF411xEBZ1,ADF411x评估板,用于SONET的200 MHz PLL时钟发生器2019-09-03 1467

-

ADF4001锁定不正常2019-03-12 4083

-

ADF4001 200 MHz 时钟发生器PLL2019-02-22 1202

-

ADF4001,pdf datasheet (200 MHz2009-09-16 779

全部0条评论

快来发表一下你的评论吧 !