ADF4252双路小数N/整数N频率合成器技术手册

描述

概述

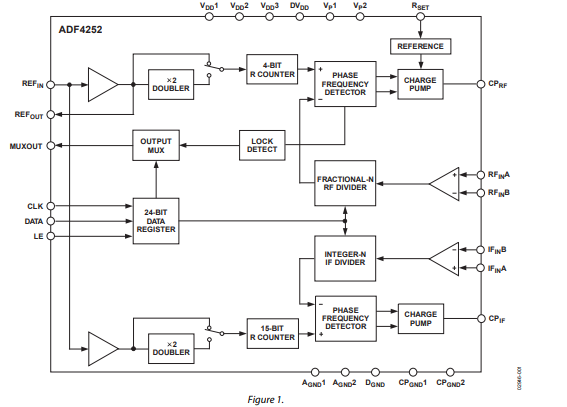

ADF4252 是一款双路小数 N/整数 N 频率合成器,可用于在无线接收器和变送器的升频转换和降频转换部分实施本地振荡器 (LO)。RF 和 IF 频率合成器由低噪声数字相位频率检波器 (PFD)、精密电荷泵和可编程基准分频器构成。RF 频率合成器具有一个基于 Σ-Δ 的小数内插器,可实现可编程小数 N 分频。IF 频率合成器具有可编程整数 N 计数器。如果将频率合成器与外部环路滤波器和压控振荡器 (VCO) 配合使用,即可实现完整的锁相环 (PLL)。

所有片内寄存器均通过简单的三线式接口进行控制。该套件采用 2.7 V 至 3.3 V 电源工作,并可在不使用时关断电源。

数据表:*附件:ADF4252双路小数N 整数N频率合成器技术手册.pdf

应用

- 移动无线电基站(GSM、PCS、DCS、CDMA、WCDMA)

- 无线手机(GSM、PCS、DCS、CDMA、WCDMA)

- 无线 LAN

- 通信测试设备

- CATV 设备

特性

- 3.0 GHz 小数 N/1.2 GHz 整数 N

- 2.7 V 至 3.3 V 电源

- 单独的 V

P允许将调谐电压扩展至 5 V - 可编程双模数预分频器

- RF:4/5, 8/9

- IF:8/9, 16/17, 32/33, 64/65

- 可编程电荷泵电流

- 3 线串行接口

- 数字锁定检测

- 关断模式

- 可编程模数小数 N 频率合成器

- 折衷噪声与杂散性能

框图

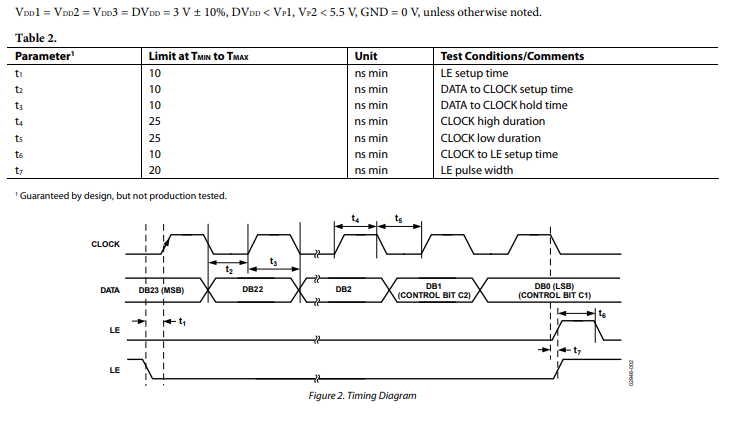

时序特征

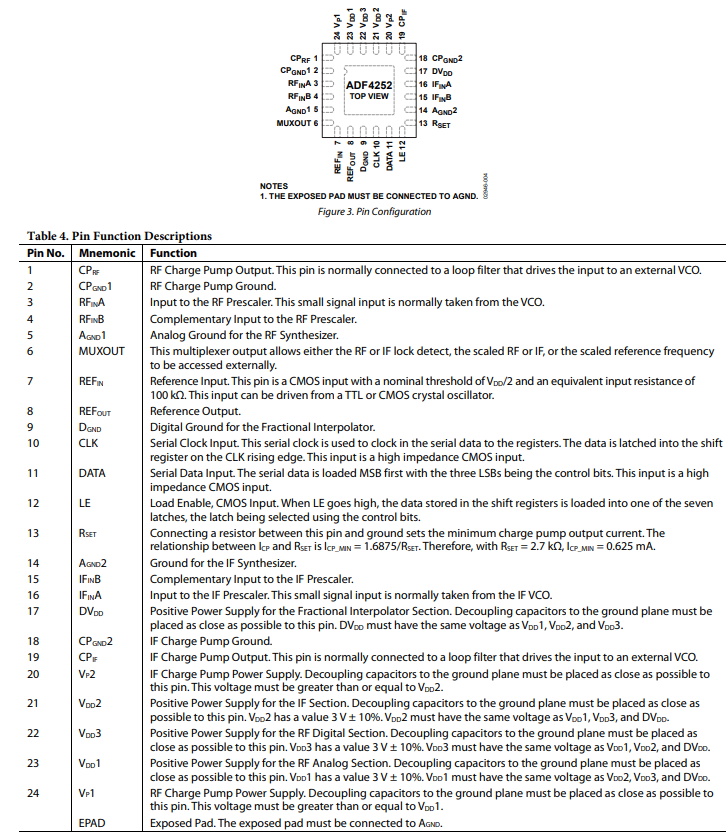

引脚配置描述

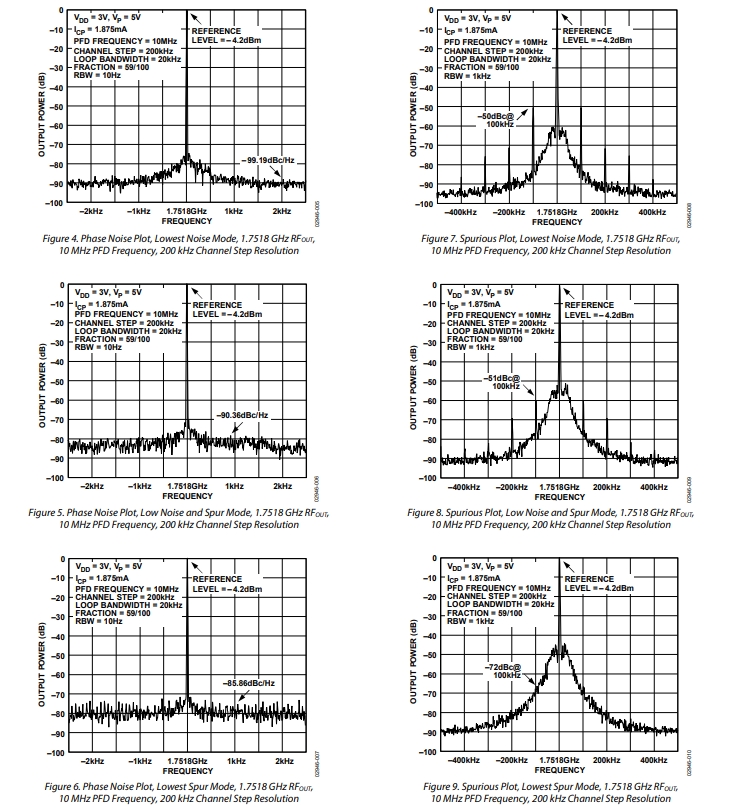

典型性能特征

工作原理

参考输入部分

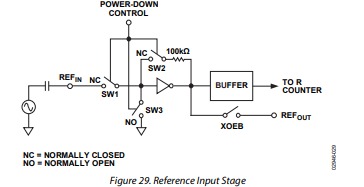

参考输入级如图29所示。SW1和SW2通常处于闭合状态,SW3通常处于断开状态。当启动掉电模式时,SW3闭合,SW1和SW2断开。这确保了在掉电时参考引脚((REF_{IN}))不会有负载。

射频和中频输入部分

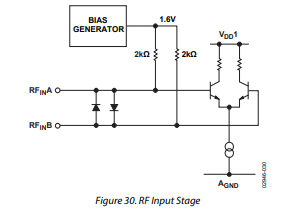

射频输入级如图30所示。中频输入级与之相同。其后接一个两级限幅放大器,以生成N计数器所需的电流模式逻辑(CML)时钟电平。

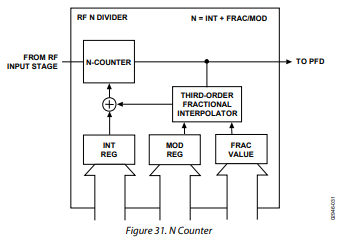

射频整数分频器

射频整数CMOS计数器可在锁相环(PLL)反馈回路中实现分频比。允许的分频比范围是31到255 。

整数(INT)、分数(FRAC)、模数(MOD)与R的关系

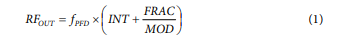

INT、FRAC和MOD的值,与射频R计数器配合,能够生成与射频鉴频鉴相器(PFD)分数间隔相同的输出频率。射频压控振荡器(RF VCO)频率公式如下:

其中:

- (RF_{OUT})是外部压控振荡器(VCO)的输出频率。

- (f_{PFD})是鉴频鉴相器频率(见公式2)。

- (INT)是8位二进制计数器的预设分频比(31到255)。

- (FRAC)是12位二进制可编程FRAC计数器的预设分数分频比(0到MOD )。

- (MOD)是12位二进制可编程FRAC计数器的预设模数(2到4095)。

其中:

- (REF_{IN})是参考输入频率。

- (D)是射频(REF_{IN})倍频位。

- (R)是4位二进制可编程参考计数器的预设分频比(1到15)。

射频R计数器

4位射频R计数器可对输入参考频率((REF_{IN}))进行分频,以产生送往射频鉴频鉴相器(PFD)的参考时钟。允许的分频比范围是1到15 。

中频R计数器

15位中频R计数器可对输入参考频率((REF_{IN}))进行分频,以产生送往中频鉴频鉴相器(PFD)的参考时钟。允许的分频比范围是1到32,767 。

-

ADF4252双分数N/整数N频率合成器技术剖析2026-04-20 117

-

Analog Devices Inc. ADF41510整数N/小数N PLL合成器数据手册2025-06-04 995

-

ADF4155整数N/小数N分频PLL频率合成器技术手册2025-04-25 1250

-

EVADF4252 ADF4252 评估板2021-06-03 842

-

ADF4252:双小数-N/整数-N频率合成器数据表2021-05-20 863

-

UG-804:评估ADF4355-2小数/整数N锁相环频率合成器2021-05-10 1030

-

ADF4251:双小数/整数N频率合成器数据表2021-04-29 782

-

UG-873:评估ADF4355-3小数/整数N锁相环频率合成器2021-04-28 902

-

ADF4150:小数N/整数N PLL合成器数据表2021-04-23 761

-

ADF4151:小数N/整数N PLL合成器数据表2021-04-14 879

-

ADF4153:小数N分频频率合成器2021-03-21 1424

-

ADF4155:整数N/小数N分频PLL频率合成器2021-03-20 951

-

EV-ADF411xSD1Z用于评估ADF411x整数N和小数N分频PLL频率合成器2019-07-15 1880

全部0条评论

快来发表一下你的评论吧 !