FPGA的Jtag接口烧了,怎么办?

描述

在展开今天的文章前,先来讨论一个问题:

FPGA的jtag接口烧了怎么办?

JTAG 接口的输入引脚通常设计为高阻抗,这使得它们对静电电荷积累非常敏感,由于JTAG 接口需要频繁连接调试器、下载线缆等外部设备,插拔过程中极易因摩擦产生静电。JTAG 接口经常会有带电拔插的情况,这不可避免地会产生静电或浪涌电流。JTAG 接口的引脚直接与 FPGA 内部的测试访问端口(TAP)控制器和配置电路相连,这意味着外界的异常电压或电流可以直接作用于这些关键的内部电路,没有太多的缓冲和保护。如果接口受到过压、过流的影响,损坏很可能会迅速蔓延到内部核心电路,造成严重的后果。

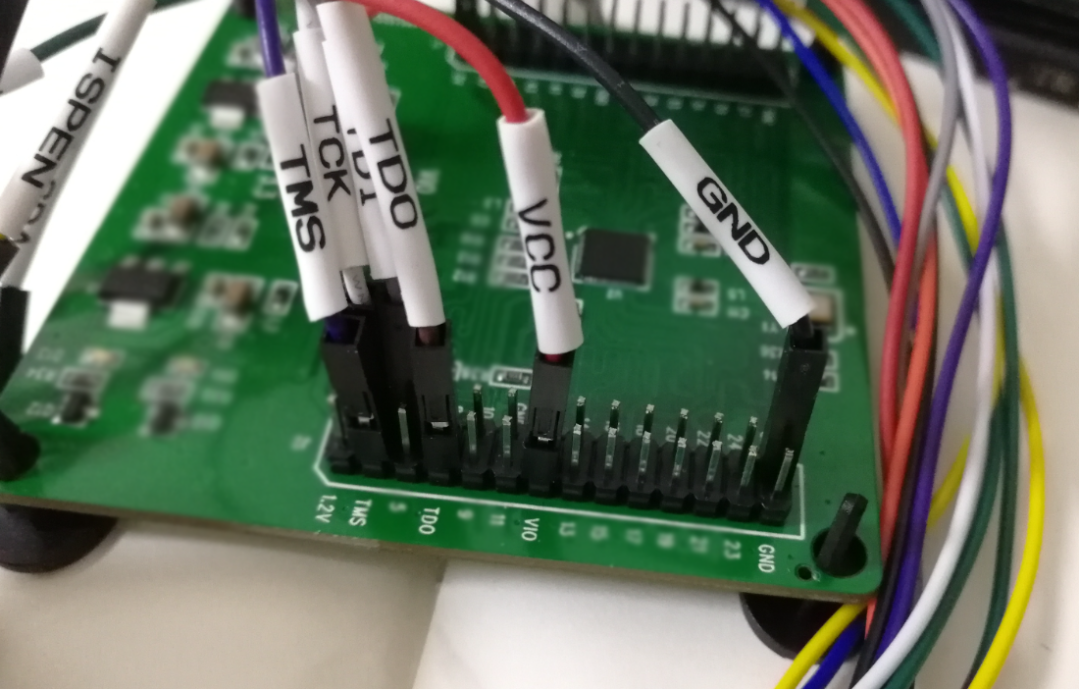

传统FPGA开发板通常扩展出FPGA的Jtag接口,需用户对照Jtag接口线序和电源管脚手动连接外部烧录器(如下图),在初学者当中常易出现不当的操作,如在板卡通电的情况下插/拔jtag接口以及Jtag接口线序连接错误(特别是电源接反)等情况,很可能会导致FPGA器件的损坏。

若损坏发生在 FPGA 芯片内部,这种情况的维修难度极大,通常需要专业的设备和技术,成本较高,且成功率不一定能得到保证。所以FPGA的JTAG 接口一旦烧坏,意味着FPGA芯片已如同“板砖”,重新配置和调试功能基本不可用。

Jtag接口对FPGA的开发、调试、测试及维护具有不可替代的意义,是 FPGA 从 “空白芯片”到“定制化电路”的必经之路,也是将FPGA内部信号实时抓取并传输至 PC 端,实现对复杂时序逻辑的可视化调试,快速定位信号毛刺、时序违例等问题重要手段。

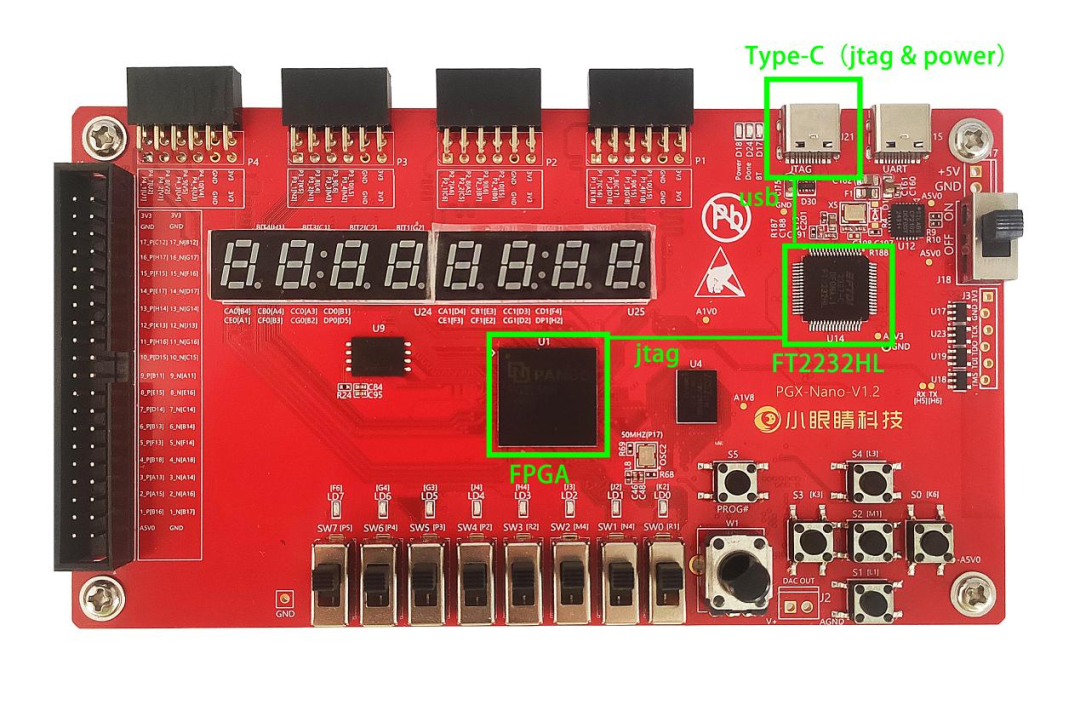

为避免初学者在使用FPGA开发板Jtag接口时出现以上问题,PGX-Nano开发板集成FT2232HL实现USB转Jtag接口,用户通过Type-C接口连接开发板即可实现Jtag接口烧录及调试,同时Type-c接口也作为开发板的供电接口使用,真是一举两得。

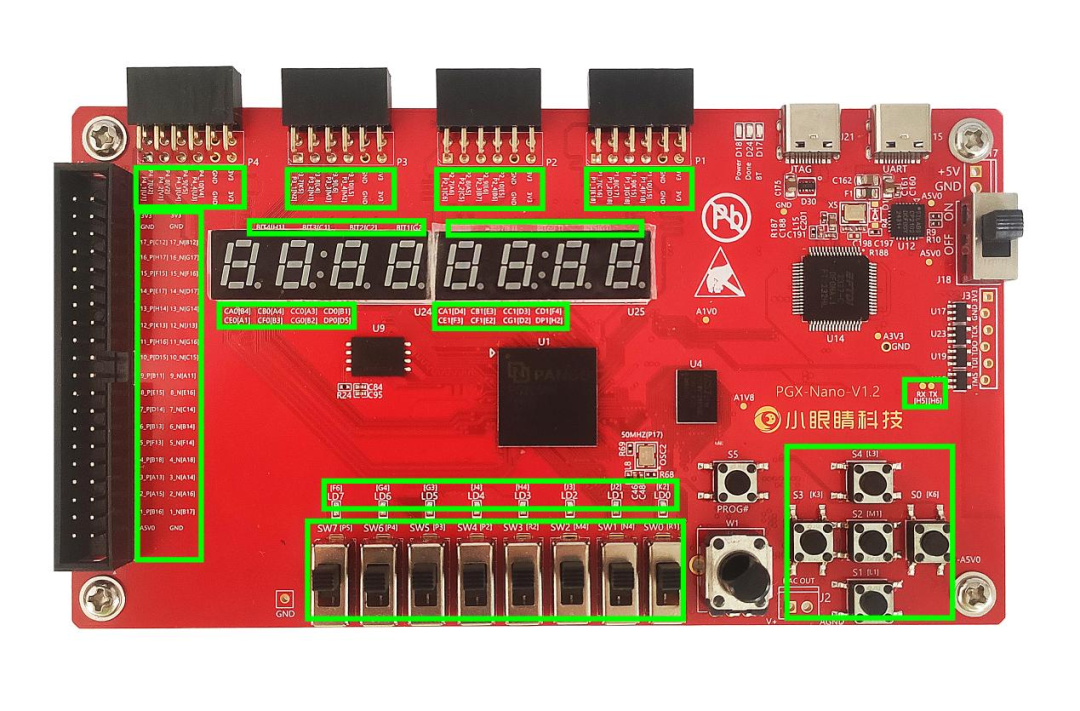

除此之外,FPGA工程在管脚约束的过程中,往往需要从原理图或硬件手册中查找对应外设所使用的FPGA管脚序号再进行管脚约束。PGX-Nano开发板的每个外设接口都以硬件丝印的形式标明对应的FPGA管脚序号,用更直观的方式便于用户直接进行管脚约束和理解FPGA IO的可编程特性。

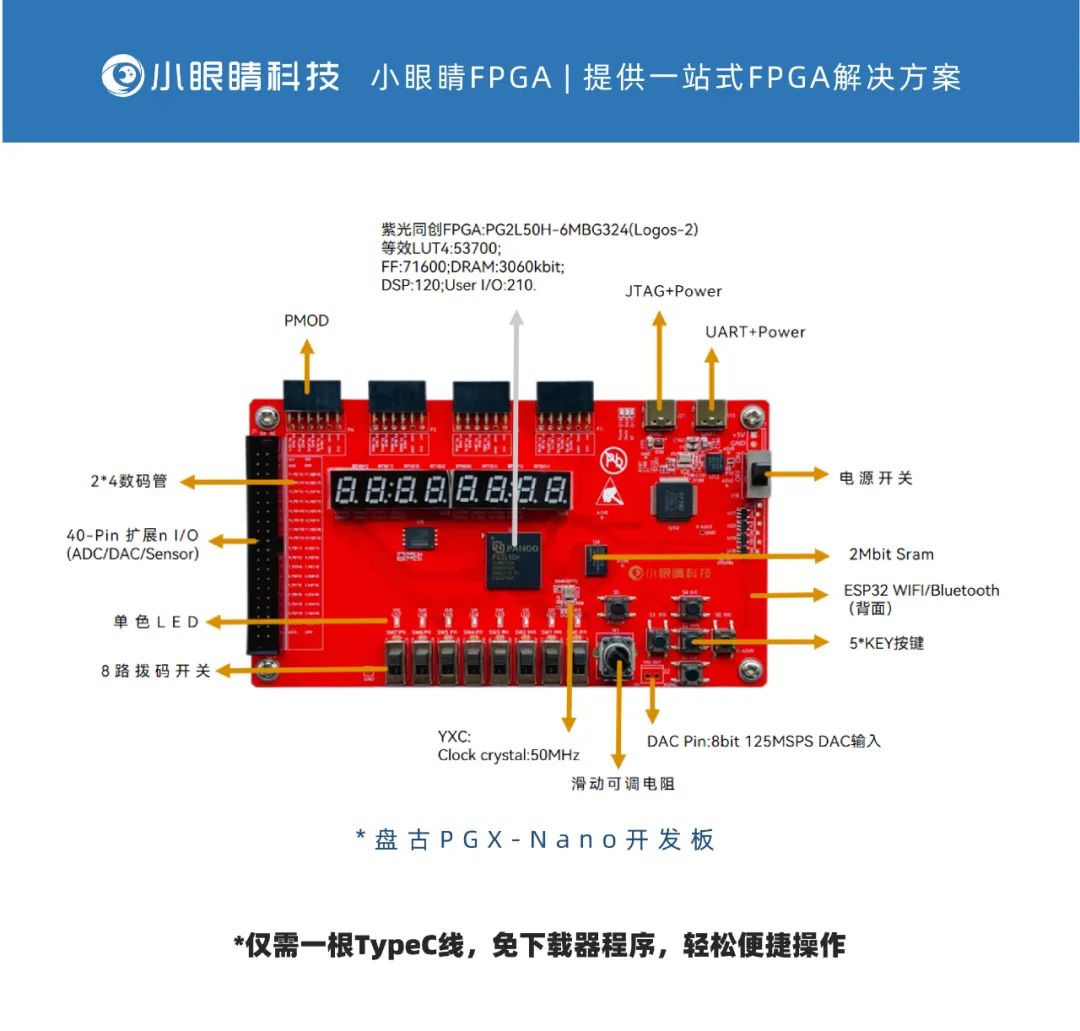

PGX-Nano是一套以紫光同创FPGA为核心的开发板,选用紫光同创logos2系列28nm工艺的FPGA(PG2L50H_6IMBG324)。

PGX-Nano板卡搭载一颗容量为2Mb的SRAM用于数据缓存,MS9708实现高速8bit DAC,esp32模组实现WIFI、蓝牙透传,CP2102实现串口通信;预留了40pin扩展IO以及4个PMOD接口可连接丰富的外设模块,同时为用户提供led灯、按键、拨码开关和数码管等基础的硬件电路资源。

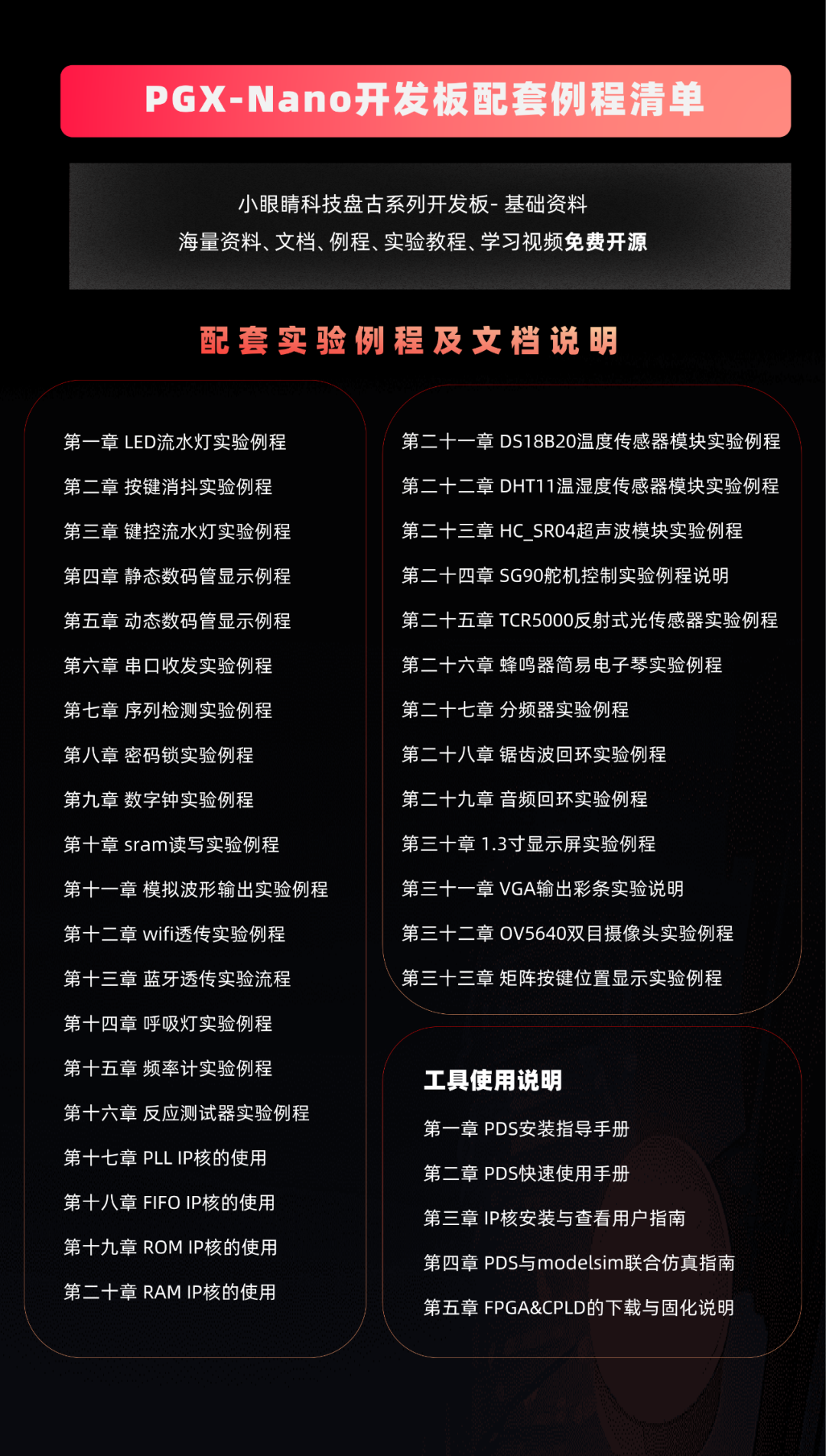

PGX_Nano配套教程通过“看得见、摸得着” 的硬件交互,建立从“比特到系统” 的工程思维。它不仅是验证理论的手段,更是培养复杂系统设计能力的核心途径。对于初学者,从点亮一颗LED开始积累底层经验;对于进阶开发者,通过外设实验探索FPGA在高速数据采集、数据处理等领域的应用,最终实现从“模块设计者” 到 “系统架构师” 的能力跃迁。

-

pcb钻孔偏孔了怎么办?2023-11-22 6480

-

电机过热怎么办?2023-11-01 1749

-

I2C接口进入Busy状态不能退出怎么办2023-08-02 1402

-

JTAG不能调试了老是出错怎么办2020-07-19 2775

-

linux无法识别U盘怎么办2020-05-19 17835

-

Xilinx FPGA JTAG接口转换成USB接口的方法2020-01-24 19680

-

二极管烧了怎么办2019-10-24 13477

-

JILNK调试时无法选择SW或JTAG怎么办2019-04-08 5206

-

JTAG接口定义2019-03-27 33444

-

电池换新无法可依怎么办2019-03-19 1923

-

如何确定fpga烧了?2017-11-21 6391

-

基于JTAG接口实现ARM的FPGA在线配置设计2010-02-09 3803

-

显示桌面没了怎么办2010-01-18 4166

-

诺基亚n70白屏怎么办2008-09-01 3770

全部0条评论

快来发表一下你的评论吧 !