ADF4383集成VCO的微波宽带频率合成器技术手册

描述

概述

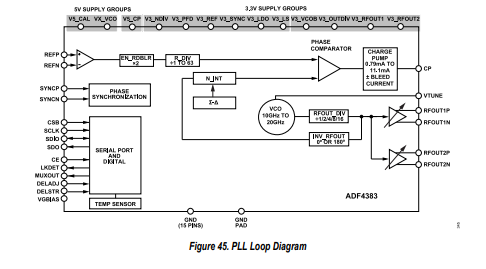

ADF4383 是一款高性能、超低抖动、小数 N 分频锁相环 (PLL),带有集成电压控制振荡器 (VCO),非常适合 5G 应用或数据转换器时钟应用的本地振荡器 (LO) 生成。高性能 PLL 具有 −239 dBc/Hz 的品质因数、低 1/f 噪声和整数模式下 625 MHz 的高 PFD 频率,可实现超低带内噪声和综合抖动。ADF4383 可产生 10 GHz 至 20 GHz 基本倍频范围内的频率,从而无需使用次谐波滤波器。ADF4383 上的输出分频器可产生从 625 MHz 至 20 GHz 的完整输出频率范围。

对于多数据转换器时钟应用,ADF4383 通过在 PLL 反馈环路中包含输出分频器,自动将其输出与输入参考边沿对齐。对于需要确定性延迟或延迟调整功能的应用,提供分辨率 <1 ps 的可编程输出延迟参考。通过参考跨多个设备和整个温度的输出延迟匹配,可以实现可预测且精确的多芯片对齐。

ADF4383 框图十分简单,通过简化的串行外设接口 (SPI) 寄存器映射、外部 SYNC 输入以及整数和小数模式下可重复的多芯片对齐,可以缩短开发时间。

数据表:*附件:ADF4383集成VCO的微波宽带频率合成器技术手册.pdf

应用

- 高性能数据转换器时钟

- 无线基础设施(MC-GSM、5G、6G)

- 测试和测量

特性

- 基本 VCO 频率范围:10 GHz 至 20 GHz

- 与 [ADF4382]相比,VCO 相位噪声改善高达 3 dB

- 20 GHz 时的积分 RMS 抖动 = 18 fs(积分带宽:100 Hz 至 100 MHz)

- 20 GHz 时的积分 RMS 抖动 = 31 fs(ADC SNR 方法)

- VCO 快速校准时间:<2 μs

- VCO 自动校准时间:<100 μs

- 相位本底噪声:20 GHz 时为 −156 dBc/Hz

- PLL 规格

- −239dBc/Hz:归一化带内相位噪声基底(整数模式)

- −287dBc/Hz:归一化 1/f 相位本底噪声

- 625 MHz 最大相位/频率检波器输入频率

- 4.5 GHz 参考输入频率

- 典型杂散 fPFD:−90 dBc

- 参考输出延迟规格

- 传播延迟温度系数:0.06 ps/°C

- 调整步长:<1ps

- 多芯片输出相位对齐

- 3.3V 和 5V 电源

- 支持 ADIsimPLL™ 环路滤波器设计工具

- 7 mm × 7 mm、48 端子 LGA

- 工作温度 −40°C 至 +105°C

框图

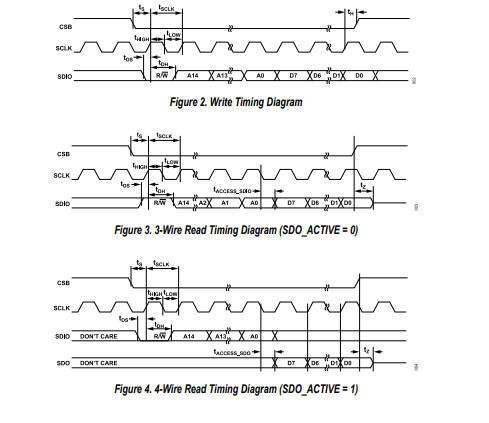

串行接口时序图

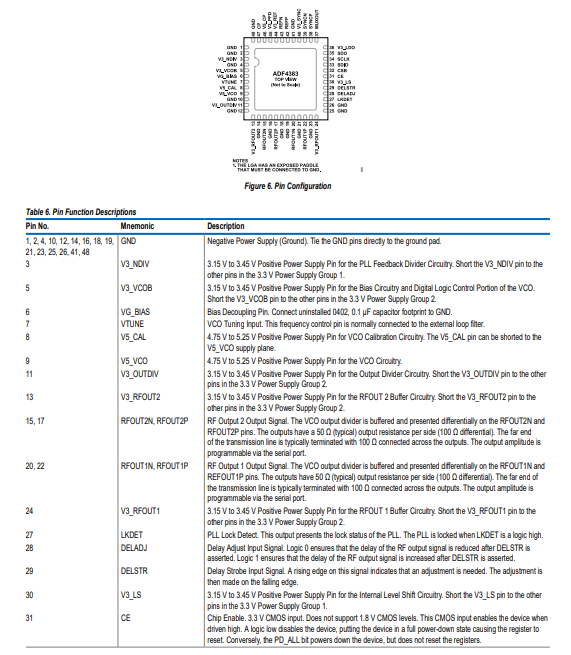

引脚配置描述

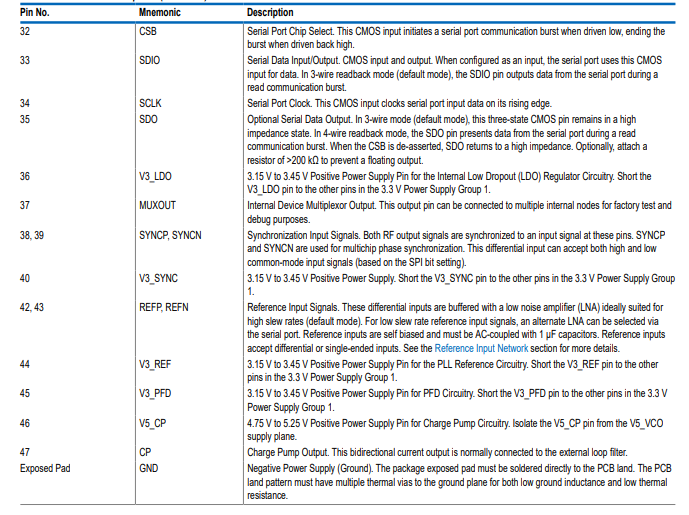

典型性能特征

工作原理

锁相环(PLL)是一种复杂的反馈系统,从概念上可视为一个频率乘法器。该系统将输入频率((REF_{IN}))与输出频率((RFOUT))进行比较,并将两者之间的相位和频率差转换为误差电压。此误差电压经滤波后,用于控制压控振荡器(VCO)的频率。VCO输出与输入参考频率之间的比率由反馈回路中的分频器设定。

PLL由几个关键部分组成:参考输入部分、鉴频鉴相器(PFD)、电荷泵、环路滤波器、VCO和反馈分频器。参考输入部分为PFD提供稳定的参考频率。PFD比较参考频率与反馈频率的相位和频率,并产生与两者差值成正比的输出。电荷泵将PFD的输出转换为电流,该电流由环路滤波器进行积分和滤波。滤波后的电压控制VCO的频率,VCO输出反馈至PFD,形成闭环系统。

在整数模式下工作时,反馈分频器将VCO输出除以整数N,N决定了输出频率与参考频率的比率。在分数模式下,反馈分频器采用更复杂的技术,实现分数N分频,从而能够产生更精细间隔的输出频率。

PLL的性能受多种因素影响,包括参考频率的稳定性、PFD的特性、电荷泵电流、环路滤波器的设计以及VCO的特性。优化这些参数对于实现低相位噪声、快速锁定时间和良好的杂散性能至关重要。

-

ADF4371微波宽带合成器:特性、应用与设计要点2026-04-20 71

-

ADF5611集成VCO的微波宽带频率合成器技术手册2025-04-27 1184

-

ADF4372带集成VCO的微波宽带频率合成器技术手册2025-04-25 1495

-

ADF5612集成VCO的微波宽带频率合成器技术手册2025-04-24 1323

-

ADF4377 微波宽带合成器和集成VCO数据表 ADI2023-10-11 313

-

ADF4368:微波宽带合成器和集成VCO数据表 ADI2023-10-10 385

-

ADF435微波宽带频率合成器资料分享2022-07-23 892

全部0条评论

快来发表一下你的评论吧 !