AD9081四通道16位12GSPS RFDAC和四通道12位4GSPS RFADC技术手册

描述

概述

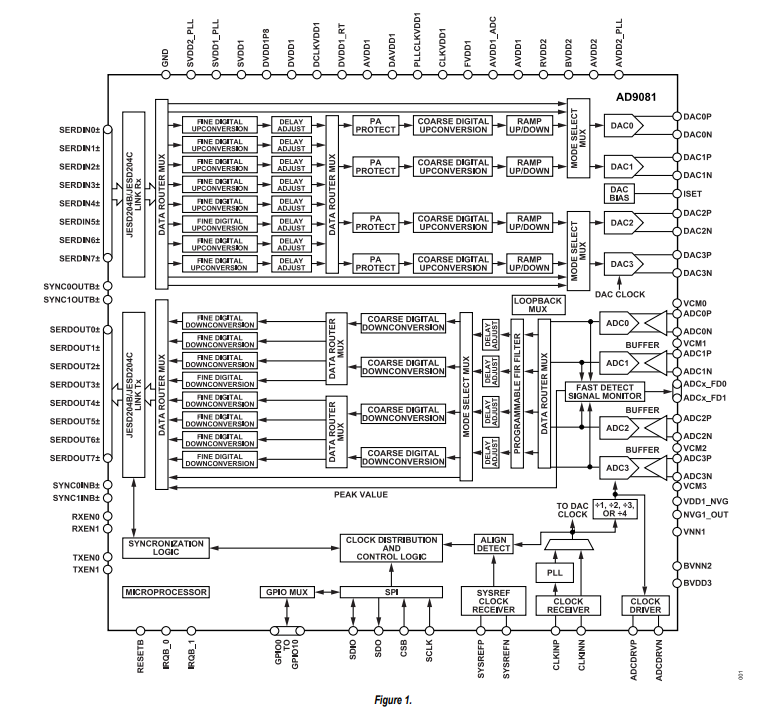

AD9081 混合信号前端(MxFE )是一款高度集成的套件,具有四个 16 位、12 GSPS 最大采样率、RF 数模转换器(DAC)内核,以及四个 12 位、4 GSPS 速率、RF 模数转换器(ADC)内核。AD9081 非常适合需要宽带 ADC 和 DAC 来处理具有宽瞬时带宽信号的应用。该套件具有八个发送和八个接收通道,支持 24.75 Gbps/通道 JESD204C 或 15.5 Gbps/通道 JESD204B 标准。该套件还具有片内时钟乘法器,以及直接针对 RF 应用的宽带或多频带数字信号处理(DSP)功能。可以绕过 DSP 数据路径,以允许转换器内核与 JESD204 数据收发器端口之间直接连接。该套件还具有针对相位阵列雷达系统和电子战应用的低延迟回送和跳频模式。提供两种型号的 AD9081。4D4AC 模型支持完整的瞬时通道带宽,而 4D4AB 模型通过自动配置 DSP,来限制启动时的瞬时带宽,从而支持每通道 600 MHz 的最大瞬时带宽。

数据表:*附件:AD9081四通道16位12GSPS RFDAC和四通道12位4GSPS RFADC技术手册.pdf

应用

- 无线通信基础设施

- 微波点对点、E 频段和 5G 毫米波

- 宽带通信系统

- DOCSIS 3.1 和 4.0 CMTS

- 相控阵雷达与电子战

- 电子测试和测量系统

特性

- 灵活的可重新配置通用平台设计

- 4 个DAC 和 4 个ADC(4D4A)

- 支持单频段、双频段和多频段

- 数据路径和 DSP 模块可完全绕过

- 1、2、3 和 4 的 DAC 与 ADC 采样率之比

- 具有多芯片同步功能的片内 PLL

- 片外 PLL 的外部 RFCLK 输入选项

- 最大 DAC 采样率高达 12 GSPS

- 使用 JESD204C 的最大数据速率高达 12 GSPS

- 可用的模拟带宽高达 8 GHz

- 最大 ADC 采样率高达 4 GSPS

- 使用 JESD204C 的最大数据速率高达 4 GSPS

- 7.5 GHz 模拟输入全功率带宽 (-3 dB)

- 4 GSPS,输入为 -2.7 GHz 时,ADC 交流性能为 -1 dBFS

- 满量程输入电压:1.4 V p-p

- 噪声密度:−147.5 dBFS/Hz

- 噪声指数:26.8 dB

- HD2:−67 dBFS

- HD3:−73 dBFS

- 最差的其他情况(HD2 和 HD3 除外):2.7 GHz 时,为 −79 dBFS

- 12 GSPS 时的 DAC 交流性能

- 满量程输出电流范围:6.43 mA 至 37.75 mA

- 双信号音 IMD3(每个音调 −7 dBFS):−78.9 dBc

- 3.7 GHz 时,NSD,单信号音:−155.1 dBc/Hz

- 3.7 GHz 时,SFDR,单信号音:−70 dBc

- SERDES JESD204B/JESD204C 接口,16 个通道,速率高达 24.75 Gbps

- 8 通道 JESD204B/C 变送器 (JTx) 和 8 通道 JESD204B/C 接收器 Rx (JRx)

- JESD204B 与最大 15.5 Gbps 的通道速率兼容

- JESD204C 与最大 24.75 Gbps 的通道速率兼容

- 支持实数或复数数字数据(8、12、16 或 24 位)

- 多种数字特性

- 可配置或可旁路的 DDC 和 DUC

- 8 个细调复数 DUC 和 4 个粗调复数 DUC

- 8 个细调复数 DDC 和 4 个粗调复数 DDC

- 每个 DUC 或 DDC 48 位 NCO

- 可编程 192 抽头 PFIR 滤波器,用于接收均衡

- 支持通过 GPIO 加载的 4 种不同的配置文件设置

- 每个数据路径的可编程延迟

- 接收 AGC 支持

- 用于快速 AGC 控制,具有低延迟的快速检测

- 用于缓慢 AGC 控制的信号监控器

- 发射 DPD 支持

- 细调 DUC 通道增益控制和延迟调整

- DPD 观察路径的粗调 DDC 延迟调整

- 可配置或可旁路的 DDC 和 DUC

- 辅助特性

- 快速跳频和直接数字频率合成器(DDS)

- 低延迟环回模式(接收数据路径数据可以路由到发送数据路径)

- 具有可选分频比的 ADC 时钟驱动器

- 功率放大器下游保护电路

- 片内温度监控单元

- 灵活的 GPIO 引脚

- TDD 省电选项和共享 ADC

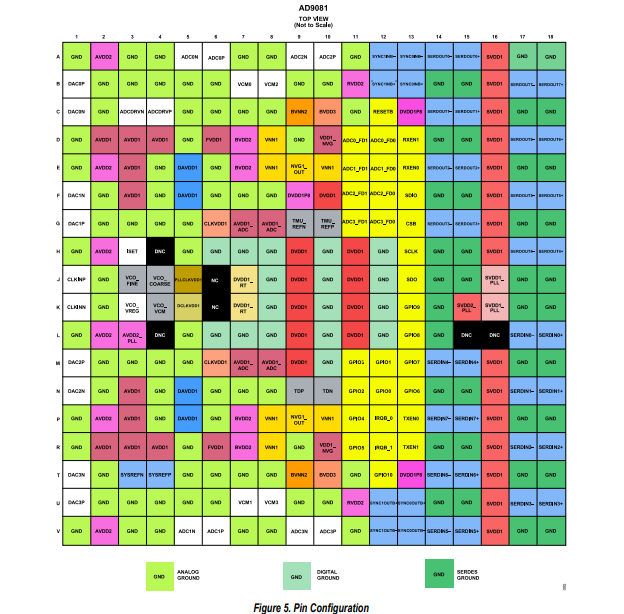

- 15毫米××15毫米、324 球 BGA,间距 0.8 毫米

框图

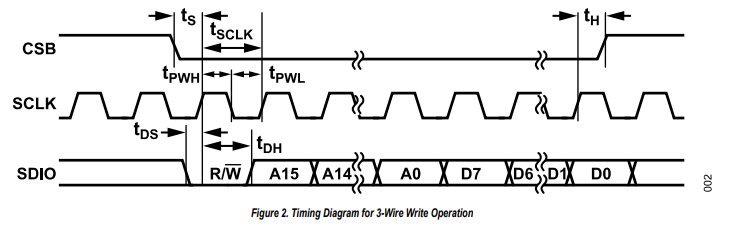

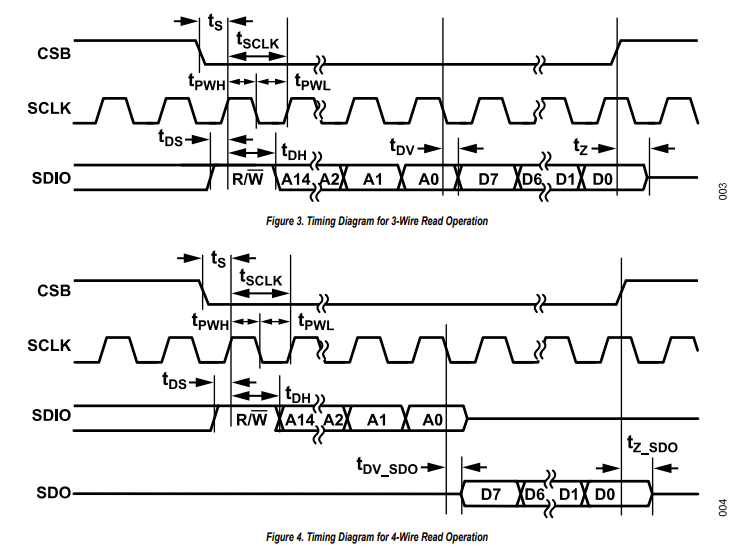

时序图

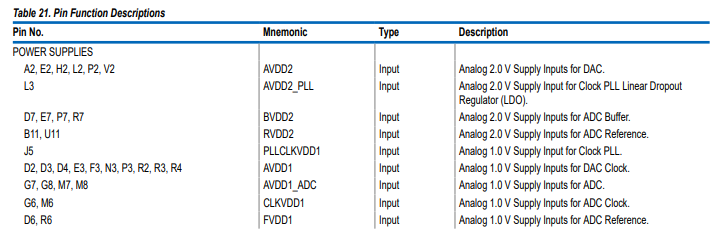

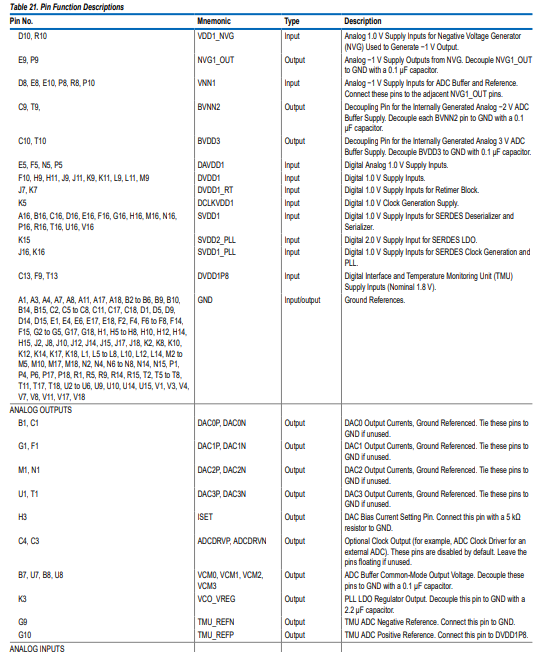

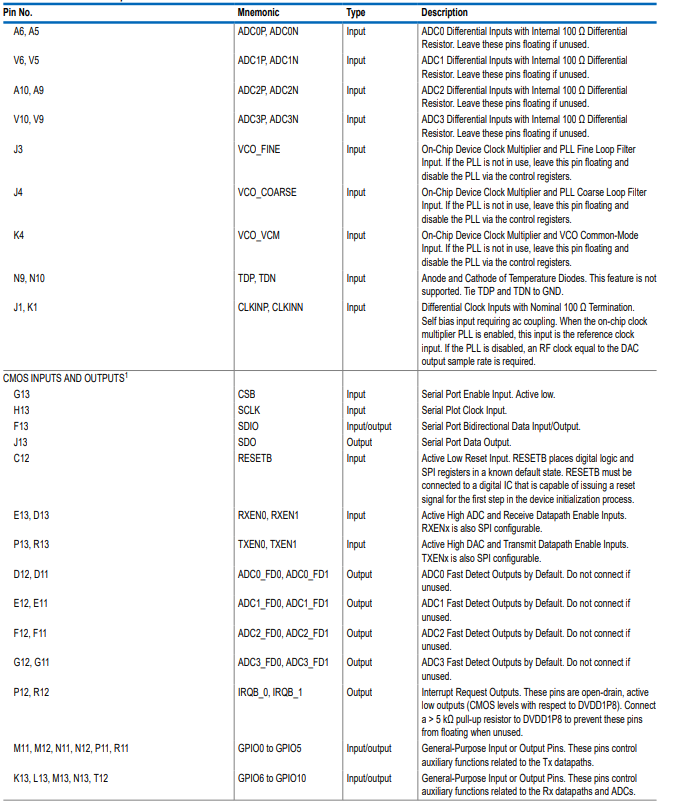

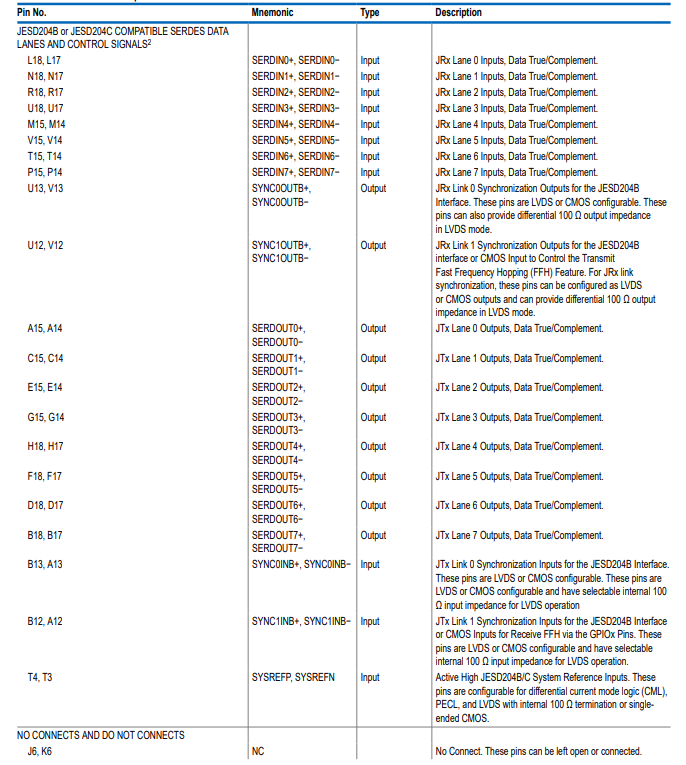

引脚配置和功能描述

工作原理

AD9081是一款高度集成的28纳米射频混合信号前端(MxFe),具有四个16位、12 GSPS的数模转换器(DAC)内核和四个12位、4 GSPS的模数转换器(ADC)内核(见图1)。DAC内核基于电流分段架构,提供具有可调输出范围(6.43 mV至37.5 mV)的互补差分输出。ADC基于比例插值架构,可抑制残余交织杂散产物,达到100 dB的高线性度。100 Ω差分缓冲器具有过驱动保护功能,用于将ADC内核与射频ADC电源隔离。片上时钟乘法器可用于合成射频DAC和ADC时钟。或者,也可以接收外部时钟。

灵活的发射和接收数字信号处理(DSP)路径可对采样信号进行采样,以获得所需的中频(IF)和射频(RF)频率,并有效降低数据速率,同时满足带宽要求。多通道数据路径使宽带数据传输成为可能,支持多达八个独特的射频频段。发射和接收DSP路径对称,由四个数字下变频(DDC)和数字上变频(DUC)模块以及主数据路径中的抽取滤波器和内插滤波器组成。每个DUC和DDC模块在多通道数据路径中具有多个内插或抽取级以及一个48位数控振荡器(NCO),用于整数或小数模式的操作。NCO可在粗调DUC和DDC模块中支持快速跳频、相干操作,并可使用GPIO控制DUC、DDC模块和数据路径,使其能够完全旁路以实现奈奎斯特操作。

各种辅助DSP功能有助于改进系统集成。数据路径包括可调延迟线,以补偿外部可能出现的通道延迟路径失配。发射数据路径包括数字增益控制、精细延迟调整和功率放大器保护,以简化多频段发射机中的数字预失真(DPD)集成。接收数据路径包括一个灵活的可编程192抽头有限脉冲响应(FIR)滤波器,该滤波器可分配给一个或多个ADC进行接收均衡。可以使用GPIO选择四种不同的滤波器配置文件。接收数据路径还包括慢速信号检测功能,以支持自动增益控制(AGC)。数据路径还包括有助于降低数据速率的特性,适用于时分双工(TDD)应用。所有辅助DSP功能都可以完全旁路。

AD9081还支持在接收和发射数据路径之间进行低延迟数字环回,以旁路JESD204。数据路径的数据格式可以是实数或复数(IQ),根据JESD204B或JESD204C,可选择8位、12位、16位和24位分辨率。

一个16通道JESD204收发器端口可支持接收和发射数据路径的高数据速率。八条SERDES通道指定用于发射数据路径,而其他八条通道指定用于接收数据路径。收发器端口支持JESD204C高达24.75 Gbps或JESD204B高达15.5 Gbps的通道速率。JESD204数据链路层高度灵活,允许调整通道计数(或速率),以支持目标链路长度。外部对齐信号(SYSREF)可用于保证确定性延迟、相位对齐,并用于多芯片同步。

片上热管理单元(TMU)可用于测量芯片温度,作为热管理解决方案的一部分,以确保系统运行期间具有更好的热稳定性。

-

深度解析AD9209:12位、4 GSPS四通道ADC的卓越性能与应用前景2026-03-27 284

-

Analog Devices Inc. AD9209四通道12位4GSPS ADC数据手册2025-06-20 1165

-

AD9082四通道16位12GSPS RFDAC和双通道12位6GSPS RFADC技术手册2025-04-28 1805

-

AD9081四通道、16位、12 GSPS RF DAC和四通道、12位、4 GSPS RF ADC数据表2024-07-31 1004

-

ADC09xJ1300四通道/双通道/单通道1.3GSPS 9位模数转换器(ADC)数据表2024-07-15 541

-

ADC12QJ1600-SP具有JESD204C接口的四通道1.6GSPS 12位模数转换器(ADC)数据2024-07-12 465

-

DAC3484四通道16位1.25GSPS数模转换器(DAC)数据表2024-06-20 676

-

AD664:单片12位四通道DAC数据表2021-05-27 1363

-

AD9081:MxFE®四路16位12 GSPS RF DAC和四路12位4 GSPS RF ADC初步数据表2021-05-08 1007

-

AD9148是支持四通道,请问如果四个通道同时用,最高支持4GSPS,还是四个通道总共1GSPS?2018-08-08 1890

-

ADI推出四通道、2.4 GSPS、16位数DAC AD91542015-03-26 6395

-

具有内部基准的四通道12 位/10 位/8 位轨至轨I2C2009-12-10 1330

全部0条评论

快来发表一下你的评论吧 !