AD9082四通道16位12GSPS RFDAC和双通道12位6GSPS RFADC技术手册

描述

概述

混合信号前端(MxFE ) 是一款高度集成的器件,搭载16位、12 GSPS最大采样速率的RF数模转换器(DAC)内核,以及12位、6 GSPS采样速率的RF模数转换器(ADC)内核。AD9082支持4个发射器通道和2个接收器通道。AD9082非常适合需要使用宽带ADC和DAC来处理具有宽瞬时带宽的信号的应用。该器件具有16通道、16.22 Gbps JESD204C或15.5 Gbps JESD204B数据收发器端口、片内时钟倍频器和数字信号处理(DSP)功能,适合宽带或多频段直接至RF应用。AD9082还具有旁路模式,允许ADC和/或DAC内核的全宽带功能旁路DSP数据路径。此器件还具有低延迟回送和跳频模式,适用于相控阵雷达系统和电子战应用。

数据表:*附件:AD9082四通道16位12GSPS RFDAC和双通道12位6GSPS RFADC技术手册.pdf

应用

- 无线通信基础设施

- 微波点对点、E频段和5G毫米波

- 宽带通信系统

- DOCSIS 3.1和4.0 CMTS

- 相控阵雷达和电子战

- 电子测试与测量系统

特性

- 灵活、可重新配置的通用平台设计

- 4个DAC和2个ADC(4D2A)

- 支持单通道、双通道、四通道

- 最大DAC/ADC采样速率高达12 GSPS/6 GSPS

- DAC至ADC的采样速率比为1、2、3和4

- ADC和DAC数据路径旁路选项

- 模拟带宽高达8 GHz

- 满量程输出电流范围,交流耦合:7 mA至40 mA

- 片内PLL,支持多芯片同步

- 外部RFCLK输入选项

- 6 GSPS时的ADC交流性能

- 满量程输入电压:1.475 V p-p

- 满量程正弦波输入功率:4.4 dBm

- 噪声密度:−153 dBFS/Hz

- 噪声系数:25.3 dB

- HD2:−65.2 dBFS(2.7 GHz)

- HD3:−70.8 dBFS(2.7 GHz)

- 最差其它谐波(不包括HD2和HD3):−68.5 dBFS(2.7 GHz)

- DAC交流性能(3.7 GHz输出)

- 双信号音IMD3(每种信号音−7 dBFS):−78.9 dBc

- NSD,单音,f

DAC= 12 GSPS: −155.1 dBc/Hz - SFDR,单音,f

DAC= 12 GSPS: −70 dBc

- 多种数字功能

- 支持真正或复杂的数字数据(8位、12位、16位或24位)

- 可选择的内插和抽选滤波器

- 可配置的DDC和DUC

- 8个精调复数DUC和4个粗调复数DUC

- 8个精调复数DDC和4个粗调复数DDC

- 每个DUC/DDC 48位NCO

- 旁路精调和粗调DUC/DDC的选项

- 可编程的192个抽头PFIR滤波器,用于实现接收均衡

- 支持通过GPIO加载的4种不同的配置文件设置

- 每条数据路径的可编程延迟

- 接收AGC支持

- 快速检测,低延迟,用于实现快速的AGC控制

- 检测缓慢AGC控制的信号监测器

- 专用的AGC支持引脚

- 发送DPD支持

- 微调DUC通道增益控制和延迟调节

- DPD观测路径的粗调DDC延迟调节

- 辅助功能

- 快速跳频

- 直接数字频率合成器(DDS)

- 低延迟数字回送模式(ADC至DAC)

- 具有可选分频比的ADC时钟驱动器

- 功率放大器下游保护电路

- 片内温度监控单元

- 灵活的GPIOx引脚

- TDD省电选项

- SERDES JESD204B/JESD204C接口,16个通道高达16.22 Gbps

- 每个DAC和ADC 8个通道

- JESD204B兼容最大15.5 Gbps的通道速率

- JESD204C兼容最大16.22 Gbps的通道速率

- 样本和位重复模式,用于通道速率匹配

- 总功耗:11.45 W(典型值)

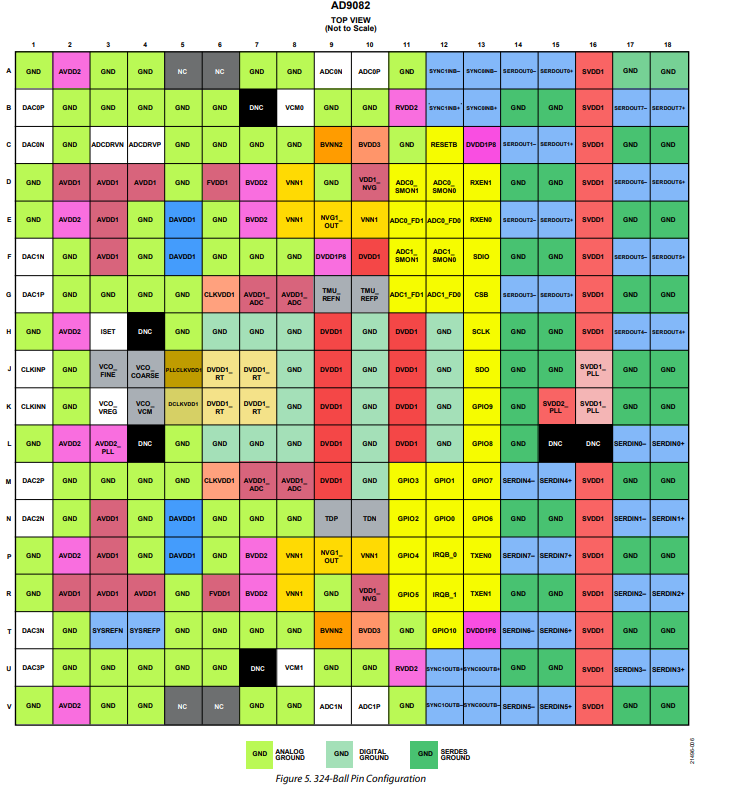

- 15 mm × 15 mm,324引脚BGA,0.8 mm间距

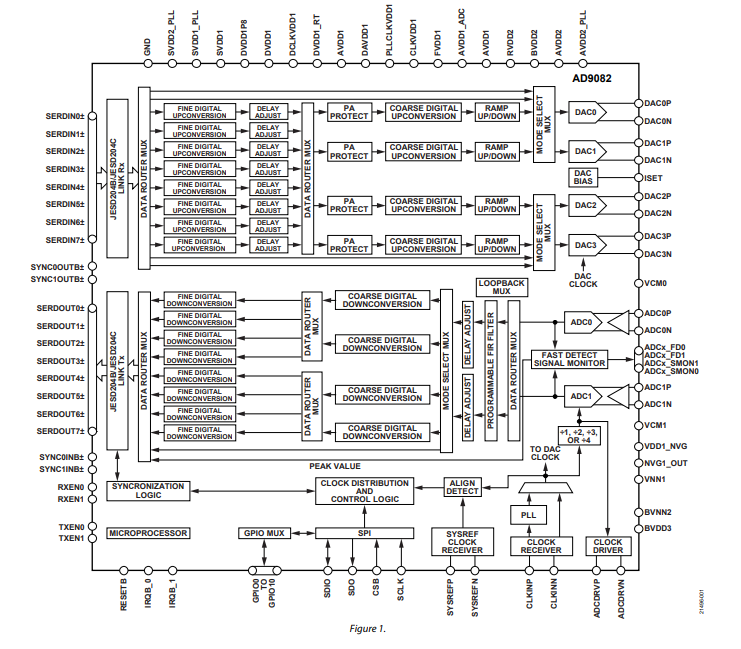

框图

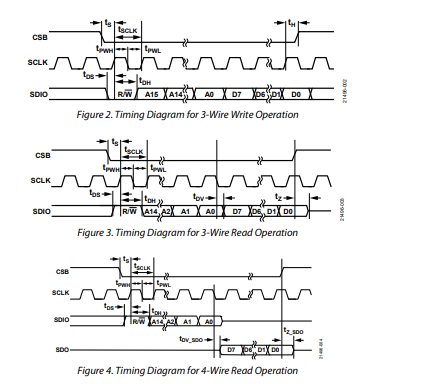

时序图

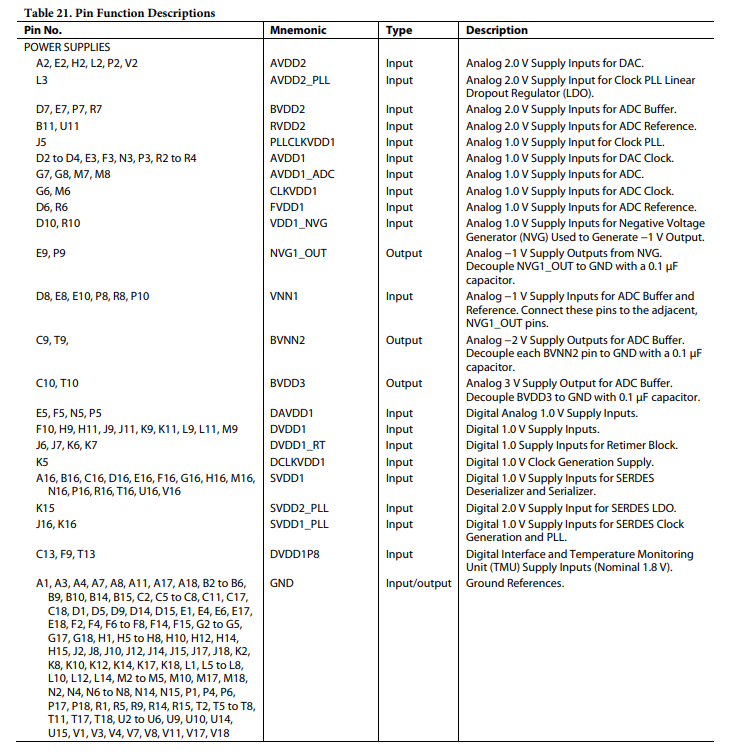

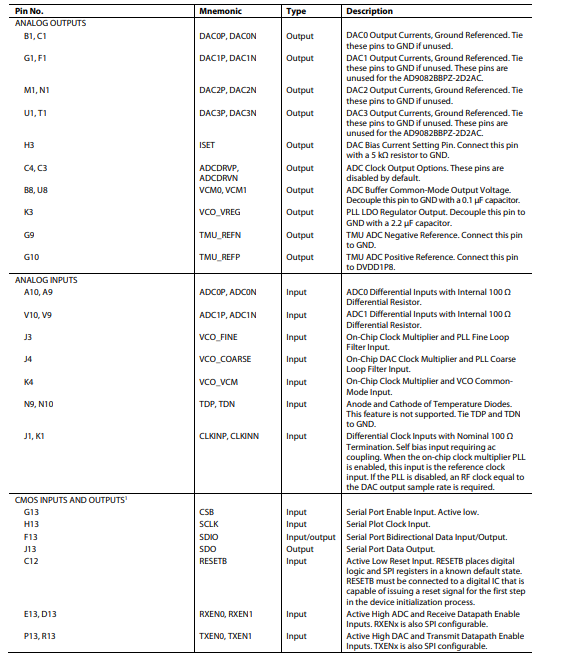

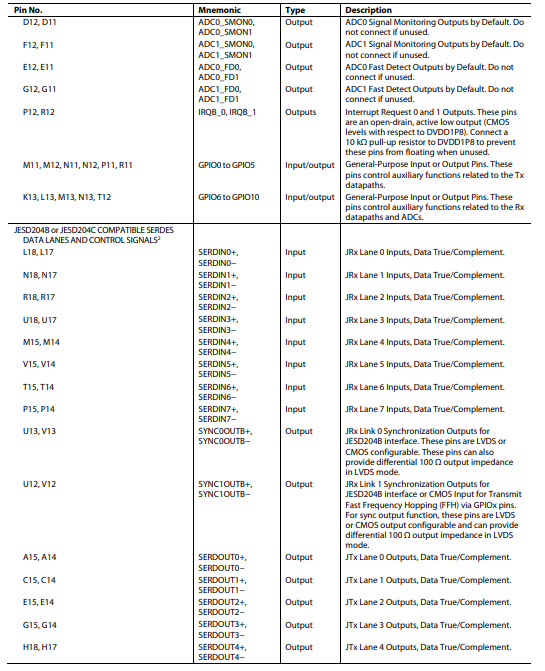

引脚配置描述

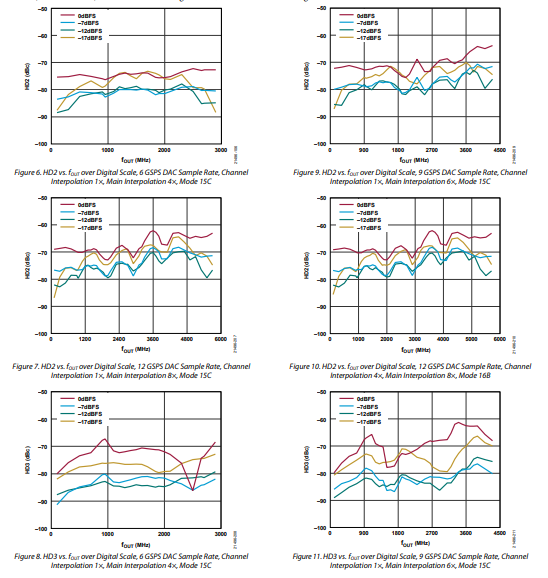

典型性能特征

数据曲线代表所有输出的平均性能,谐波和杂散落在第一奈奎斯特区(< fuc/2)。所有SFDR、IMD3和NSD数据均在实验室评估板上测量。相位噪声和邻道泄漏率(ACL)的所有数据。r)在AD9081-FMCA-EBZ或AD9082-FMCA-EBZ客户评估板上测量。有关JESD204B和JESD204C模式配置的更多信息,请参见UG-1578用户指南。

工作原理

AD9082是一款高度集成的28纳米射频混合信号前端(MxFe),具备四个16位、12 GSPS的数模转换器(DAC)内核以及两个12位、6 GSPS的模数转换器(ADC)内核(见图1)。DAC内核基于电流分段架构,提供互补差分电流输出,其输出范围可在6.43 mA至37.75 mA之间调节。ADC采用比例插值架构,可抑制残余杂散产物,实现100 Ω差分缓冲器的高线性度。该缓冲器具备过驱动保护功能,用于将ADC内核与射频ADC电源隔离。片上时钟乘法器可用于合成射频DAC和ADC时钟,也可接收外部时钟。

灵活的发射和接收数字信号处理(DSP)路径可对所需的中频(IF)或射频(RF)信号进行上下采样,以有效管理与带宽要求相符的数据速率。发射和接收的DSP路径对称,由主数据路径中的四个数字上变频(DUC)和数字下变频(DDC)模块组成,每个DUC和DDC模块均带有抽取滤波器和内插滤波器。每条通道的数据路径包含一个48位数控振荡器(NCO),可用于整数或小数模式操作。通道数据路径可实现多频段应用,支持多达八个射频频段。DUC和DDC模块均可旁路,并提供灵活的内插和抽取功能。每个模块还支持相干跳频。

在发射和接收数据路径中还包含额外的DSP功能,以助力系统集成。两条路径均设有可调延迟线,用于补偿器件外部通道延迟路径可能出现的失配情况。发射数据路径集成了数字增益控制、精细延迟调整和功率放大器保护功能,便于在多频段发射机中实现数字预失真(DPD)。接收数据路径配备一个灵活的可编程192抽头有限脉冲响应(FIR)滤波器,可分配给一个或多个ADC用于接收均衡。可通过GPIO引脚选择四种不同的滤波器配置文件。接收数据路径还具备慢速信号检测功能,支持自动增益控制(AGC)。发射和接收的数据格式可以是实数或复数(IQ),分辨率可选8位、12位、16位和24位,符合JESD204B或JESD204C标准。AD9082还支持JESD204模式下的低延迟数字环回功能,可绕过发射和接收DSP路径,实现奈奎斯特操作。

该器件还支持通过GPIO引脚实现快速跳频,并具备低延迟数字环回功能。片上热管理单元(TMU)可用作热管理方案的一部分,用于监测温度。同时还提供了功率检测功能,适用于时分双工(TDD)应用。

一个16通道JESD204收发器端口,可支持接收和发射数据路径的高数据传输速率。八条SERDES通道专用于发射数据路径,另外八条用于接收数据路径,收发器端口可根据JESD204C标准,支持高达24.75 Gbps的数据速率,或根据JESD204B标准,支持高达15.5 Gbps的数据速率。JESD204数据链路层高度灵活,可根据目标传输速率优化通道数量(或速率)。内部同步功能可确保确定性延迟和相位校准,也可通过外部对齐信号(SYSREF)实现多芯片同步。

-

ADC12DJ1600-Q1 汽车、2通道、12位、1.6GSPS ADC技术手册2025-11-03 884

-

ADC12DJ1600 双通道、12位、1.6GSPS ADC技术手册2025-10-31 1403

-

AD9084 Apollo MxFE四通道、16位、28 GSPS RF DAC和四通道、12位、20 GSPS RF ADC技术手册2025-04-28 2188

-

AD9084 MxFE 四通道、16位、28 GSPS RF DAC和四通道、12位、20 GSPS RF ADC技术手册2025-04-18 2517

-

AD9081四通道、16位、12 GSPS RF DAC和四通道、12位、4 GSPS RF ADC数据表2024-07-31 1004

-

ADC09xJ1300四通道/双通道/单通道1.3GSPS 9位模数转换器(ADC)数据表2024-07-15 541

-

ADC12QJ1600-SEP四通道1.6GSPS 12位模数转换器(ADC)数据表2024-07-12 480

-

AD9082: MxFE® Quad, 16-Bit, 12 GSPS RF DAC and Dual, 12-Bit, 6 GSPS RF ADC Data Sheet AD9082: MxFE® Quad, 16-Bit, 12 GSPS RF DAC and Dual, 12023-10-17 135

-

高度集成混合信号前端AD9082的功能特点及应用范围2020-11-30 2806

-

RF数模转换器AD9082的性能特点及应用范围2020-11-28 2095

-

ADI推出四通道、2.4 GSPS、16位数DAC AD91542015-03-26 6395

全部0条评论

快来发表一下你的评论吧 !