AD6674 385MHz BW IF分集接收机技术手册

描述

概述

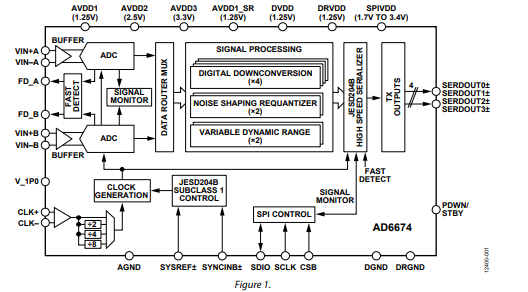

AD6674是一款385 MHz带宽混合信号中频(IF)接收器。内置双通道、14位1.0 GSPS/750 MSPS/500 MSPS模数转换器(ADC)和各种数字信号算法模块,包括四个宽带DDC、一个NSR和VDR监控。它具有片内缓冲器和采样保持电路,专门针对低功耗、小尺寸和易用性而设计。该产品设计支持通信应用,能够实现高达2 GHz的宽带宽模拟信号采样。AD6674针对宽输入带宽、高采样速率、出色的线性度和小封装低功耗而优化。

这款双通道ADC内核采用多级、差分流水线架构,并集成了输出纠错逻辑。每个ADC均具有宽带宽输入,支持用户可选的各种输入范围。集成基准电压源可简化设计考量。

数据表:*附件:AD6674 385MHz BW IF分集接收机技术手册.pdf

应用

- 分集多频段、多模数字接收器 3G/4G、TD-SCDMA、W-CDMA、GSM、LTE、LTE-A

- DOCSIS 3.0 CMTS上游接收路径

- HFC 数字反向路径接收机

特性

- JESD204B(子类1)编码串行数字输出

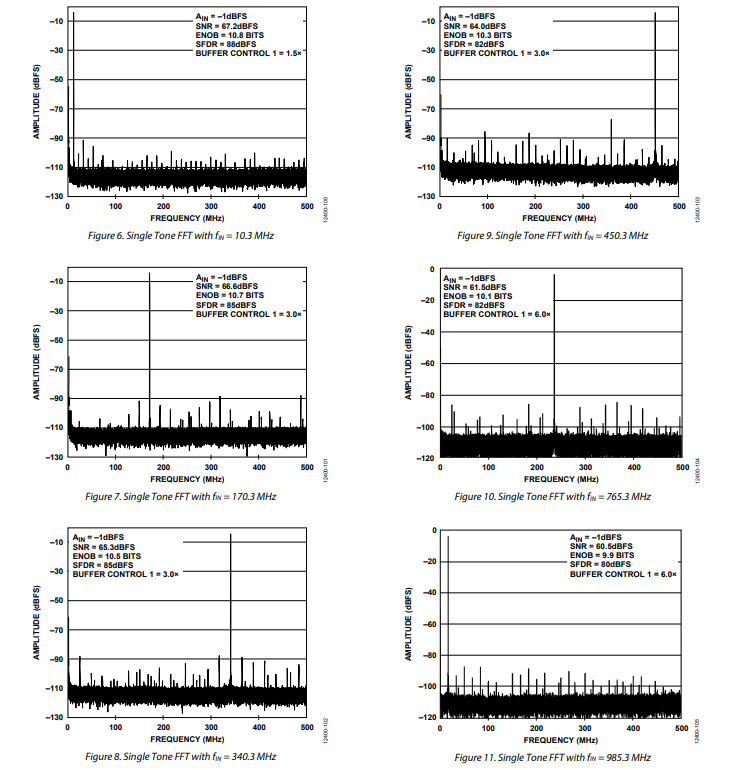

- 带内SFDR = 83 dBFS (340 MHz时,750 MSPS)

- 带内SNR = 66.7 dBFS (340 MHz时,750 MSPS)

- 750 MSPS 时每通道总功耗:1.4 W(默认设置)

- 噪声密度 = -153 dBFS/Hz (750 MSPS)

- 1.25 V、2.5 V和3.3 V 直流电源供电

- 灵活的输入范围

- AD6674-750和AD6674-1000

1.46 V p-p至1.94 V p-p(标称值1.70 V p-p) - AD6674-500

1.46 V p-p至2.06 V p-p(标称值2.06 V p-p)

- AD6674-750和AD6674-1000

- 95 dB通道隔离/串扰

- 幅度检测位支持实现高效自动增益控制(AGC)

- 噪声整形再量化器(NSR)选项支持主接收机功能

- 可变动态范围(VDR)选项支持数字预失真(DPD)功能

- 每通道集成 2 个宽带数字处理器

- 12 位数控振荡器(NCO),最多级联 4 个半带滤波器

- 差分时钟输入

- 整数时钟分频值:1、2、4或8

- 节能的关断模式

- 灵活的 JESD204B 通道配置

- 小信号扰动

框图

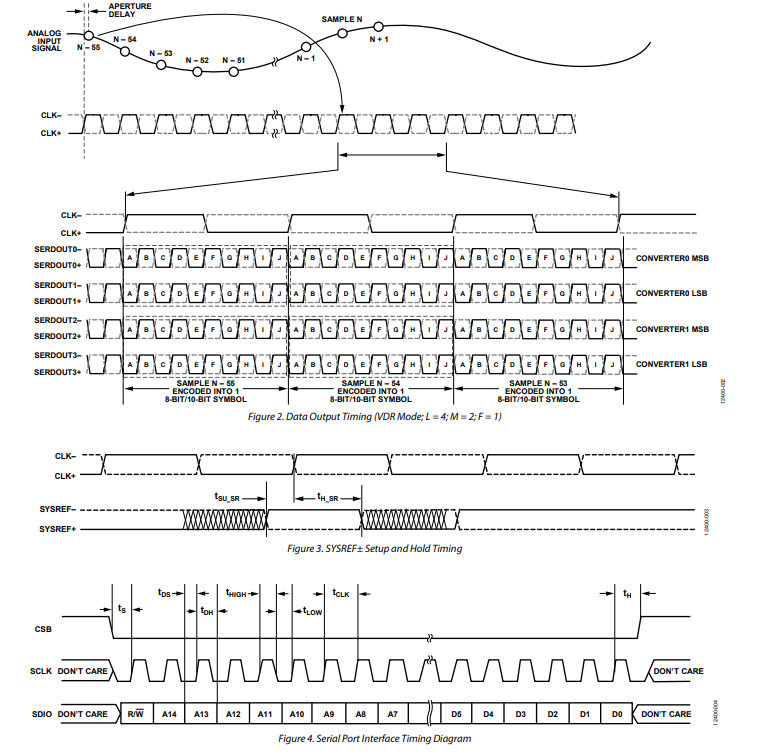

时序图

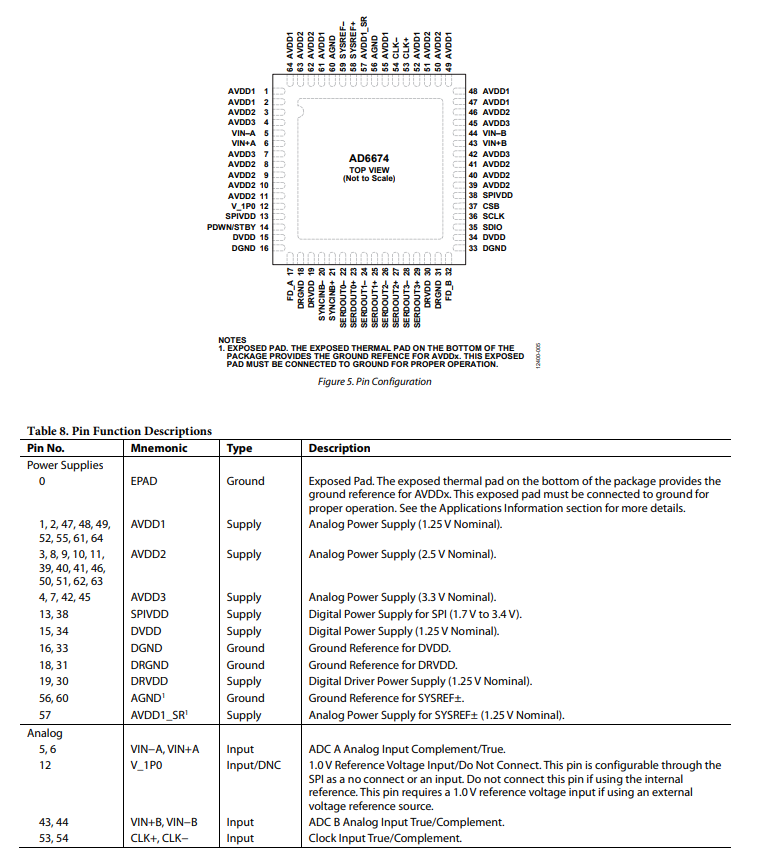

引脚配置描述

典型性能特征

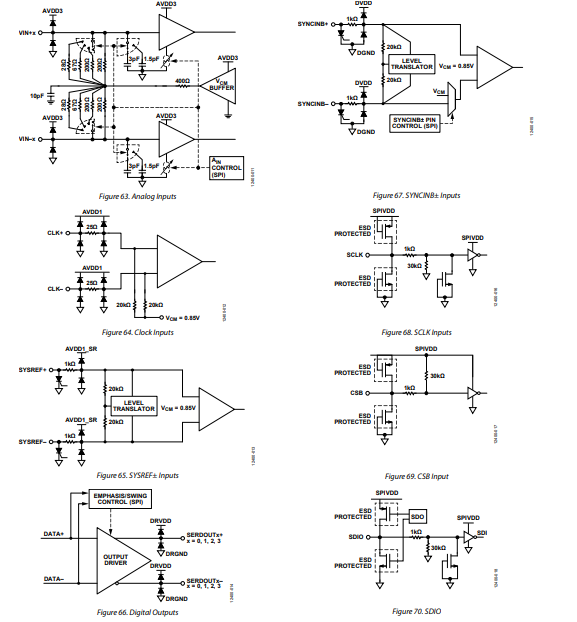

等效电路

工作原理

AD6674有两个模拟输入通道和两个JESD204B输出通道。AD6674旨在对高达2 GHz的宽带宽模拟信号进行采样。其优化设计用于实现宽带宽、高采样速率、出色的线性度以及小封装低功耗。

双ADC内核采用差分流水线架构,集成输出误差校正逻辑。每个ADC具有宽带宽输入,支持多种用户可选输入范围。集成的电压基准简化了设计考量。

AD6674具备多项功能,可简化通信接收器中的自动增益控制(AGC)功能。可编程阈值检测器能够监测ADC数据输出流的功率。当检测到的功率超过可编程阈值(通过寄存器0x24B设置)时,快速检测指示灯将变高。由于该阈值指示灯具有低延迟特性,用户可以快速降低系统增益,以避免ADC输入出现过载情况。

超速率1模式下的JESD204B高速串行输出数据速率可配置为单通道(L = 1)和双通道(L = 2),具体取决于采样速率和抽取率。通过SYSREF™和SYNCIN™输入引脚支持多路复用和设备间同步。

ADC架构

该架构采用输入缓冲伪差分ADC。输入缓冲器旨在提供一个与模拟输入信号相匹配的终端阻抗。这种终端连接可以通过使用SPDT来切换驱动/放大器的电源实现。图43展示了输入缓冲器的设置。为实现高线性度、低噪声和低功耗,对终端进行了优化。输入缓冲器具有高输入阻抗(可降低驱动源的负载),并从ADC的最终量化级获取反馈。反馈路径中的延迟有助于伪差分电路在采样瞬间像连续时间运算放大器一样工作。在时钟上升沿进行采样。

模拟输入注意事项

AD6674的模拟输入为差分信号。内部共模电压为2.05 V。时钟信号交替切换输入电路,在采样模式和保持模式之间切换。当输入电路切换到采样模式时,它会在半个时钟周期内对输入电容器进行采样和设置。采样保持电路中的每个电容器都有一个低阻抗驱动源。此外,可在输入的每个部分放置低Q值电感或铁氧体磁珠,以降低模拟输入的高差分电容,从而实现宽输入带宽。使用低Q值电感或铁氧体磁珠会在驱动源与转换器输入端之间引入寄生极点。寄生极点会产生一个单端等效电容,使输入与无源网络分离。这种未端接的低通滤波器会限制输入带宽,从而影响性能。有关详细信息,请参考《AN - 742:应用笔记,电压反馈运算放大器》,编号为AN - 742,出版于2005年4月,可在analog.com网站获取。一般来说,进行精密设计时,需使源阻抗匹配戴维南等效值,该等效值是通过对模拟输入的公共模式设置进行建模得出的。内部基准缓冲器会产生差分基准,从而确定ADC内核的比例。

通过设置ADC的最大差分配置,可实现最高SNR性能。在共模电压为1.9 V的情况下,AD6674 - 1000的满量程峰值 - 峰值范围为1.46 V p - p至2.06 V p - p,而AD6674 - 500的默认值为1.70 V p - p,额定值为2.06 V p - p。

不同输入配置

有多种方法可优化AD6674的性能,包括有源和无源方式。然而,最佳性能是通过有源方式实现的。

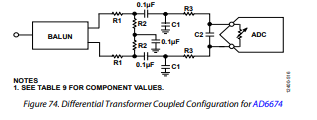

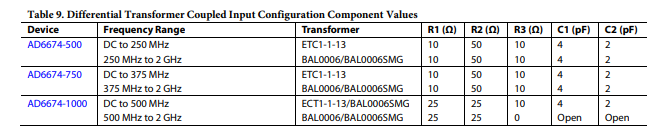

对于需要SNR和SFDR的应用,建议使用变压器耦合和共模输入配置(见图74和表9),因为这种配置可实现最佳性能,且不会影响AD6674的真实性能。

为了对混叠频率进行镜像处理,建议使用双巴伦(见图75和表9)。对于接近或高于AD6674奈奎斯特频率的频率,建议使用双巴伦,以去除前端无源元件,确保宽带宽工作(见图74和表9)。

-

请问AD6674的VDR功能有什么好处?2018-12-19 3470

-

RAKE接收机与分集接收2010-10-16 912

-

385MHz带宽中频分集接收机2017-06-06 1320

-

RAKE接收机的分集接收原理2017-11-13 19421

-

AD6674 385 MHz BW IF分集接收机2019-02-22 1022

-

AD6649: 中频分集接收机2021-03-21 1037

-

AD9680/AD6674 IBIS型号2021-03-24 827

-

评估AD6679中频分集接收机2021-05-09 2983

-

AD6653:中频分集接收机数据表2021-05-10 827

-

评估AD6674中频分集接收机2021-05-13 2189

-

AD6674德尔福型号2021-06-04 732

-

AD9680 AD6674 IBIS型号2021-06-06 803

-

AD6650分集中频至基带GSM/EDGE窄带接收机技术手册2025-04-28 1287

-

AD6674:高性能385 MHz带宽IF多样性接收器的技术剖析2026-03-30 512

-

AD6674:高性能中频分集接收机的卓越之选2026-05-23 58

全部0条评论

快来发表一下你的评论吧 !