AD6676宽带中频接收机子系统技术手册

描述

概述

AD6676是一款高度集成的中频子系统,可数字化高达160 MHz的射频(RF)频段,并且此频段在70 MHz至450 MHz中频(IF)范围内为宽度居中。 与传统奈奎斯特IF采样ADC不同,AD6676依靠具有高过采样率的可调谐带通Σ-Δ型ADC,无需特定频段的IF SAW滤波器和增益级,极大简化宽带无线电接收机架构。 片内正交数字下变频后接可选抽取滤波器,可将复数的数据速率降低至62.5 MSPS至266.7 MSPS范围内便于管理的速率。 16位复数输出数据通过单通道或双通道JESD204B接口传输至主机,支持的线路速率高达5.333 Gbps。

数据表:*附件:AD6676宽带中频接收机子系统技术手册.pdf

应用

- 多模、宽带蜂窝基础设施设备

- 点对点微波设备

- 仪器仪表

- 频谱分析仪和通信分析仪

- 软件定义无线电

特性

- 高瞬时动态范围

- 噪声系数(NF)低至13 dB

- 噪声频谱密度(NSD)低至−159 dBFS/Hz

- IIP3高达36.9 dBm,杂散音低于−99 dBFS

- 可调谐带通Σ-Δ型模数转换器(ADC)

- 信号带宽:20 MHz至160 MHz

- 中频中心频率:70 MHz至450 MHz

- 可配置输入满量程电平:−2 dBm至−14 dBm

- 易于驱动的阻性中频输入

- 1 dB增益平坦度,带外峰化低于0.5 dB

- 混叠抑制大于50 dB

- 2.0 GSPS至3.2 GSPS ADC时钟速率

- 片内PLL时钟倍频器

- 16位I/Q速率高达266 MSPS

- 片内数字信号处理

- NCO和正交数字下变频器(QDDC)

- 可选抽取系数:12、16、24和32

- 支持自动增益控制(AGC)

- 片内衰减器范围为27 dB、步进为1 dB

- 通过可配置AGC数据端口实现衰减器快速控制

- 具有可编程阈值的峰值检测标志

- 单通道或多通道,支持JESD204B

- 低功耗:1.20 W

- 电源电压:1.1 V和2.5 V

- TDD省电高达60%

- 4.3 mm × 5.0 mm WLCSP

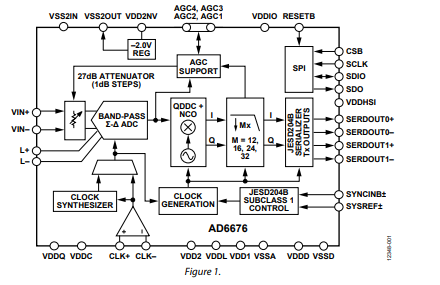

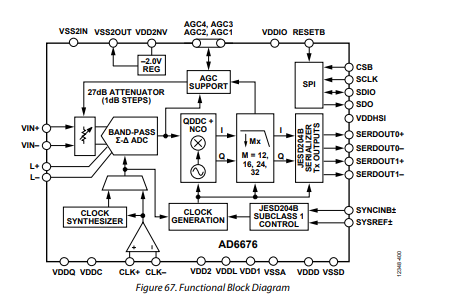

框图

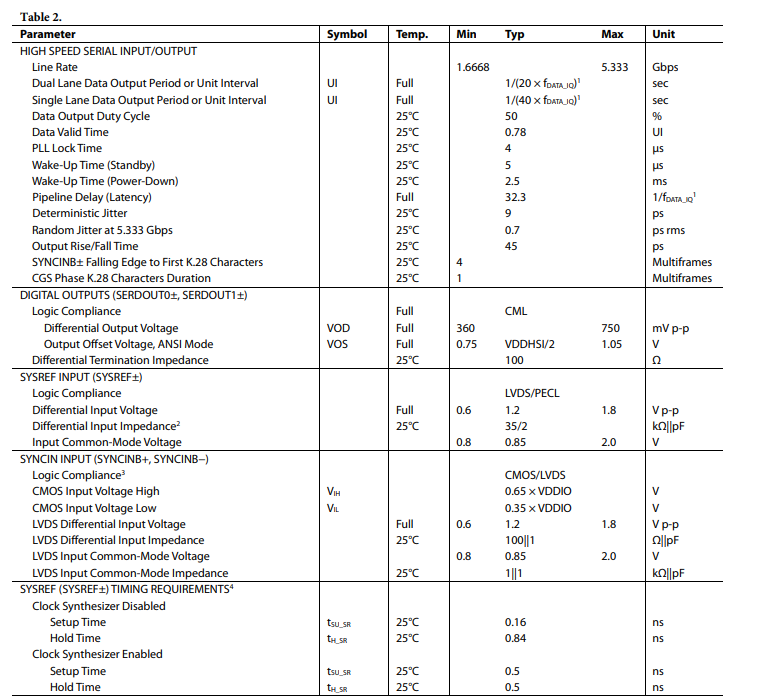

数字高速SERDES规格

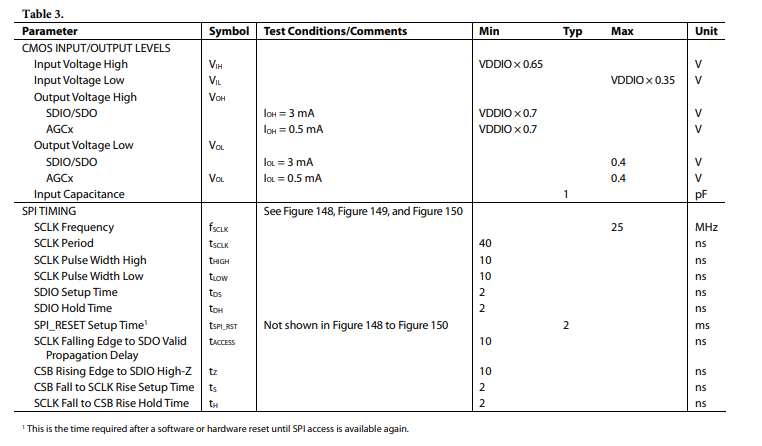

数字CMOS输入/输出规格

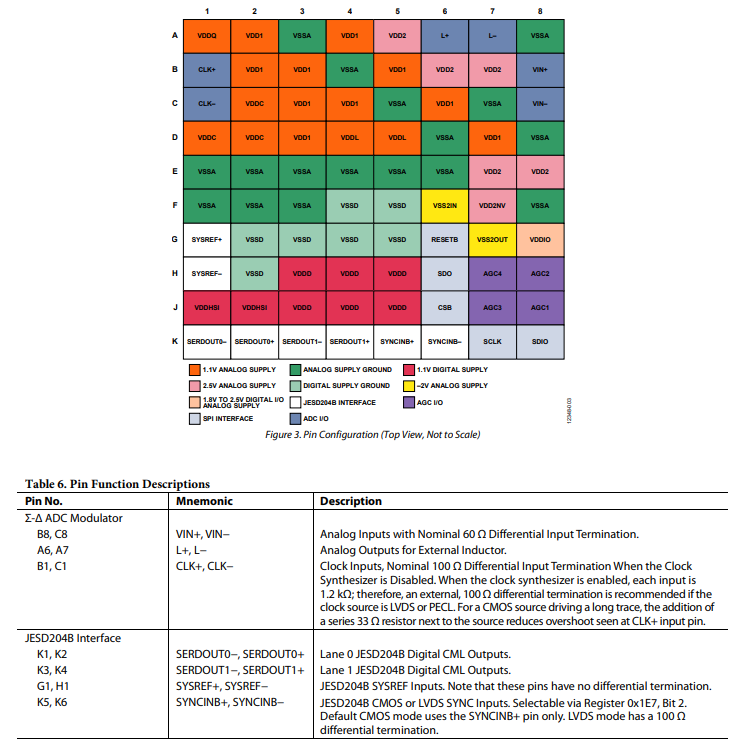

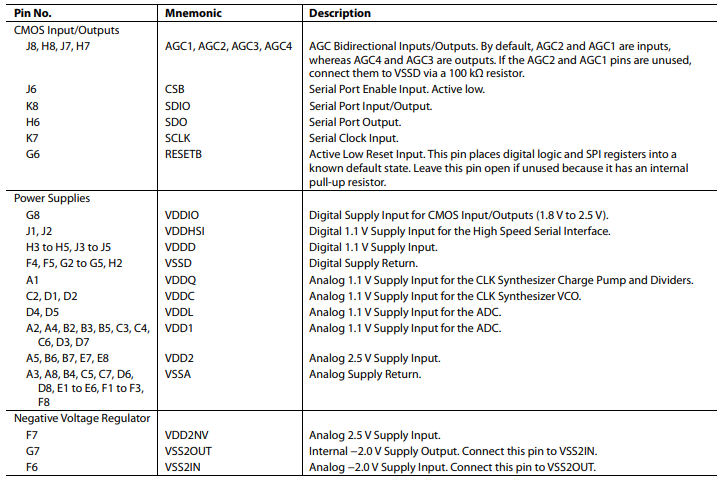

引脚配置描述

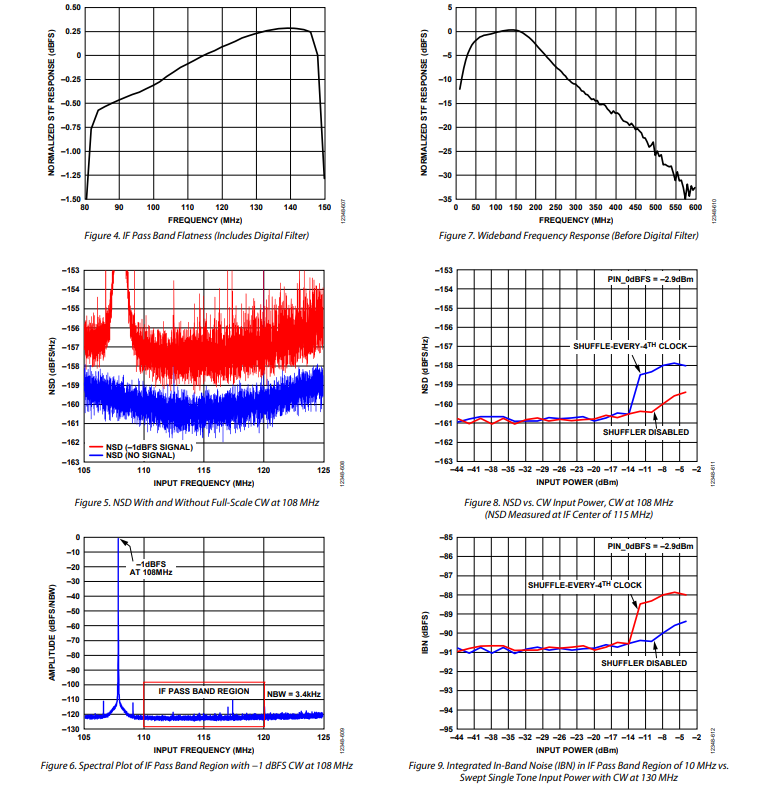

典型性能特征

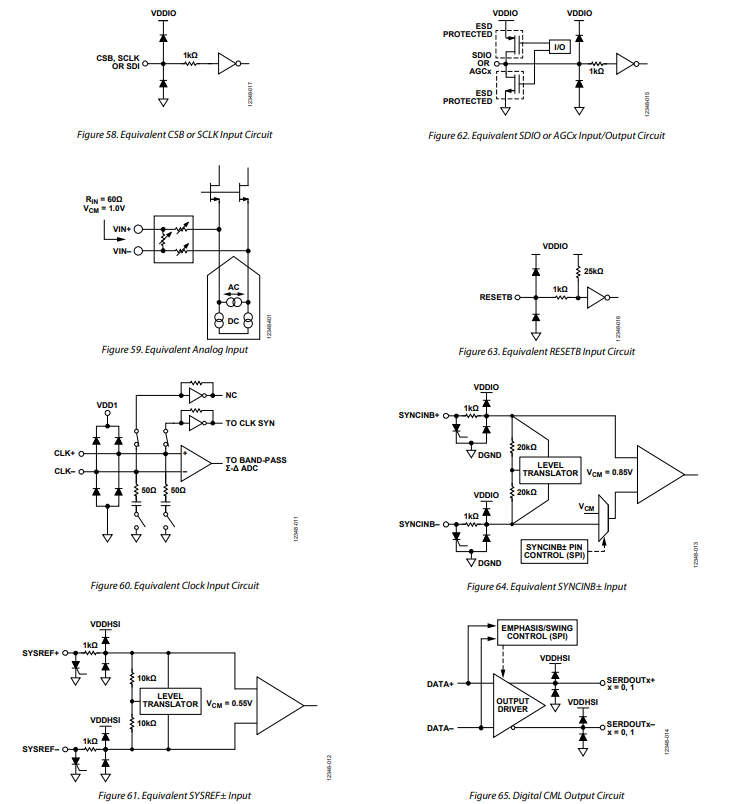

等效电路

工作原理

概述

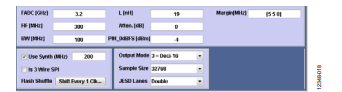

AD6676是一款高度集成且灵活的中频(IF)子系统,能够对中频信号进行数字化处理。它具备调节中频频率和带宽的能力,从而针对不同的应用场景优化Σ - Δ ADC的带宽与动态范围。为了便于评估和设计,还提供了一款软件工具,即AD6676EBZ开发平台,用于配置和评估该器件。此工具可存储SPI初始化和配置序列,以供后续使用。图形用户界面(GUI)前面板的截图(图66)展示了不同的应用参数设置,这些设置可对AD6676进行配置。以下讨论将深入介绍器件的操作原理,以及这些应用参数对性能的影响。

图66. 有助于器件配置和评估的AD6676 GUI软件工具截图

AD6676的功能框图如图67所示。其核心是连续时间带通Σ - Δ ADC,工作时钟频率在2.0 GHz至3.2 GHz之间。片上控制器会根据用户指定的应用参数来配置Σ - Δ ADC。Σ - Δ ADC可在期望的中频范围内提供出色的动态范围和带外抑制能力,同时将带内平坦度控制在0.5 dB以内。片上时钟合成器可提供2.94 GHz至3.2 GHz的Σ - Δ ADC时钟。或者,也可提供外部时钟,以实现更低的时钟速率或更好的相位噪声性能。

片上数字信号处理模块包括一个正交数字下变频器(QDDC),其后是可选的抽取滤波器,支持的抽取因子为12、16、24或32。QDDC能够对复信号进行处理,使其以直流为中心,即零中频。级联抽取滤波器可去除ADC固有的带外噪声以及其他带外信号成分,从而将16位复数IQ数据速率降低至更易于管理的水平,以便通过单通道或双通道JESD204B接口传输至主机,该接口支持的速率高达5.333 Gbps。

AD6676还具备自动增益控制(AGC)支持和/或电平规划功能。AGC支持功能包括能够监测Σ - Δ ADC输出的峰值功率,或监测第一个内部抽取级后的均方根功率。主机可通过配置各种标志位来启动快速AGC操作,这些标志位的状态可通过AGCA至AGCI引脚获取。这些标志位可设置可编程阈值,以指示信号电平是高于还是低于设定水平。此外,还提供了一个步长为1 dB的27 dB衰减器,用于在初始系统校准期间进行电平规划。或者,标称0 dBFS满量程输入功率引脚(PIN_0dBFS)的 - 2 dBm输入功率可衰减12 dB,从而进一步降低射频/中频增益要求。SPI可对AD6676的众多参数进行编程,使其能够针对各种应用进行优化。

-

AD607:低功耗接收机中频子系统的卓越之选2026-04-24 191

-

AD6676:宽带中频接收器子系统的卓越之选2026-03-30 183

-

雷达接收机噪声系数定义 接收机噪声系数是多少2023-07-21 5132

-

AD6676:高动态范围宽带接收器Ad6676评估板的设计工具和启动指南2021-05-24 1909

-

AD6676 AMI型号2021-03-24 713

-

如何对宽带零中频接收机的性能进行优化设计2019-08-15 3425

-

AD6676在宽带中频接收机子系统中的应用分析2019-07-18 3723

-

AD6676的优缺点分析 ∑-∆型ADC的意义何在?2018-10-31 3730

-

ADI推出单芯片宽带IF接收器子系统AD6676,可减少接收器设计的复杂性2018-09-12 1768

-

零中频接收机设计2013-09-25 8791

-

低功耗接收机中频子系统芯片AD608的原理、特点与应用2009-04-30 719

-

低功耗接收机中频子系统芯片AD6072009-04-25 818

-

带有集成电压调节器的CDMA接收机中频子系统芯片AD61212009-04-24 591

-

宽带中频数字接收机的FPGA实现2006-03-11 1835

全部0条评论

快来发表一下你的评论吧 !