AD6641 250MHz带宽DPD观测接收机技术手册

描述

概述

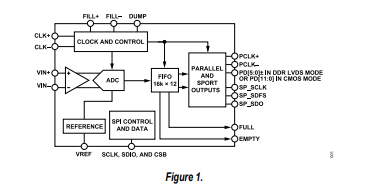

AD6641是一款250 MHz带宽数字预失真(DPD)观测接收机,集成一个12位500 MSPS ADC、一个16k × 12 FIFO和一个多模式后端,用户可通过串行端口(SPORT)、SPI接口、12位并行CMOS端口或6位DDR LVDS端口检索存储在集成FIFO存储器中的数据。它具有出色的动态性能和低功耗特性,适合电信应用,如要求更宽带宽的数字预失真观测路径等。芯片上集成了全部必需功能,包括采样保持器与基准电压源,可提供完整的信号转换解决方案。

数据表:*附件:AD6641 250MHz带宽DPD观测接收机技术手册.pdf

片内FIFO允许通过ADC捕捉较短的时间快照,以及以较低速率进行回读。这样,捕捉的数据可以随时以低得多的采样速率进行传输,信号处理限制得以降低。FIFO可以在多种用户可编程模式下工作。在单次捕捉模式下,当捕捉到ADC数据时,可以通过SPI端口或者使用外部FILL±引脚来指示。在连续捕捉模式下,数据持续加载到FIFO中,并使用FILL±引脚停止该操作。

FIFO中存储的数据可以在多种用户可选的输出模式下回读。可以置位DUMP引脚以输出FIFO数据。FIFO中存储的数据可以通过SPORT、SPI、12位并行CMOS端口或6位DDR LVDS接口访问。AD6641在12位CMOS或6位DDR LVDS模式下支持最大输出吞吐速率,器件内部将其限制为最大输入采样速率的1/8。也就是说,当输入时钟速率为500 MSPS时,最大输出数据速率为62.5 MHz。

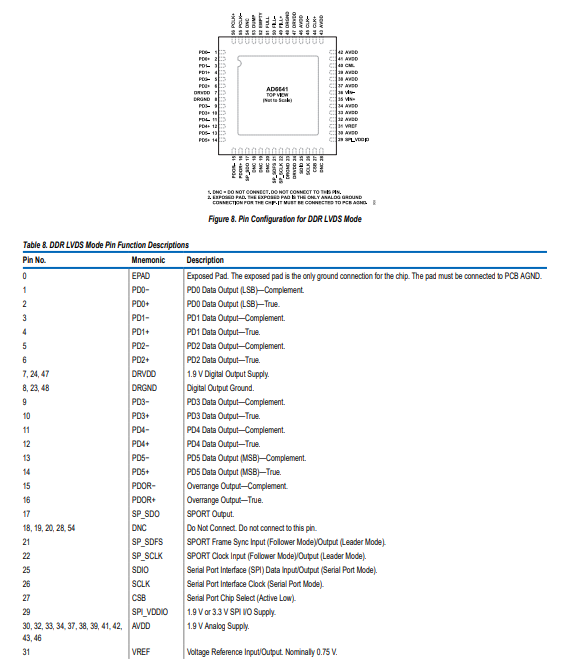

该ADC要求采用1.9 V模拟电源供电及差分时钟信号,以便充分发挥其工作性能。输出格式选项包括二进制补码、偏移二进制和格雷码。该ADC还提供数据时钟输出,用于正确进行输出数据定时。该器件采用先进的SiGe BiCMOS工艺制造,提供56引脚LFCSP封装,额定温度范围为-40°C至+85°C工业温度范围。该产品受美国专利保护。

应用

- 无线和有线宽带通信

- 通信测试设备

- 功率放大器线性化

产品特色

- 高性能ADC内核。

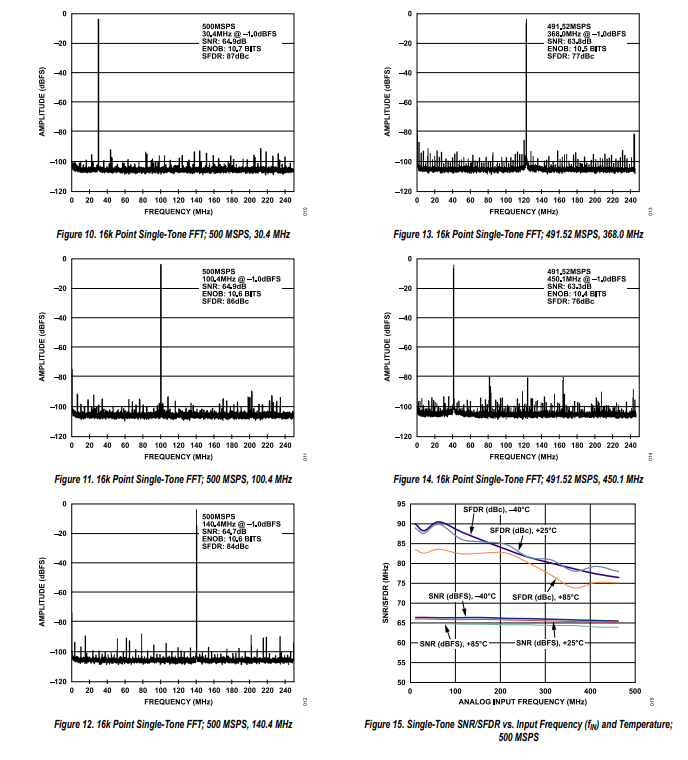

500 MSPS、250 MHz输入时信噪比维持在65.8 dBFS。 - 低功耗。500 MSPS时功耗仅695 mW。

- 易于使用。

片内16k FIFO允许用户让高性能ADC在目标时间执行处理,并在任意时间以较低的采样速率传输数据,从而减少数据处理的限制。片内基准电压源和采样保持功能使系统设计更灵活。采用1.9 V单电源则简化了系统电源设计。 - 串行端口控制。

标准串行端口接口支持对器件进行配置以及根据用户的需求进行定制。 - 1.9 V或3.3 V SPI和串行数据端口工作模式。

特性

- 信噪比(SNR):65.8 dBFS(f

IN最高为250MHz,500 MSPS) - 有效位数(ENOB):10.5位(f

IN最高为250 MHz,500 MSPS,−1.0 dBFS) - 无杂散动态范围(SFDR):80 dBc(f

IN最高为250 MHz,500 MSPS,−1.0 dBFS) - 出色的线性度

- DNL = ±0.5 LSB(典型值);INL = ±0.6 LSB(典型值)

- 集成16k × 12 FIFO

- FIFO回读选项

- 12位并行CMOS(62.5 MHz)

- 6位DDR LVDS接口

- SPORT (62.5 MHz)

- SPI (25 MHz)

- 高速同步功能

- 1 GHz全功率模拟带宽

- 集成输入缓冲器

- 片内基准电压源,无需外部去耦

- 低功耗

- 695 mW (500 MSPS)

- 可编程输入电压范围

- 1.18 V至1.6 V,标称值1.5 V

- 采用1.9 V模拟和数字电源供电

- 1.9 V或3.3 V SPI和SPORT工作模式

- 时钟占空比稳定器

- 带可编程时钟和数据对准功能的集成数据时钟输出

框图

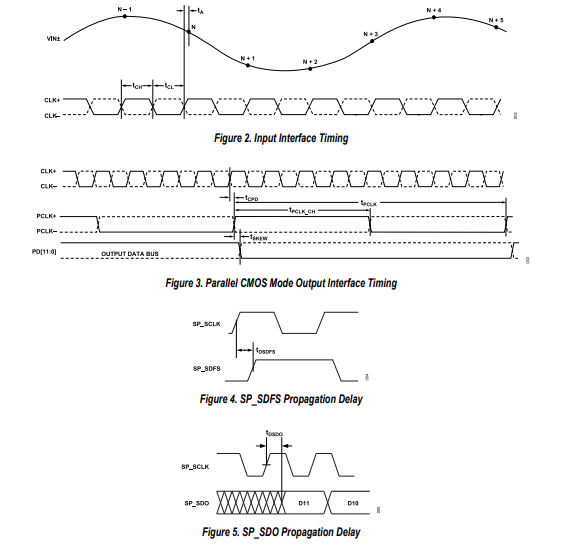

时序图

引脚配置描述

典型性能特征

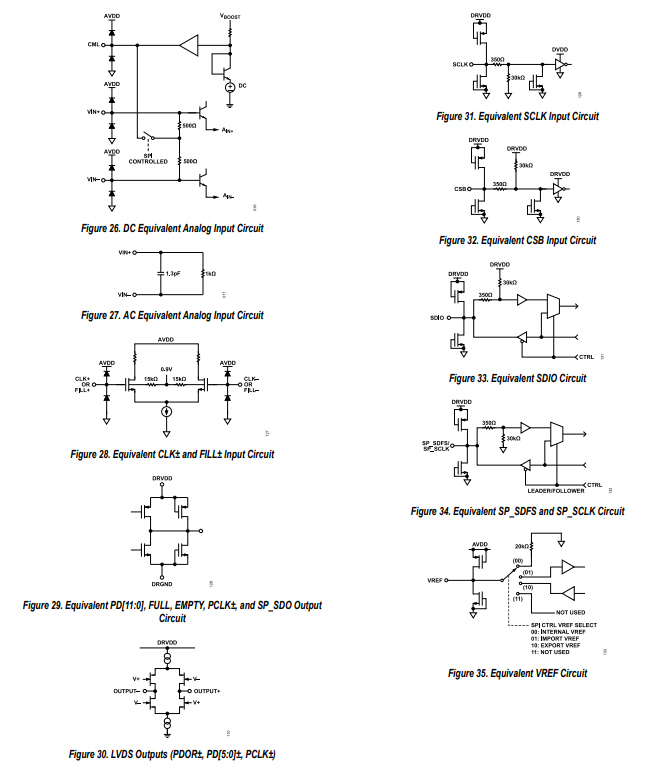

等效电路

工作原理

片上先进先出存储器(FIFO)能够通过模数转换器(ADC)捕获短时间的信号快照,并以较低速率回读。这通过以任意采样率传输捕获的数据,减少了信号处理的限制。

FIFO操作

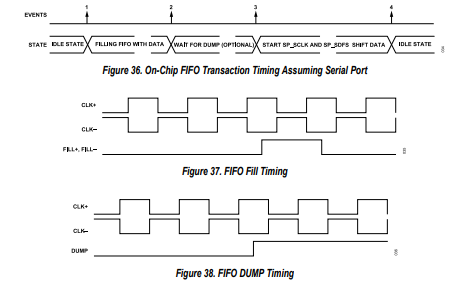

数据捕获可通过向串行外设接口(SPI)端口写入来指示,方式是置位FILL±引脚。图36所示的时序图说明了FIFO的加载过程。

在事件1时,通过断言FILL±引脚或通过SPI位写入来指示FIFO进行填充。FILL±引脚操作可以通过可编程SPI填充控制位进行延迟,这样在填充事件之前可对数据进行缓冲。然后,FIFO会用数据填充自身。周围样本的数量由计数寄存器(0x104)确定。这是一个8位寄存器,取值范围为0到255。放入FIFO的样本数量由以下公式确定:

样本数量 = (FILL_CNT + 1) × 64

在FIFO完成填充(事件2)后,AD6461会发送一个满标志来指示FIFO已填满,然后进入等待状态,在此期间设备等待接收来自DUMP引脚或SPI的转储指令。

数据移位(事件4)后,FIFO进入空闲状态,并等待下一个填充命令。在空闲状态下,ADC可以选择置于深度猝发模式以节省功率。如果ADC在空闲状态下掉电,启动填充操作(事件1)会使ADC上电。在此期间,ADC会等待设置计数周期(0x105、0x106),然后再捕获数据。设置计数可在SPI端口编程,允许在采集数据前让模拟电路稳定下来。通过使用这个寄存器,可以在采集速度和精度之间进行智能权衡。

这些数据可以通过三个输出接口中的任意一个以低数据速率回读,这进一步节省了功率。如果使用SPI或SPORT接口读取数据,该接口可能只需要三个引脚。满标志和空标志用于指示FIFO的状态。SPI中的FIFO状态寄存器(0x10A)也可以通过软件进行监控。

单次捕获模式

通过将填充控制寄存器(0x103[3:2])中的FIFO填充模式位写入00,可将FIFO置于单次捕获模式。在单次捕获模式下,用户通过驱动FILL±引脚高电平或通过SPI端口写入(如有必要)填充位(0x101[0])来启动捕获。这会在上电后(根据SPI设置计数寄存器(0x105、0x106)中设置的时间)为ADC(如果已掉电)供电。如果0x101寄存器中的位3置位,捕获完成后ADC会返回待机模式。

填充引脚定时

通过断言差分FILL±引脚可以启动FIFO填充。在FILL±引脚上检测到脉冲时,FIFO开始填充。

转储引脚定时

通过断言DUMP引脚可以启动FIFO回读。在DUMP引脚上检测到高电平时,FIFO数据会在可用时钟上被清除。

-

高性能65 MHz带宽四通道中频接收机电路图2013-11-13 5918

-

请问AD6641采集出来的数据和输入模拟量电压信号转换的公式是什么?2018-09-13 2739

-

PIC32MZ2048EFH 250Mhz怎么说?2019-03-25 2250

-

什么是海量存储宽带接收机?2019-08-09 2280

-

AD6641采集出来的数据和输入模拟量电压信号转换的公式是什么?2023-12-18 498

-

40MHz AM接收机的高放电路2009-03-13 2492

-

MAX19790应用电路--250MHz至4000MHz、双2010-07-11 1208

-

250 MHz带宽DPD观测接收机 AD66412014-09-24 887

-

385MHz带宽中频分集接收机2017-06-06 1309

-

AD6641 250 MHz带宽DPD观测接收机2019-02-22 544

-

AD6641: 250 MHz带宽DPD观测接收机2021-03-21 740

-

评估AD6688射频分集和1.2 GHz带宽观测接收机2021-04-09 2279

-

EVAD6641 AD6641 评估板2021-06-03 574

-

AD6679 135MHz带宽中频分集接收机技术手册2025-04-28 1058

-

高性能低功耗的AD6641:数字预失真观测接收器的优选之选2026-03-31 318

全部0条评论

快来发表一下你的评论吧 !