AD6642双通道中频接收机技术手册

描述

概述

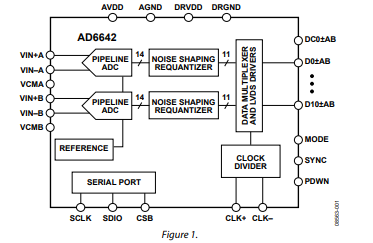

AD6642是一款11位、200 MSPS、双通道中频(IF)接收机,专门针对要求高动态范围性能、低功耗和小尺寸的电信应用中支持多通道系统而设计。

该器件包括两个高性能模数转换器(ADC)和噪声整形再量化器(NSR)数字模块。各ADC采用多级、差分流水线架构,并集成了输出纠错逻辑。ADC差分流水线的第一级包含一个宽带宽开关电容采样网络。集成基准电压源可简化设计。占空比稳定器(DCS)补偿ADC时钟占空比的波动,使转换器保持出色的性能。

数据表:*附件:AD6642双通道中频接收机技术手册.pdf

各ADC的输出内部连接到NSR模块。集成NSR电路能够提高奈奎斯特带宽内较小频段的信噪比(SNR)性能。该器件支持两种不同的输出模式,通过外部MODE引脚或SPI可以选择输出模式。

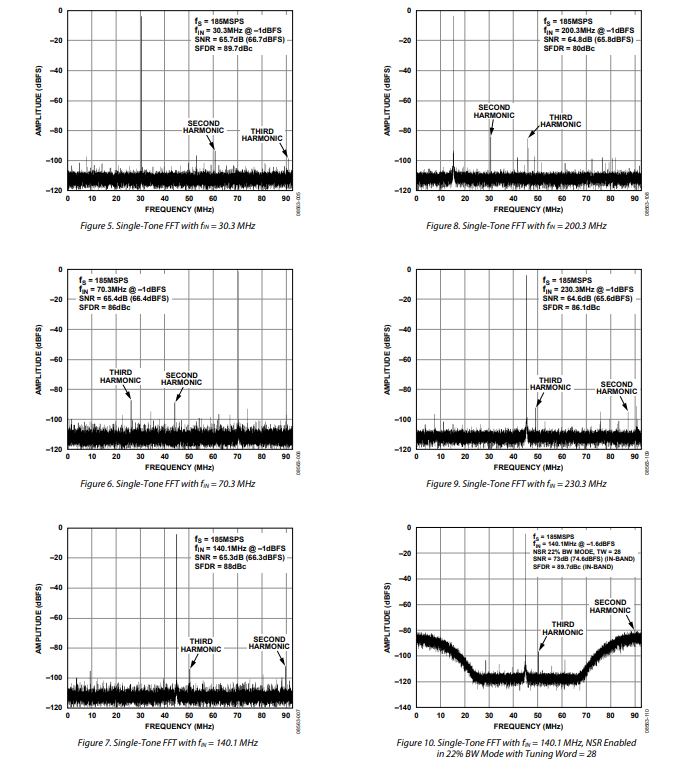

如果使能NSR特性,则在处理ADC的输出时,AD6642可以在有限的部分奈奎斯特带宽内实现更高的SNR性能,同时保持11位输出分辨率。可以对NSR模块进行编程,以提供采样时钟22%或33%的带宽。例如,当采样时钟速率为185 MSPS时,在22%模式下,AD6642可以在40 MHz带宽内实现最高75.5 dBFS的SNR; 在33%模式下,它可以在60 MHz带宽内实现最高73.7 dBFS的SNR。

如果禁用NSR模块,则ADC数据直接以11位的分辨率提供给输出端。这种工作模式下,AD6642能够在整个奈奎斯特带宽内实现最高66.5 dBFS的SNR。因此,AD6642可以用于电信应用,例如要求更宽带宽的数字预失真观测路径。

经过数字信号处理后,多路复用输出数据路由至两个11位输出端口,最大数据速率为400 Mbps (DDR)。这些输出设置为1.8 V LVDS,支持ANSI-644电平。AD6642接收机能够对很宽的中频频谱进行数字化处理。各接收机设计用于同步接收不同的天线。该IF采样架构与传统的模拟技术或较低集成度的数字方法相比,能大幅度降低器件的成本和复杂度。

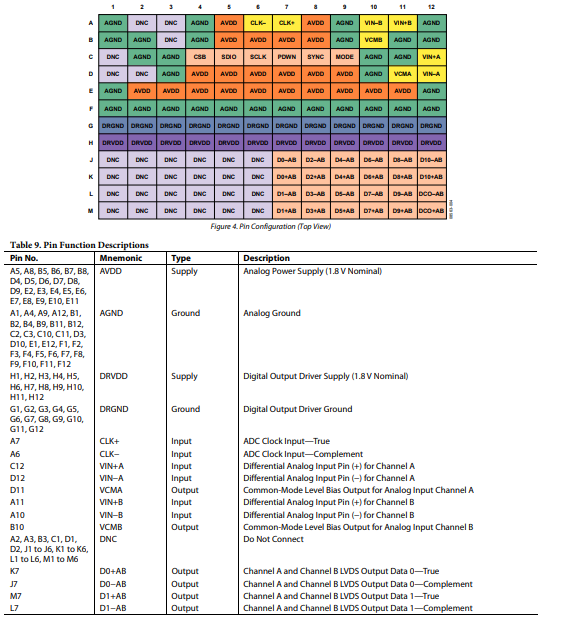

灵活的关断选项可以明显降低功耗。器件设置与控制的编程利用三线式SPI兼容型串行接口来完成;该接口提供多种工作模式,支持电路板级系统测试。AD6642采用144引脚无铅10 mm × 10 mm芯片级球栅阵列(CSP_BGA)封装,符合RoHS标准,额定温度范围为−40°C至+85°C工业温度范围。

应用

- 通信

- 分集无线电和智能天线(MIMO)系统

- 多模式数字接收器(3G)

- WCDMA、LTE、CDMA2000

- WiMAX、TD-SCDMA

- I/Q解调系统

- 通用软件无线电

特性

- 每个通道11位、200 MSPS输出数据速率

- 集成噪声整形再量化器(NSR)

- 使能NSR时的性能

SNR:75.5 dBFS(40 MHz带宽,最高70 MHz,185 MSPS)

SNR: 73.7 dBFS(60 MHz带宽,最高70 MHz,185 MSPS) - 禁用NSR时的性能

SNR:66.5 dBFS(最高70 MHz,185 MSPS)

SFDR: 83 dBc(最高70 MHz,185 MSPS) - 低功耗:0.62 W (185 MSPS)

- 1.8 V模拟电源供电

- 1.8 V LVDS(ANSI-644电平)输出

- 1至8整数时钟分频器

- ADC内部基准电压源

- 模拟输入范围:1.75 V p-p(可编程至2 V p-p)

- 差分模拟输入、800 MHz带宽

框图

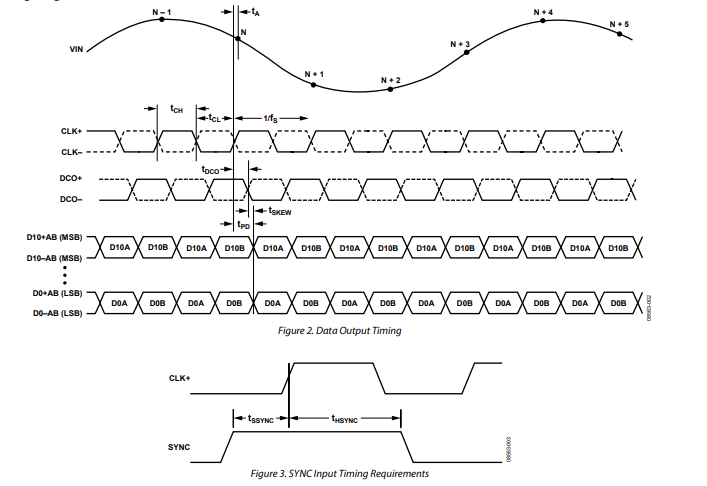

时序图

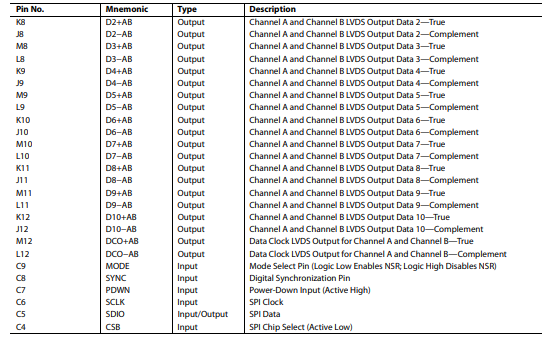

引脚配置描述

典型性能特征

工作原理

ADC架构

AD6642架构由双前端采样保持电路组成,其后连接流水线开关电容ADC。每个阶段的量化输出先进行合并,再得到最终的14位数字校正逻辑结果。或者,这14位结果在送入数字校正逻辑之前,可先通过噪声整形量化器(NSR)模块进行处理。

流水线架构使第一级能够基于新的输入样本运行,并让其余各级对前一个样本进行处理,在时钟上升沿进行采样。

流水线的每一级(最后一级除外)均由一个低分辨率闪存ADC、一个数模转换器(DAC)以及一个积分误差放大器(MDAC)组成。MDAC对DAC输出与下一级流水线中闪存输入的差值进行放大。每一级中都有一位冗余,用于校正闪存误差。最后一级仅由一个闪存ADC组成。

每个通道的输入级包含一个差分采样电路,可实现交流耦合或单端模式。输出数据锁存模块会阻塞数据、校正误差,并将数据输出到外部缓冲器。输出缓冲器由独立电源供电,在掉电期间,输出缓冲器进入高阻态。

AD6642双中频接收器可同时对两个通道进行数字化处理,适用于通信系统中多样性接收和数字预失真(DPD)观测路径。

它具备同步功能,可实现多个通道或多个器件之间的定时同步。通过一个三线制、SPI兼容的串行接口对AD6642进行编程和控制。

模拟输入注意事项

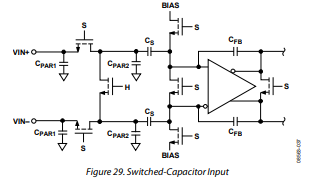

AD6642的模拟输入采用差分开关电容电路,针对差分输入信号处理进行了优化。

时钟信号交替切换输入电路,使其在采样模式和保持模式间转换(见图29)。处于采样模式时,信号源必须能够在半个时钟周期内完成对采样电容的充电以及设置。

每个输入端串联一个小电阻,有助于降低驱动源输出级所需的峰值瞬态电流。可在输入端之间并联一个旁路电容,为动态充电电流提供通路。这种无源网络会在ADC输入端形成一个低通滤波器,因此,具体数值取决于应用场景。

为实现最佳动态性能,需匹配驱动VIN+和VIN - 引脚的源阻抗。

内部差分基准缓冲器会产生正电压和负电压,用于定义ADC内核的输入范围。ADC内核的范围由该缓冲器设置为2 × VREF 。

输入共模

AD6642的模拟输入内部无直流偏置。在交流耦合应用中,用户必须从外部提供此偏置。将器件设置为VCM = 0.5 × AVDD(或0.9 V)可实现最佳性能。

芯片设计中集成了片上共模电压基准,可通过VCMx引脚获取。建议使用VCM输出来设置输入共模。

模拟输入的最佳共模电压由VCMx引脚电压(通常为0.5 × AVDD)设定。VCMx引脚必须通过0.1 μF电容接地。

-

AD6659混合信号双通道中频接收机2010-08-12 1548

-

高性能、双通道IF采样接收机2011-03-31 640

-

双通道接收机的设计2011-12-14 625

-

零中频射频接收机技术2016-12-16 1101

-

80MHz带宽双通道中频接收机2017-06-01 1734

-

AD6642 双通道中频接收机2019-02-22 465

-

AD6643双通道中频接收机的性能及应用2019-06-20 4079

-

AD6643: 双通道中频接收机2021-03-20 912

-

AD6649: 中频分集接收机2021-03-21 1009

-

AD6642:双中频接收器数据表2021-04-23 691

-

AN-1589:高性能双通道中频采样接收机2021-05-26 814

-

EVAD6642 AD6642 评估板2021-06-03 687

-

CN0140 高性能、双通道IF采样接收机2021-06-06 1194

-

AD6643双通道中频接收机技术手册2025-04-28 1116

-

AD6642双中频接收器:高性能与低功耗的完美结合2026-03-31 292

全部0条评论

快来发表一下你的评论吧 !