AD6650分集中频至基带GSM/EDGE窄带接收机技术手册

描述

概述

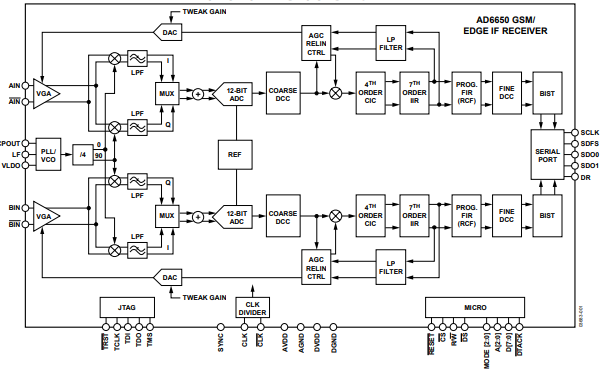

AD6650是一款分集中频至基带接收机,适用于GSM/EDGE。这款窄带接收机由一个集成DVGA、中频至基带I/Q解调器、低通滤波和一个双通道宽带ADC组成。该芯片可处理70 MHz至260 MHz的中频输入。接收机架构经过特别设计,整个接收信号路径只需要一个用于主信号的外部表面声波(SAW)滤波器和一个用于分集信号的滤波器,便可达到GSM/EDGE阻塞要求。

片内数字抽取与滤波电路可消除目标通道之外的干扰信号和噪声。利用可编程RAM系数滤波器,只需一个经济高效的滤波器,便可实现抗混叠、匹配滤波和静态均衡三种功能。通道滤波器的输出通过串行输出I/Q数据流提供给用户。

数据表:*附件:AD6650分集中频至基带GSM EDGE窄带接收机技术手册.pdf

应用

- PHS或GSM/EDGE单载波、分集接收机

- 微蜂窝和微微蜂窝系统无线本地环路

- 智能天线系统

- 软件无线电建筑物内无线电话

特性

- 动态范围:116 dB

- 数字VGA

- I/Q解调器

- 有源低通滤波器

- 双通道宽带ADC

- 可编程抽取和通道滤波器

- VCO和锁相环电路

- 串行数据输出端口

框图

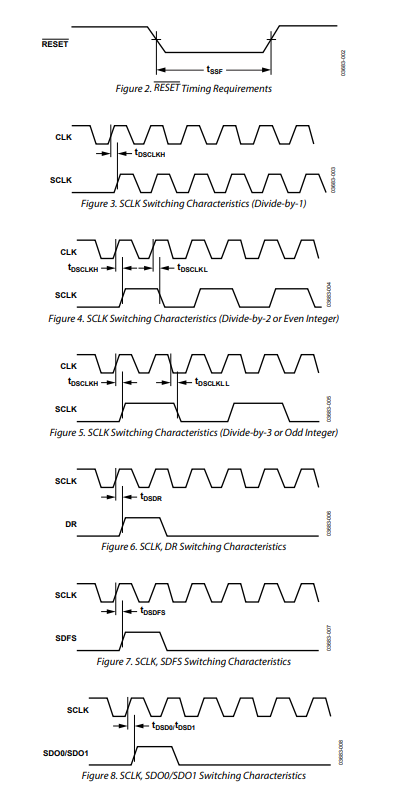

时序图

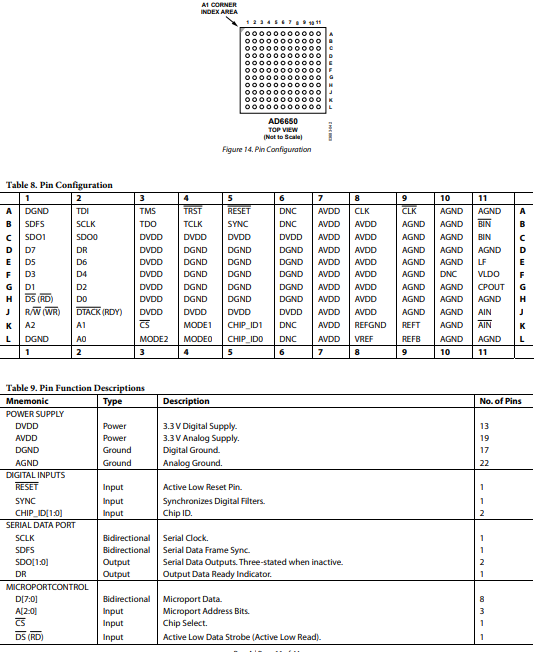

引脚配置描述

工作原理

模拟前端

AD6650是一款混合信号前端(MxFE)组件,适用于需要高动态范围的直接中频采样无线电设备。它针对GSM和EDGE标准的性能要求进行了优化。

AD6650包含五个信号处理阶段:数字可变增益放大器(VGA)、同相/正交(I/Q)解调器、七阶低通滤波器、双ADC以及数字滤波。其编程和控制通过微处理器接口实现。

数字可变增益放大器(DVGA)

一个增益可变的数字VGA用于扩展ADC的动态范围,并最大程度减少ADC输入处的信号削波。VGA的最大增益为36 dB,标称步长为0.094 dB。放大器级作为AD6650的输入级,标称输入阻抗为200 Ω,输入功率为4 dBm。

I/Q解调器

频率转换通过I/Q解调器实现。进入此级的实数据通过同相(I)和正交(Q)解调器分离。该级将输入信号从70 MHz至260 MHz的中频(IF)转换为2.59 MHz的基带频率。

低通滤波器

每个I/Q信号路径中都有一个七阶低通有源滤波器,带宽为3.5 MHz,具备自动阻容校准功能,校准精度为±4%。此滤波器通常能提供大于70 dB的2.59 MHz以上频率的混叠抑制。

双ADC

AD6650有两个ADC,每个ADC都采用AD9238内核,前面有双路跟踪保持电路,分别以26 MSPS的速率对I和Q信号进行多路复用。满量程输入功率为4 dBm。

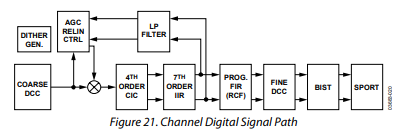

数字后端

12位ADC数据通过粗直流校正模块,该模块对I和Q路径中的直流失调进行一次性校准。此模块的输出驱动自动增益控制(AGC)回路,该回路调节模拟路径中数字控制的VGA。AGC调整输入感兴趣信号的幅度,达到可编程水平,防止ADC削波。VGA的增益从重新线性化模块中减去。例如,如果外部AD6650的增益在20 dB至30 dB之间,由于信号功率从20 dB降至 - 20 dB,VGA必须增加30 dB的增益,以保持AD6650的总响应不变。

然后,AGC模块的19位输出通过CICA滤波器进行抽取和滤波,再经过IIR滤波器以及可编程随机存取存储器系数滤波器(RCF)。16位或24位数据通过串行端口输出。

凭借36 dB的VGA增益、12位ADC性能以及高达21 dB的处理增益,AD6650能够提供约116 dB的动态范围或19位性能。出于这个原因,使用24位串行输出,以确保动态范围不会损失。数字信号路径的框图如图21所示。

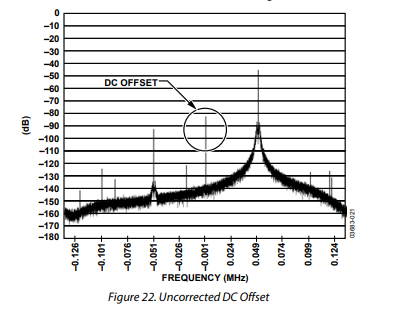

直流校正

AD6650模拟路径中的直流失调源自三个方面:模拟基带滤波器、ADC以及混频器的本振(LO)泄漏。模拟滤波器和ADC的直流失调会导致LO泄漏产生直流偏移。I和Q路径的直流失调不同,因为它们使用不同的模拟路径,且每条路径都独立校正。

未校正的直流失调相对于ADC的满量程(dBFS)通常在 - 32 dB至 - 35 dB之间。考虑到AGC范围后,直流失调实际上会因增益设置而降低,当AD6650处于最大增益时,约为 - 68 dBFS至 - 71 dBFS或更小。

-

中频至基带接收机电路功能与优势2019-07-05 3417

-

具有中频和基带可变增益以及可编程基带滤波功能的中频至基带接收机,不看肯定后悔2021-05-24 2390

-

ADI实验室电路:灵活的中频至基带接收机解决方案2013-01-11 12045

-

基于IQ解调器的中频至基带接收机设计2019-03-13 4285

-

AD6650 分集中频至基带GSM/EDGE窄带接收机2019-02-22 589

-

CN0320:基于IQ解调器,具有中频和基带可变增益以及可编程基带滤波功能的中频至基带接收机2021-03-18 833

-

AD6649: 中频分集接收机2021-03-21 1009

-

AN-502:采用中频采样分集芯片组设计超外差接收机2021-04-15 1095

-

AD6650:分集IF-to-基带GSM/EDGE窄带接收机数据表2021-04-25 707

-

AD6652:12位、65 MSPS中频至基带分集接收器数据表2021-04-30 854

-

评估AD6679中频分集接收机2021-05-09 2931

-

AD6653:中频分集接收机数据表2021-05-10 796

-

评估AD6674中频分集接收机2021-05-13 2132

-

AD6600分集接收机芯片组技术手册2025-04-28 1123

-

深入剖析AD6650:打造高性能GSM/EDGE接收系统的核心利器2026-04-01 565

全部0条评论

快来发表一下你的评论吧 !