AD9874低功耗中频数字化子系统技术手册

描述

概述

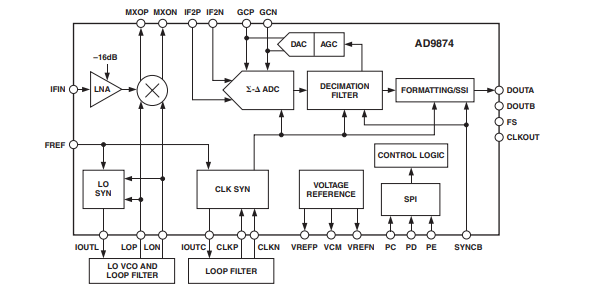

AD9874是一款通用中频子系统,可对带宽最高至270 kHz的低电平10至300 MHz中频输入信号进行数字处理。AD9874的信号链包括一个低噪声放大器、混频器、一个带通Σ-Δ型模数转换器以及一个具有可编程抽取系数的抽取滤波器。自动增益控制(AGC)电路提供12 dB的连续增益调整。

高动态范围和带通Σ-Δ型转换器内在的抗混叠功能,使该器件能处理比目标信号强度高达95 dB的阻塞信号。除串行外设接口端口外,辅助模块还包括时钟和LO频率合成器。

通过SPI端口可对AD9874的许多参数进行编程,因此该器件可针对特定应用进行优化。可编程参数包括:频率合成器分频比率、AGC衰减和上升/延迟时间、接收信号强度水平、抽取系数、输出数据格式、16 dB衰减器以及所选的偏置电流。LNA和混频器的偏置电流可以进一步降低,但电池供电应用的性能也会随之降低。

数据表:*附件:AD9874低功耗中频数字化子系统技术手册.pdf

应用

- 多模式窄带无线电产品

模拟/数字UHF/VHF FDMA接收机

TETRA、APCO25、GSM/EDGE - 便携式和移动无线电产品

- 基站应用

- SATCOM终端

特性

- 输入频率:10至300 MHz

- 基带(I/Q)数字输出

- 电源电压:2.7 V至3.6 V

- 输出信号带宽:10至270 KHz

- 单边带噪声系数(SSB NF):8 dB

- 三阶交调截点(IIP3):+1 dBm(典型值,最大偏置)

- 动态范围:95 dB(12 dB连续AGC范围使能时)

- 中频输入:-18 dBm或-30 dBm(最大值,AGC禁用)

- LO和时钟采样频率合成器

- 可编程抽取系数、输出格式、AGC和频率合成器设置

框图

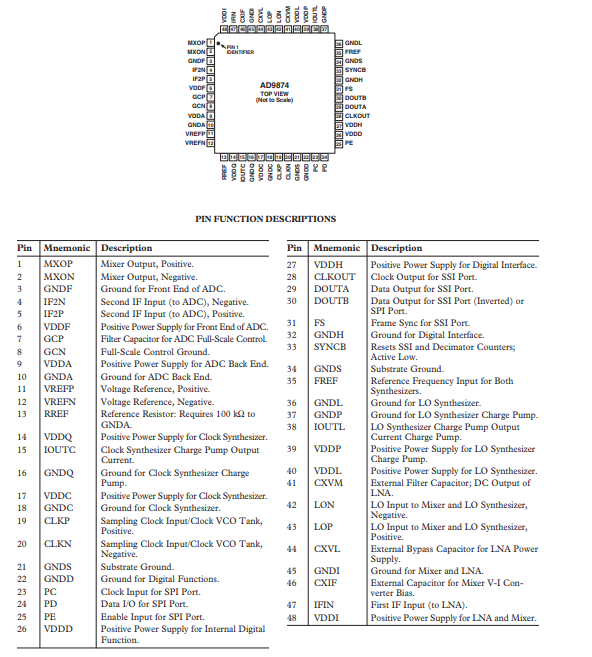

引脚配置描述

串行端口接口(SPI)

AD9874的串行端口具备三线制或四线制SPI功能,允许读/写访问所有用于配置器件内部参数的寄存器。默认的三线制串行通信端口包含一个时钟(PC)、一个主输出从输入(MOSI)和一个双向数据(DT)信号。引脚PC、PE、PD默认具有一个施密特触发器,其数字中心电压约为0.4 V至0.5 V(由VDDH2提供)。

四线制SPI接口可通过设置辅助寄存器(Reg. 0x019,第7位)启用,这样输出数据也会出现在DOUTB引脚。需要注意的是,在默认掉电状态下,DOUTB引脚处于低电平。对于需要设置SPI输出线以避免总线竞争的系统而言,这很有用。DOUTB引脚可通过设置辅助控制位中的第三位(Reg. 0x3B,第3位)进行三态控制,通过切换该位可访问共享SPI输出线。

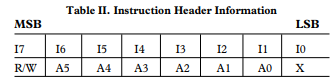

一个8位指令头用于每次读/写SPI操作。只有写操作支持自动递增模式,允许对芯片上配置的单个写操作进行编程。该指令头如表II所示,包含一个读/写指示位、六位地址位,且不区分数据位。需要注意的是,数据位和指令位在地址位之后立即出现,且地址和数据均以最高有效位(MSB)在前的方式给出。

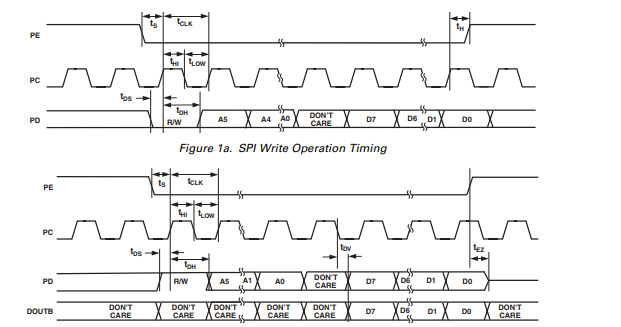

图1a展示了向SPI端口进行写操作的时序要求。在使能引脚(PE)信号变低后,数据(PD)与指令相关的部分在时钟(PC)的上升沿被锁存。要启动写操作,读/写位必须设置为低电平。发送完指定指令头后,在接下来八个时钟周期的上升沿,数据会移入数据引脚(PD)。PE保持低电平,直到操作完成并在第八个时钟周期结束时变高。如果在第八个时钟周期过去后,PE仍为低电平,则操作将再进行八个时钟周期。

如果设置了额外的八个时钟周期,目标地址会递增,另外八个数据位会再次移入。此时,应忽略当前字节的其余部分,通过这种隐式寻址模式可进行整个芯片的配置操作。已确定用于控制频率更新的寄存器,即那些与电源控制和AGC操作相关的寄存器,已被分配了相邻地址,以尽量减少多字节寄存器(最高有效字节为最低地址)更新时所需的时间,并且在写入最低有效字节时会进行更新。

图1b展示了SPI端口读操作的时序。尽管AD9874不需要读操作来实现正确操作,但在产品开发阶段或系统调试时,了解回读数据非常有用。注意,回读使能位(Register 0x3A,第3位)必须置位才能进行读操作,且必须在使能引脚(PE)信号变低之前设置,数据(PD)与指令相关的部分在时钟(PC)的上升沿被锁存。如果读/写指示位为高电平,则会进行读操作。发送完指令头后,目标地址寄存器中的八个数据位会在接下来八个时钟周期的下降沿出现在数据引脚(PD)上。如果启用了四线制SPI接口,八个数据位也会出现在DOUTB引脚上,其与最后一位数据的关系与出现在PD引脚上的情况相同。在最后一位数据移出后,用户应在读操作完成后将PE拉高,使其恢复到正常的非选通输入状态。

由于自动递增模式不支持读操作,因此每个寄存器读操作都需要指令头。在读操作完成且PE拉高之前,下一个读操作无法启动。

-

AD9864中频数字化子系统数据手册解读2026-04-03 98

-

AD9874:通用中频子系统的卓越性能与应用探索2026-04-02 371

-

AD9870中频数字化子系统:技术剖析与应用指南2026-03-30 103

-

AD9864中频数字化子系统技术手册2025-04-28 1450

-

怎么实现基于AD6623的多路中频数字化直扩通信系统的设计?2021-05-28 1382

-

怎么实现中频数字化接收机系统的设计?2021-04-22 2195

-

AD9874:IF数字化子系统数据表2021-04-19 646

-

AD9864:IF数字化子系统数据表2021-04-18 691

-

AD9864 中频数字化子系统2019-02-22 933

-

AD6644做中频数字处理模块及接口的设计2018-09-04 6346

-

中频数字化基带硬件电路设计2018-08-13 4042

-

中频数字化正交解调结构介绍2011-10-08 5792

-

发射机中频数字化的设计与实现2011-02-27 863

-

AD9874,pdf datasheet (IF Digit2009-09-10 842

全部0条评论

快来发表一下你的评论吧 !