MAX5863超低功耗、宽动态范围、7.5Msps模拟前端技术手册

描述

概述

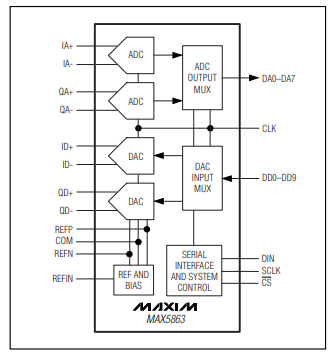

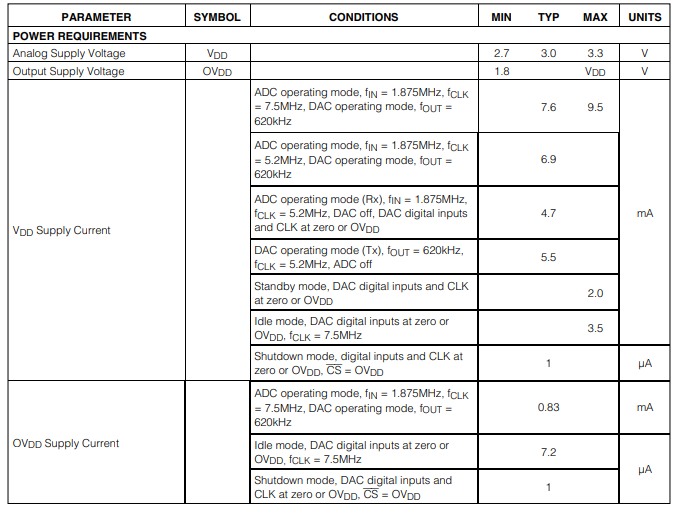

MAX5863超低功耗、高集成度模拟前端可理想用于便携式通信设备,如手机、PDA、WLAN以及3G无线终端。MAX5863集成双路8位接收ADC和双路10位发送DAC,能以极低的功耗提供较高的动态性能。ADC的模拟I-Q输入放大器为全差分结构,可接受1VP-P满量程信号。I-Q通道的典型相位匹配为±0.03°,幅度匹配为±0.03dB。在fIN = 1.875MHz和fCLK = 7.5Msps时,ADC的SINAD为48.5dB,无杂散动态范围(SFDR)为69dBc。DAC的模拟I-Q输出为全差分结构,满量程输出为±400mV,共模电压为1.4V。I-Q通道的典型相位匹配为±0.15°,增益匹配为±0.05dB。在fOUT = 620kHz和fCLK = 7.5MHz时,DAC具有双路10位分辨率,SFDR为73dBc,SNR为61dB。

针对频分复用(FDD)和时分复用(TDD)模式,ADC与DAC可同时或独立工作。3线串行接口可控制关断和收发器的工作模式。在ADC和DAC同时工作的收发器模式下,fCLK = 7.5Msps时功耗典型值为22.8mW。MAX5863具有内部1.024V电压基准,在整个供电范围与温度范围内保持稳定。MAX5863使用+2.7V至+3.3V模拟电源工作,可采用+1.8V至+3.3V数字I/O电源以保证逻辑兼容性。空闲模式下静态电流为3.5mA,关断模式下为1µA。MAX5863工作于扩展的-40°C至+85°C温度范围,提供48引脚薄型QFN封装。

数据表:*附件:MAX5863超低功耗、宽动态范围、7.5Msps模拟前端技术手册.pdf

应用

- 3G无线终端

- 固定/移动宽带无线调制解调器

- 窄带/宽带CDMA手机

- PDA

特性

- 集成双路8位ADC与双路10位DAC

- 超低功耗

- f

CLK= 7.5MHz时22.8mW (收发器模式) - f

CLK= 5.2MHz时2.07mW (收发器模式) - 低电流空闲和关断模式

- f

- 优异的动态性能

- f

IN= 1.875MHz时SINAD为48.5dB (ADC) - f

OUT= 620kHz时SFDR为73dBc (DAC)

- f

- 优异的增益/相位匹配

- f

IN= 1.875MHz时±0.03°相位匹配,±0.03dB增益匹配(ADC)

- f

- 内部/外部基准选择

- +1.8V至+3.3V数字输出电平(TTL/CMOS兼容)

- 为ADC/DAC提供并行数字输入/输出复用

- 微型48引脚薄型QFN封装(7mm x 7mm)

框图

电特性

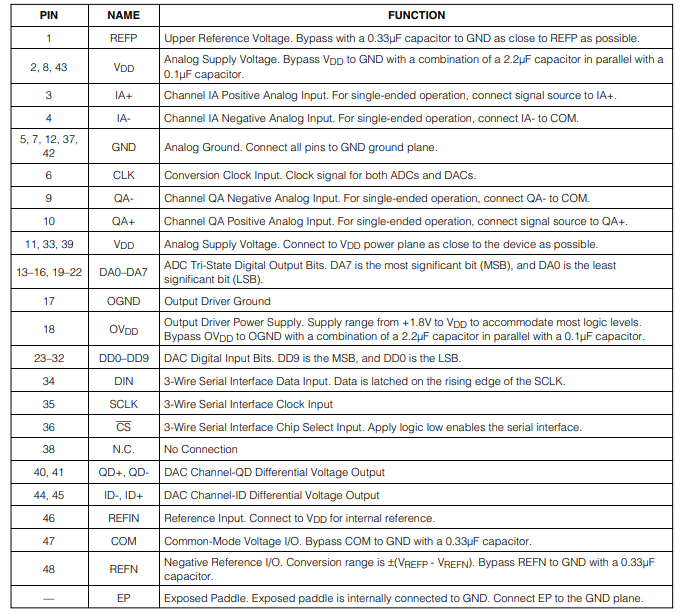

引脚描述

应用信息

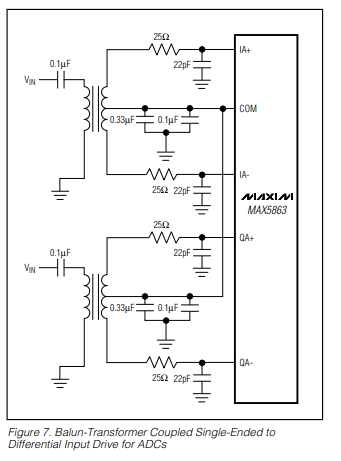

使用平衡 - 不平衡变压器交流耦合

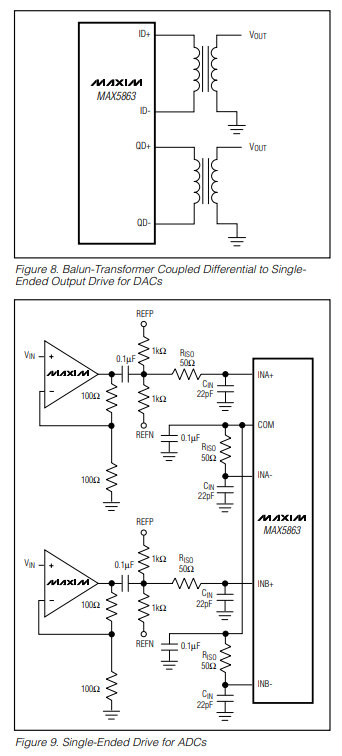

射频变压器(图7)能为将单端信号源转换为全差分信号提供极佳方案,有助于实现ADC的最优性能。将变压器的中心抽头连接到COM引脚,可为输入提供VDD/2的直流电平转换。可选用1:1变压器,也可选择升压变压器来降低驱动要求。一般而言,MAX5863在处理全差分输入信号方面优于SPDR和THD信号,尤其是在较高的输入频率下。在差分模式下,由于两个输入端(IA+、IA - 、QA+、QA - )相互平衡,偶次谐波较低,并且每个ADC输入所需的信号摆幅仅为单端模式下的一半。图8展示了一个利用射频变压器将MAX5863 DAC差分模拟输出转换为单端输出的示例。

使用运算放大器耦合

当没有平衡 - 不平衡变压器可用时,可用运算放大器来驱动MAX5863的模数转换器(ADC)。图9和图10展示了如何使用运算放大器来驱动交流耦合单端和直流耦合差分应用中的ADC。诸如MAX4354、MAX4454等放大器具备高速、高带宽、低噪声和低失真特性,可维持输入信号的完整性。图10中的电路也可用于数模转换器(DAC)差分模拟输出的接口,以提供增益或缓冲。DAC差分模拟输出不能用于单端模式,因为其内部产生的共模电平为1.4 VDC 。此外,DAC模拟输出的设计要求采用差分输入级,且输入阻抗需≥70 kΩ。如果需要单端输出,可使用一个放大器来实现差分转单端转换,并选择具有合适输入共模电压范围的放大器。

频分双工(FDD)和时分双工(TDD)模式

MAX5863可用于多种工作在FDD或TDD模式下的应用。在FDD模式下,MAX5863可用于Xcvr模式的应用,如WCDMA 3GPP(FDD)和4G技术。此外,MAX5863还可在Tx和Rx模式之间切换,适用于TD - SCDMA、WCDMA - 3GPP(TDD)、IEEE 802.11a/b/g和IEEE 802.16等TDD应用。

在FDD模式下,ADC和DAC同时工作。ADC总线和DAC总线相互隔离,且必须分别连接到18位并行总线(8位ADC和10位DAC)的数字基带处理器。通过三线串行接口选择Xcvr模式,并使用转换时钟来锁存数据。在FDD模式下,当fCLK = 5.2MHz时,MAX5863的功耗为21mW 。这是ADC和DAC同时工作时的总功耗。

在TDD模式下,ADC和DAC独立工作。ADC和DAC总线可连接在一起,形成一个10位并行总线,连接到数字基带处理器。通过三线串行接口,在Rx模式下使能ADC,在Tx模式下使能DAC。在Rx模式下工作时,DAC不传输数据,其内核被禁用,ADC总线处于三态,这样可消除任何不需要的寄生发射,防止总线竞争。在TDD模式下,当fCLK = 5.2MHz时,MAX5863在Rx模式下的功耗为14mW,Tx模式下DAC的功耗为5mW。

-

MAX5863:超低功耗、高动态性能的7.5Msps模拟前端2026-03-26 210

-

MAX5866超低功耗、高动态性能、60Msps模拟前端技术手册2025-04-28 1201

-

超低功耗模拟前端集成电路MAX19708相关资料分享2021-05-17 1437

-

超低功耗模拟前端MAX19706相关资料下载2021-05-14 818

-

超低功耗高度集成的模拟前端MAX5865电子资料2021-04-20 1336

-

10位45Msps超低功耗模拟前端MAX19707资料推荐2021-04-02 1432

-

75Msps超低功耗模拟前端MAX19700资料推荐2021-04-01 728

-

MAX19700中文资料pdf2008-04-23 534

全部0条评论

快来发表一下你的评论吧 !