cadence allegro16.3常见问题解答

EDA/IC设计

描述

1. Allegro中我设置了highlight的颜色为白色,但选中后颜色是白蓝相间的,很不方便查看。是什么地方需要设置,哪位大虾告诉哈我?

答:setup/user preferences/display/display_nohilitefont 这个选项打勾就行了。

2. 不小心按了Highlight Sov后部分线高亮成白色,怎样取消?

答:这个是用来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地网络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight高亮默认颜色?

答:可以在Display-》Color/Visibility-》Display-》Temporary Highlight里修改即可,临时修改颜色可以点Display-》Assign Color来实现。

4. 如实现Highlight高亮部分网络,而背景变暗,就像Altium Designer那样?

答:可以在Display-》Color/Visibility-》Display-》Shadow Mode打开该模式,并且选中Dim active layer即可。

5. 快速切换层快捷键

答:可以按数字区里的“-”或“+”来换层。

6. OrCAD跟Allegro交互时,出现WARNING [CAP0072] Could not find component to highlight错误等?

答:OrCAD输出网表,Allegro导入网表,确保两者对的上号,然后在Orcad选中元件,再右键Editor Select,即可在Allegro中选中该元件;反过来,在Allegro中要先Highlight某元件,在Orcad中变会选中该元件。

1.ORcad :首先打开orcad和allegro分别占1/2的窗口界面。然后orcad中 Tools/creatnetlist/PCB Editor中Create PCB Editor Netlist下的Options中设置导出网表的路径。然后确定导出网表。

2.Allegro:Files/Import/Logic/ 最底下的Import directory中设置刚才导出网表的路径。然后导入即可,只要不出现error即可。

3.操作互动:首先在allegro中选中高亮display/Highlight,然后到orcad中选中一个元件或者引脚哪么对应的allegro中旧高亮显示了。当然了选中Dehighlight就可以不高亮显示了。

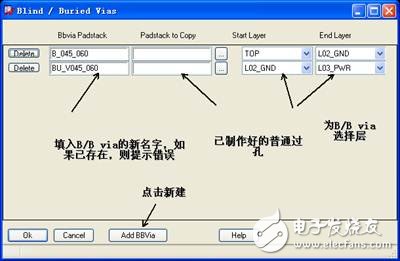

7. 关于盲孔及埋孔B/B Via的制作方法?

答:可先制作通孔Thru via,然后Setup-》B/B via definitions-》Define B/B via,如下图,完成后,再在Constraint Manager-》Physical-》all layers-》vias里添加B/B Via即可。

8. 在用Router Editor做BGA自动扇出时,遇到提示无法找到xxx解决方法?

答:路径里不能有中文或者空格 。

9. 在制作封装时,如何修改封装引脚的PIN Number?

答:Edit-》Text,然后选中PIN Number修改即可。

10. 对于一些机械安装孔,为什么选了pin后,选中老是删除不了?

答:因为这些Mechanical Pin属于某个Symbol的,在Find里选中Symbols,再右键该机械孔,点Unplace Component即可。

11. 在OrCAD里用Off Page Connector为什么没起到电气连接的作用?

答:先科普下:

1.off_page connector确实是用在不同页间比较合适,同一页中可以选择用连线,总线或者Place net alias来连通管脚,没有见过在同一页中用off_page connector的。

2.off_page connector在电气特性上是没有方向性的,但是在制图时,为了人看方便,所以使用的双向信号和单向信号的符号还是不同的,这是为了让人知道它是输入还是输出。电气特性的连接是在芯片做原理图封装时,对管脚定义时形成的。

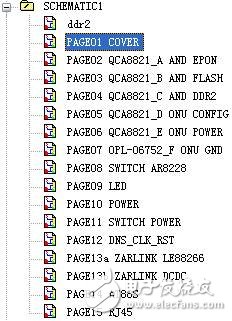

原因分析:Off Page Connector用于平坦式电路图中多页面原理图电气连接(这些原理图必须从属于同一个Parent Sheet Symbol)。如下图所示才算同一个Parent sheet symbol。

12. 如何将两块电路板合成一块?

答:先将电路板A导出成Sub-drawing,然后电路板B再导入该Sub-drawing,同时原理图也合成一个原理图,完后创建网表Netlist,电路板B再导入该Netlist,此时电路板B存在一些未名的器件和已名的器件,因为导入Sub-drawing元件布局跟连线都跟原来的保持一致,但是去掉了电路板A中元件的网表信息的,而导入该Netlist则导入了网表信息,为了利用原来的元件布局,可用Swap-》Component命令来交换元件网表信息而保持原来的布局不变。

13. 元件封装中的机械安装孔Mechanical Symbol?

答:使用Allegro PCB Design XL的Package symbol模板建立一个元件封装,对于有电气连接性的pin将其按照实际元件的引脚编号。而对于机械安装孔的pin,将其pin number删除掉,表明它是一个非电气连接性的引脚,大多数指安装孔。比如DB9、RJ45等接插件都具有两个(或者以上)的机械孔。

14. Mechanical Symbol已经存在库中,但Place-》Manually在Mechanical Symbols里见不到?

答:在Placement里的Advance Settings选项卡中选中Library即可。

15. ORCAD画原理图时,off page connector 后加上页码的方法?

答:用ORCAD画原理图,很多ORCAD的SCH中,大多在offpage connector 加上一个页码。方法很简单:Tools-》annotate-》action-》add intersheet reference即可。

16. 布线时,添加到约束中的所有的通孔和盲孔都可以显示,但是所有埋孔都不能显示,不知道为什么。比如,L1—L2,L1--L3, L1--L8(8层板)都可以显示,但是L2——L7,L3--L6都无法显示?

答:在pad制作时需要把microvia点上即可。

17. Allegro Region区域规则设置?

答:setup - constraints - constraint manager或者快捷菜单中带cm标记的,Cmgr图标启动constraints manager图表窗体,在窗体中选择object--》create--》region,此后就在表中设置一下物理或者间距规则,只不过在设置通孔时可以双击弹出选择过孔窗体,非常方便。最后设置完了点击OK,此后在allegro pcb的菜单中shape下有利用Rectangular建立一个矩形,然后在option中的active class 选择Constraint Region,subclass选择all.assgin to region选择你刚刚在规则管理中建立的区域规则名称,如果没有说明你没有保存好,重新操作一遍以上的规则建立过程。

18. 与某个Symbol的引脚相连的Clins和Vias删除不了?

答:可能该Symbol为fix,Unfix该Symbol即可。

19. Allegro使用Fanout by pick功能时老是扇不出,而且停到一半卡死?

答:可能待扇出Symbol所在区域中存在Etch层的Shape,要删掉这些Shape才行。

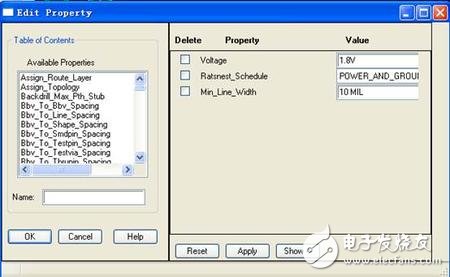

20. 将某个网络设置成电源网络,并设置其电压、线宽等属性?

答:选中该Net,然后Edit-》Properties,按下图修改其属性即可。或者也可以依次点击Tools-》Setup Advisor-》Next-》Next-》Identify DC Nets-》填入网络的Voltage即可。

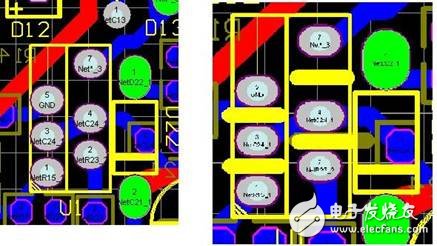

21. 为什么器件bound相互重叠了,也不显示DRC错误呢?是不是哪里设置要打开以下?

3 u# n/ O$ F1 d3 @# l. |答:有两种,一个是pin到pin的距离约束,主要是防止短路,需要在constrain中设置smd pin 到smd pin的距离,然后在setup——constrain——modes中的spacing modes中勾选smd pin to smd pin。

另外一个是检查两个器件是否重叠,需要用到place bound top/bottom,至于是顶层还是底层,要更具你的器件而定,这个规则只要是两个器件的place bound层相互重叠就会报警,同样需要打开检查开关,在setup——constrain——modes中的design modes(package)中勾选package to package为on(其中on为实时监测,只要触犯规则就报警,batch为只有点击update drc才监测报警,off是不监测,违反规则不报警)。当然,Color/Visibility中Stack-UP中相应层中的DRC显示也要开启。

22. 拖动时为什么不显示鼠线?移动铺铜或元件时,原来与之相连的过孔和线都消失了,怎么解决?

答:Move时要选中Ripup Etch。选中Ripup Etch时将去掉跟该Symbol引脚相连的Clines,同时显示Rats,选中Stretch Etch时用Clines代替Rats,而什么都不选时则保留Clines同时显示Rats。所以移动铺铜或元件为保留原来的过孔和线,则不能选中Ripup Etch。

另外:定制Allegro环境

Find(选取)

Design Object Find Filter选项:

Groups(将1个或多个元件设定为同一组群)

Comps(带有元件序号的Allegro元件)

Symbols(所有电路板中的Allegro元件)

Functions(一组元件中的一个元件)

Nets(一条导线)

Pins(元件的管脚)

Vias(过孔或贯穿孔)

Clines(具有电气特性的线段:导线到导线;导线到过孔;过孔到过孔)

Lines(具有电气特性的线段:如元件外框)

Shapes(任意多边形)

Voids(任意多边形的挖空部分)

Cline Segs(在clines中一条没有拐弯的导线)

Other Segs(在line中一条没有拐弯的导线)

Figures(图形符号)

DRC errors(违反设计规则的位置及相关信息)

Text(文字)

Ratsnets(飞线)

Rat Ts(T型飞线)

文件类型:

.brd(普通的电路板文件)

.dra(Symbols或Pad的可编辑保存文件)

.pad(Padstack文件,在做symbol时可以直接调用)

.psm(Library文件,保存一般元件)

.osm(Library文件,保存由图框及图文件说明组成的元件)

.bsm(Library文件,保存由板外框及螺丝孔组成的元件)

.fsm(Library文件,保存特殊图形元件,仅用于建立Padstack的Thermal Relief)

.ssm(Library文件,保存特殊外形元件,仅用于建立特殊外形的Padstack)

.mdd(Library文件,保存module definition)

.tap(输出的包含NC drill数据的文件)

.scr(Script和macro文件)

.art(输出底片文件)

.log(输出的一些临时信息文件)

.color(view层面切换文件)

.jrl(记录操作Allegro的事件的文件)

设定Drawing Size(setupDrawing size.。。.)

设定Drawing Options(setupDrawing option.。。.)

status:on-line DRC(随时执行DRC)

Default symbol height

Display:

Enhanced Display Mode:

Display drill holes:显示钻孔的实际大小

Filled pads:将via 和pin由中空改为填满

Cline endcaps:导线拐弯处的平滑

Thermal pads:显示Negative Layer的pin/via的散热十字孔

设定Text Size(setupText Size.。。.)

设定格子(setup grids.。。)

Grids on:显示格子

Non-Etch:非走线层

All Etch:走线层

Top:顶层

Bottom:底层

设定Subclasses选项(setupsubclasses.。。)

添加删除 Layer

New Subclass.。

设定B/Bvia(setupViasDefine B/Bvia.。。)

Ripup etch:移动时显示飞线

Stretch etch:移动时不显示飞线

信号线的基本操作:

更改信号线的宽度(EditChangeFindClines)optionlinewidth

删除信号线(EditDelete)

改变信号线的拐角(EditVertex)

删除信号线的拐角(EditDelete Vertex)

23. 如何修改某个Shape或Polygon的网络属性以及边界?

答:Shape-》Select Shape or void-》单击选中该Shape-》在右边Option栏Assign net name中将Dummy Net修改成自己想要的网络,当鼠标光标停留在边界时可以拖动光标修改边界。

24. 如何只删除某一层里的东西?

答:很简单,Display-》Color/Visibility-》单独显示要想删除的那一层,OK后删除即可。

25. 如何替换某个过孔?如何不在布线状态下快速添加过孔?

答:Tools-》PadStack-》Replace,然后必须选上Single via replace mode,最后选上要想替换的过孔即可;利用copy来快速添加大量过孔即可。

26. 如何在allegro中取消Thermal relief花焊盘(十字焊盘)

答:set up-》design parameter -》shape-》edit global dynamic shape parameters-》Thermal relief connects -》Thru pins ,Smd pins -》 full contact

27. 在等长走线时,如何更改target目标线?

答:绕等长有两种:一种是设在一定范围内绕没有基准,就是说在一组BUS里必须绕到这个范围内才会变绿,这个我一般不用,因为BUS里少绕一根不到这个范围就不会变绿。另一种就是设在一定范围内有基准的,也许就是你表达的这种,ElectricalConstraint Set-->Net-->Routing-->Relative Propagation-->relative Delay-->Delta:Tolerance下你想设做基准的Net,点鼠标右键,在下拉菜单选择set as target。

28. 如何分割电源层?

答:使用Anti Etch来分割平面

使用Add-》line命令,并且设置Active Class为Anti Etch,设置好线宽,并且在外框画好RoutKeepin,然后在已经建立Shape的平面上,画出想要分隔的范围,再用Edit-》Split Plane-》Create。

29. 画了line型线,如何修改?

答:Edit-》Vertex(顶点)命令来修改。

30. 通孔式焊盘做得比较大,且排列的较密集,怕连锡怎么办?

答:焊盘间画丝印做隔离。

31. allegro对齐的问题

答:1.首先右键application mode切换到模式placement edit;

2.框选需要对齐的元件;

3.关键的一步,在你要对齐的基准元件上右键,选择align components;OK

4.allegro只能实现这个中心点对齐,至于更高级的要使用skill了

32. 修改了元器件封装,如何更新到PCB?

答:Place-》Update Symbols-》Package Symbols-》找到该封装-》点击Refresh即可。

33. Allegro如何添加机械孔?

答:孔径为NPTH(None Plated Through Hole),焊盘为NULL,THERMAL RELIEF和ANTI PAD需比孔径大20MIL左右。然后把它当做via来用就可以了,当然也可以做成Symbol来添加。

34. 画封装时如何将元件参考点设在中间?

答:画好封装后,Setup-》designer parameters-》Move Orign即可。

35. 在Allegro中如何更改字体和大小(丝印,位号等)

配置字体:

allegro 15.2:

setup-》text sizes

text blk:字体编号

photo width: 配置线宽

width,height:配置字体大小

改变字体大小:edit-》change,然后在右边控制面板find tab里只选text(只改变字体)

然后在右边控制面板options tab里line width添线的宽度和text block里选字体的大小。

最后选你准备改变的TEXT。

框住要修改的所有TEXT可以批量修改

allegro 16.0: setup-》design-》parameter-》text-》setup text size

text blk:字体编号

photo width: 配置线宽

width,height:配置字体大小

改变字体大小:

edit-》change,然后在右边控制面板find tab里只选text(只改变字体)

然后在右边控制面板options tab里line width添线的宽度和text block里选字体的大小。

class-》ref des-》new sub class-》silkscreen_top

最后选你准备改变的TEXT,框住要修改的所有TEXT可以批量修改,

注意:

如果修改顶层丝印要先关掉底部丝印层,silkscreen_bottom和display_bottom

--------------------------------------------------------------------

在建封装的时候可以设定

36. Allegro静态铺铜时,当用Shape void Element来手动避让时,有些区域明明很宽但老是进不去以致导致出现孤岛?

答:在用Shape Void Element命令时,选中Shape,右键Parameter,Void Controls-》Creat Pin voids,将In-Line改为Individually即可。

37. 重叠元件,如何切换选中它们?

答:选中该最上面元件,按Tab逐层切换选中。

38. 画封装的时候,明明已经在某些层上有定义,如Rout Keepout等,但是调用元件到板上却老是找不到该层?

答:可能有两个原因:1、PCB板上没显示该层;2、画封装的时候,如Top层定义成“Top_Cond”,但PCB上却定义成“TOP”,所以显示不出来。

39. 动态铺铜时,Update to Smooth但还是存在Out of date shapes,什么原因?

答:可能存在一些dummy net 的shapes,可以通过在Report里运行Shape dynamic state来找到这些shapes,又因为dummy net的shapes可能不会就这样显示出来,可以stack-up里boundary那栏打开,用shape select来选中它来删除。

40. Package Geometry 里的Silkscreen画的是封装的外框,Component Geometry里的Silkscreen是器件的编号文本如R1等。

41. Place_Bound_Top

Used to ensure you don’t place components on top of each without getting a DRC. This boundary normally defines the component area which may or may not include pins of surface mount devices. This boundary can also be assigned a component high to be verified at the board level and checked to the Package_Keepout_Top boundaries or any other special component clearances. If this boundary does not exist than it will be automatically created based on the Assembly_Top outline and the outer extents of the component pins. This boundary can only be defined at the symbol level (.dra)。

Dfa_Bound_Top

Used by the Real Time Design for Assembly (DFA) Analysis to check clearances between components driven by a Spreadsheet based matrix of components. This boundary normally or can be different then the traditional Place_Bound_Top boundary and it may include pins of surface mount devices. If this boundary does not exist than the DFA checks default to using the Place_Bound_Top boundary. This boundary can only be defined at the symbol level (.dra)。

Package_Keepout_Top

Used to ensure you don’t violate placement keepout areas or high restricted area in a design. This boundary can only be defined at the board level (.brd) and cannot be added to the symbol level (.dra) unless it is part of a Mechanical Symbol (.bsm)

42. allegro导出库时,no library dependencies选项有什么用?

答:选中该选项,导出库时会连同焊盘一起导出去。

43. Constraints manager里无法建立pin pair?

答:有可能是虽然已经给电阻、电容等器件建立Espice模型了,但是IC的pin脚IO属性没定义。可以编辑pin脚的属性,找到pinuse项,在里面更改即可。

SI仿真时,提示can’t open xx/xx/xx/cycle.msm是怎么回事?

答:肯定是.brd文件的路径或文件名本身有空格。

SI仿真时,提示“part with invalid parameter values exist in the topology”怎么解决?

答:可能是TL的velocity参数没添加上。

Allegro布线时,等长走线很慢、很卡?

答:肯定是开了constraints manager,关掉即可。

Orcad使用层次原理图作图时,对于顶层原理图中的block跟其所对应的子原理图中port修改后如何快速同步?

答:当修改了原理图中的port时,回到顶层原理图,找到其所对应的block,右键选择synchronize up(向上同步),即可将port更新到block。Synchronize down则刚好相反。

Constraints Manager里等长布线时,Relative Propagation Delay里没有显示走线长度及误差信息?

答:可以试试打开Online DRC,并且Update DRC.

如何查看Packetage使用了哪几个pad?

答:在allegro里找到Tools-》Quick Reports-》PadStack Usage Report,在里面搜索即可。

orcad/pspice安装报runtime error r6034错误或缺少.dll文件的解决方法

答: Microsoft Visual C++ Runtime library

Runtime Error!

Program :D:CadenceSPB_15.7toolscapturecapture.exe

R6034

An application has made an attempt to load the C runtime library incorrectly.

Please ccontact the application‘s support team for more information!

解决方法:

1.在“我的电脑”上右键,选择属性,然后选择“高级”,再点击进入“环境变量”

2.在“系统变量”中找到“PATH”项,我的PATH键值如下:

原来的:

E:MentorGraphics9.3PADSSDD_HOMEcommonwin32bin;E:MentorGraphics9.3PADSSDD_HOMEcommonwin32lib;%SystemRoot%system32;%SystemRoot%;%SystemRoot%System32Wbem;%QUARTUS_ROOTDIR%bin;e:MENTOR~1LICENS~1;%MGC_HOME%/bin;%MGC_HOME%/lib;%MGC_HOMEBS%bin;%MGC_HOMEBS%lib;%CDSROOT%toolsbin;%CDSROOT%toolslibutilbin;%CDSROOT%toolsfetbin;%CDSROOT%toolspcbbin;%CDSROOT%toolsspecctrabin;%CDSROOT%toolsPSpice;%CDSROOT%toolsPSpiceLibrary;%CDSROOT%toolsCapture;%CDSROOT%OpenAccessbinwin32opt

修改后的:

%CDSROOT%toolsbin;%CDSROOT%toolslibutilbin;%CDSROOT%toolsfetbin;%CDSROOT%toolspcbbin;%CDSROOT%toolsspecctrabin;%CDSROOT%toolsPSpice;%CDSROOT%toolsPSpiceLibrary;%CDSROOT%toolsCapture;%CDSROOT%OpenAccessbinwin32opt;E:MentorGraphics9.3PADSSDD_HOMEcommonwin32bin;E:MentorGraphics9.3PADSSDD_HOMEcommonwin32lib;%SystemRoot%system32;%SystemRoot%;%SystemRoot%System32Wbem;%QUARTUS_ROOTDIR%bin;e:MENTOR~1LICENS~1;%MGC_HOME%/bin;%MGC_HOME%/lib;%MGC_HOMEBS%bin;%MGC_HOMEBS%lib

也就是把所有cadence的变量全部放到前面就行了。

orCAD里面怎样批量修改器件的属性?

答:在project页面里选中”xxx.dsn”,右键选择Edit Object Properties,进去后再右键选择pivot可切换列表布局。

LP Wizard做PCB库的时候为什么做出来的库没有焊盘的?

答:肯定是没设置allegro里Pad的路径了,导致LP Wizard用skill调用allegro时找不到焊盘。

做PCB库时,一般需要在哪些层做处理?

答:无电气层外框 (Packetage Geometry-》Place_Bound_Top)

器件高度 (Setup-》Areas-》Package Height)

装配层外框 (Packetage Geometry-》Assembly_top)

元件丝印层外框 (Packetage Geometry-》Silkscreen_top)

参考编号在丝印层(Ref Des-》Silkscreen_top)和装配层(Ref Des-》Assembly_top)

元器件类型 (Device Type-》Assembly_Top)可选

做PCB库时,如果修改了焊盘,那怎样将封装库里焊盘更新到最新状态?

答:打开.dra,Tools-》Padstack-》Refresh即可。

快速切换act层跟alt层?

答:在env里设置快捷键添加以下文本即可用F2键快速切换了。

alias F2 pop swap

用Allegro SI仿真的时候,DDR3跑的是800MHz,所以我CLK设的是400MHz,您所在Stimulus Edit中的Switch At选BOTH,这样跑出来的才是正确的。打开switch at的方法是:在Stimulus State栏中选Custom选项,Stimulus Type里面选择SYNC,在下面的Stimulus Editing栏就可以看到Switch At选项。

当使用层次式设计时,导出物料清单要选中use occurrences(preferred) ,而不是use instances(使用当前属性)。否则可能出现器件编号不对的状况。

当back annotation反标失败的时候,可再重新对整个design来一次annotation,甚至是先复位所有编号,再无条件编号,平铺式选instances跟occurrences没关系,层次式必须选择occurrences。然后brd导出logic,orcad再反标一次即可。

铺静态铜完成后最好fix下,否则split planes时可能会导致之前的覆铜丢失。

Allegro老是提示dynamic shapes里有out of date shapes怎么办?

答:肯定是用画anti etch线的方法分割电源层,但分割得太碎,导致一些外面的dummy net的shapes被自动删掉而留下一些boundaries,没分割一次,boundary就增多,所以可以看到out of date shapes会增多。这时单纯删除shape是不行的,要在color/visibility里将bound.这一栏显示才行。

不小心将所有覆铜删掉后,导致之前打的接到低上的过孔全都变成dummy net了,有没有办法可以批量修改这些过孔的网络接到地呢?

答:先铺上GND属性的dynamic copper;

选中所有过孔,然后移动到板外面,不要选中rip up,最好用ix 命令,方便待会儿移回到原来的位置;

然后再用ix命令移回到原来的位置,此时刚才的无网络连接属性的过孔将会自动打上网络属性。

44. SI仿真时,提示can’t open xx/xx/xx/cycle.msm是怎么回事?

答:肯定是.brd文件的路径或文件名本身有空格。

45. SI仿真时,提示“part with invalid parameter values exist in the topology”怎么解决?

答:可能是TL的velocity参数没添加上。

46. Allegro布线时,等长走线很慢、很卡?

答:肯定是开了constraints manager,关掉即可。

47. Orcad使用层次原理图作图时,对于顶层原理图中的block跟其所对应的子原理图中port修改后如何快速同步?

答:当修改了原理图中的port时,回到顶层原理图,找到其所对应的block,右键选择synchronize up(向上同步),即可将port更新到block。Synchronize down则刚好相反。

-

Keystone NDK常见问题解答2024-10-11 523

-

TFPxxx常见问题解答2024-09-29 465

-

TMP LM 75比较常见问题解答2024-08-30 520

-

CLOCK常见问题解答2023-11-23 677

-

CAN总线常见问题解答2021-12-27 2822

-

PDIUSBD12常见问题解答资料下载2021-05-14 1264

-

AN-1291:数字电位计:常见问题解答2021-03-19 1201

-

英飞凌IGBT应用常见问题解答2018-12-13 10339

-

Allegro16.3速成2016-12-14 713

-

PC 音质常见问题解答2010-08-02 652

-

新手-iPhone/touch常见问题解答2010-02-02 610

-

钒电池常见问题解答2009-11-20 1962

-

TOPSwitch-HX常见问题解答2009-04-27 849

-

VxWorks常见问题解答2009-03-28 599

全部0条评论

快来发表一下你的评论吧 !