AD9957 1 GSPS正交数字上变频器,内置18位IQ数据路径和14位DAC技术手册

描述

概述

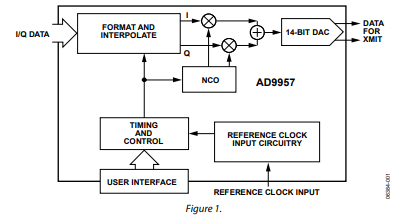

AD9957可用作通用I/Q调制器与捷变上变频器,适合视成本、尺寸、功耗和动态性能为关键因素的通信系统。它在单芯片上集成了一个高速直接数字频率合成器(DDS)、一个高性能、高速14位数模转换器(DAC)、时钟乘法器电路、数字滤波器以及其它DSP功能,为有线或无线通信系统中的数据传输提供基带上变频。

AD9957是正交数字上变频器(QDUC)系列中的第三款器件,另外两款器件是AD9857和AD9856。它的工作速度、功耗和频谱性能均有所提升。与前两款产品不同,它支持可用于I/Q基带数据的16位串行输入模式。或者,也可以对这款器件进行编程,用作单音正弦源或插值DAC。

基准时钟输入电路含有一个晶体振荡器、一个高速二分频输入和一个低噪声锁相环(PLL),锁相环用于倍增基准时钟频率。

控制功能的用户接口包括一个串行端口和引脚分布,前者经过配置很容易与Blackfin® DSP的SPORT接口,后者可以用来对任何信号参数(相位、频率或振幅)进行快速、轻松的移动键控。

数据表:*附件:AD9957 1 GSPS正交数字上变频器,内置18位IQ数据路径和14位DAC技术手册.pdf

应用

- HFC数据、电话和视频调制解调器

- 无线基站传输

- 宽带通信传输

- 网络电话

特性

- 1 GSPS内部时钟速度(高达 400 MHz模拟输出)

- 集成1 GSPS、14位DAC

- 输入数据速率:250 MSPS

- 相位噪声 ≤ −125 dBc/Hz(1 kHz偏移,400 MHz载波)

- 卓越的动态性能:>80 dB 窄带 SFDR

- 8个可编程配置文件,支持移位键控

- Sin(x)/(x)校正(反正弦滤波器)

- 参考时钟倍频器

- 内部振荡器,支持单晶体操作

- 软件/硬件控制的关断功能

- 集成RAM

- 相位调制功能

- 多芯片同步

- 与Blackfin SPORT轻松接口

- 插值因子范围:4至252倍

- DAC插值模式

- 增益控制DAC

- 内部分频器支持高达2 GHz的参考频率

- 采用1.8 V和3.3 V电源供电

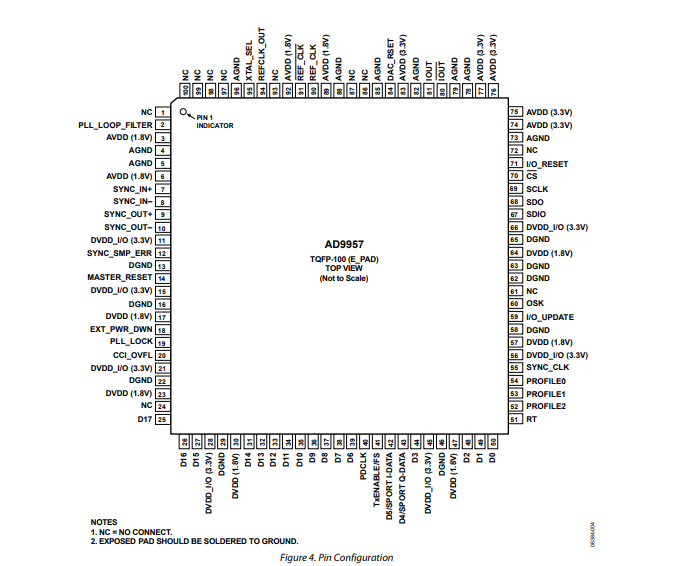

- 100引脚TQFP_EP封装

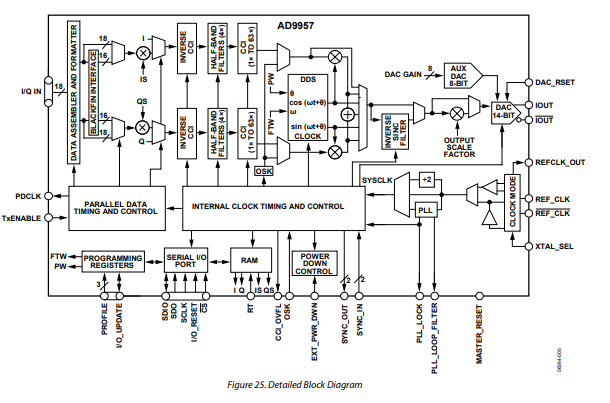

框图

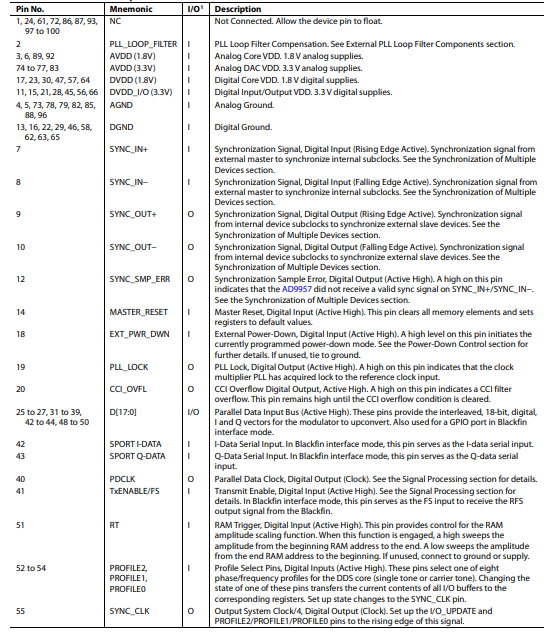

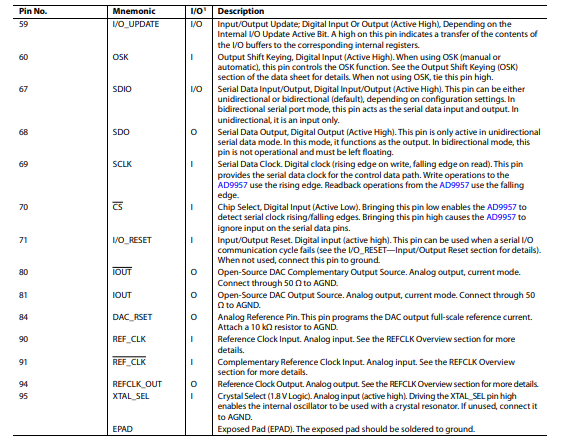

引脚配置描述

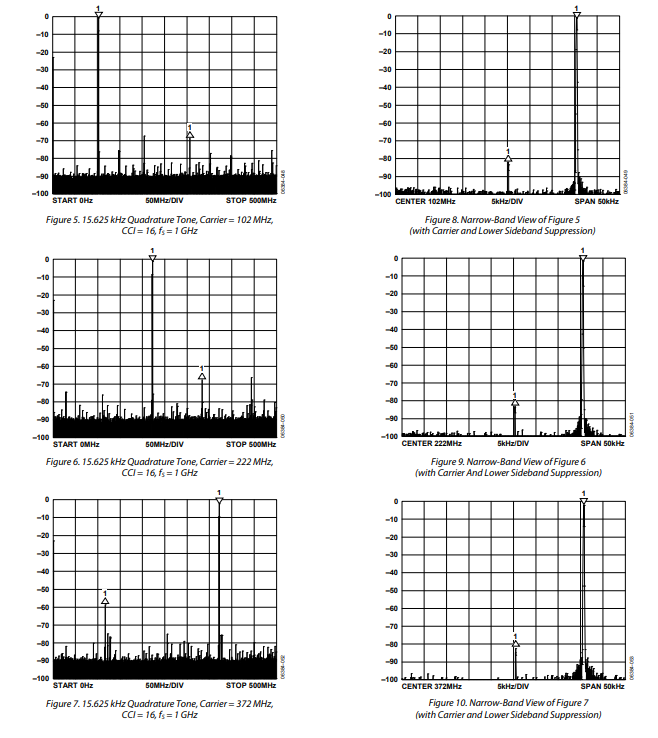

典型性能特征

工作模式

概述

AD9957 有三种基本工作模式:

- 正交调制(QQUC)模式(默认)

- 插值数模转换器(DAC)模式

- 单音模式

活动模式通过控制功能寄存器1(CFR1)中的工作模式位来选择。单音模式允许该器件作为一个正弦波发生器,直接由直接数字合成器(DDS)驱动数模转换器(DAC)。

插值数模转换器模式绕过直接数字合成器(DDS),使器件能够以低于数模转换器(DAC)的采样率传送基带数据。内部速率插值滤波器对用户数据进行滤波,并上采样至数模转换器(DAC)的采样率。这些滤波器共同提供了可编程的速率插值功能,同时抑制频谱镜像并保留原始基带频谱。

正交调制(QQUC)模式同时采用直接数字合成器(DDS)和速率插值滤波器。在这种情况下,两组并行的速率插值滤波器允许基带信号进行同相和正交(I/Q)信号处理,同时由直接数字合成器(DDS)提供载波进行信号调制。AD9957的详细框图如图25所示。

反sinc滤波器在这三种模式下均可用。

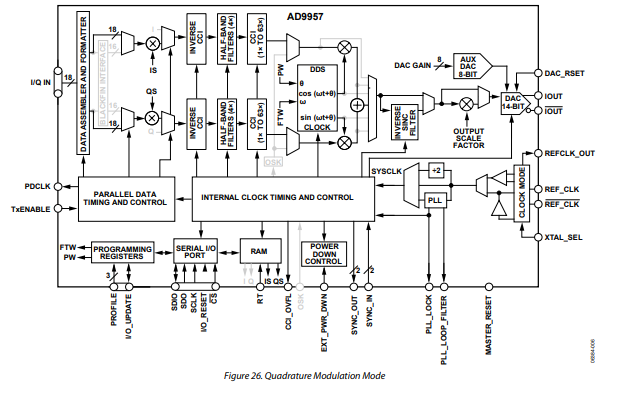

正交调制模式

AD9957 在 QDUC 模式下工作的框图如图 26 所示,灰色项目处于非活动状态。并行输入接受 18 位 I 字和 18 位 Q 字,二者在时间上是交错的。也就是说,先是一个 18 位 I 字,接着是一个 18 位 Q 字,然后下一个 18 位 I 字,依此类推。这两个 18 位 Q 字共同构成一个内部样本。数据在累加器和格式化器中进行解交错,使得每个样本在并行数据路径中沿各自的 I 和 Q 通道以并行方式传播。I 和 Q 数据均处于活动状态;并行数据时钟(PDCLK)用于同步 I/Q 数据输入到 AD9957 中。

PROFILE0、PROFILE1、PROFILE2 和 I/O_UPDATE 引脚也与 PDCLK 同步。

直接数字频率合成器(DDS)内核提供正交(正弦和余弦)本地振荡器信号给正交调制器,在此处,经过插值的 I 和 Q 样本分别与载波的相应相位相乘并求和,从而产生正交调制数据流。该数据流通过反 sinc 滤波器(可选),然后经过缩放乘法器。接着,它被应用于 14 位数模转换器(DAC),以产生正交调制的模拟输出信号。

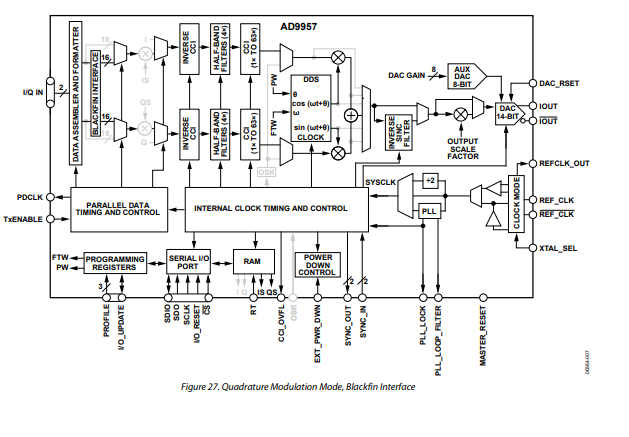

#黑鳍接口(BFI)模式

黑鳍接口(BFI)模式是正交调制(QDUC)模式的一个子集,如图27所示,灰色项目处于非活动状态。在这种模式下,一个单独的16位串行比特流被应用于基带数据端口以替代并行数据字。这两个串行输入提供16位的I和Q字(与正常的QDUC模式中18位字不同)。串行比特流通过PDCLK信号输送到黑鳍接口。黑鳍接口将16位串行数据转换为16位并行数据,以在系统时钟中传播并行数据链。

黑鳍接口在I和Q基带路径中都包含一对额外的半带滤波器(图中未明确显示)。这两个半带滤波器将基带数据的插值因子相对于正常的QDUC模式提高四倍。

串行数据的同步通过PDCLK信号实现。在BFI模式下,PDCLK信号实际上是位时钟,用于串行数据。请注意,在BFI模式下系统时钟限制为750 MHz。

-

AD9857:高性能CMOS 200 MSPS 14位正交数字上变频器2026-04-16 58

-

AD9163:高性能16位RF DAC与数字上变频器的深度解析2026-04-10 136

-

AD9857 CMOS 200 MSPS、14位正交数字上变频器技术手册2025-04-30 1203

-

1 GSPS正交数字上变频器,内置18位IQ数据路径和14位DAC-CBM99D572024-11-11 2058

-

AD9957正交数字上变频器介绍2023-02-01 4701

-

AD9163:16位、12 GSPS、RF DAC和数字上变频器数据表2021-04-23 876

-

AD9957: 内置14位DAC的1 GSPS正交数字上变频器2021-03-22 973

-

AD9957:内置18位I/Q数据路径和14位DAC的1GSPS正交数字上变频器 数据手册2021-03-19 1157

-

基于STC12C5410单片机和AD9957实现雷达上变频器的设计2020-12-28 6095

-

数字上变频器IC调制复杂调制2019-07-22 1356

-

AD9957 1 GSPS正交数字上变频器,内置18位IQ数据路径和14位DAC2019-02-22 1255

-

基于数字上变频器的中频调制器2011-07-11 4456

-

基于QDUC的雷达上变频电路的设计2010-12-29 1217

-

数字正交上变频器AD98572009-04-22 970

全部0条评论

快来发表一下你的评论吧 !