AD9856 CMOS 200MHz正交数字上变频器技术手册

描述

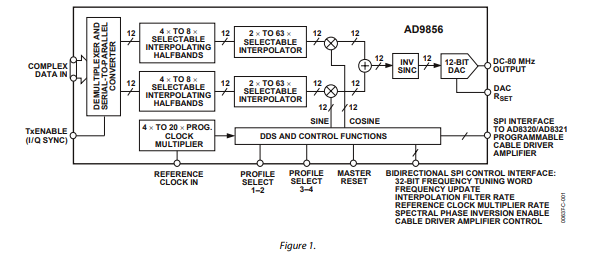

概述

AD9856在单芯片上集成了一个高速直接数字频率合成器(DDS)、一个高性能、高速12位数模转换器(DAC)、时钟乘法器电路、数字滤波器以及其它DSP功能,构成一个完整的正交数字上变频器。它主要用作通用上行与下行I/Q调制器,适合视成本、尺寸、功耗和动态性能为关键因素的交互式HFC电缆网络应用。

数据表:*附件:AD9856 CMOS 200MHz正交数字上变频器技术手册.pdf

特性

- 通用低成本调制器解决方案,适合通信应用

- 输出带宽:DC至80 MHz

- 集成12位数模转换器

- 可编程采样速率插值滤波器

- 可编程基准时钟乘法器

- SIN(x)/x内部补偿滤波器

- 无杂散动态范围(SFDR):大于52 dB (40 MHz AOUT)

- +3 V单电源供电

- 无杂散动态范围(SFDR):大于48 dB (70 MHz AOUT)

- 窄带无杂散动态范围(SFDR):大于80 dB (70 MHz AOUT)

- 节省空间的表面贴装封装

- 双向控制总线接口

框图

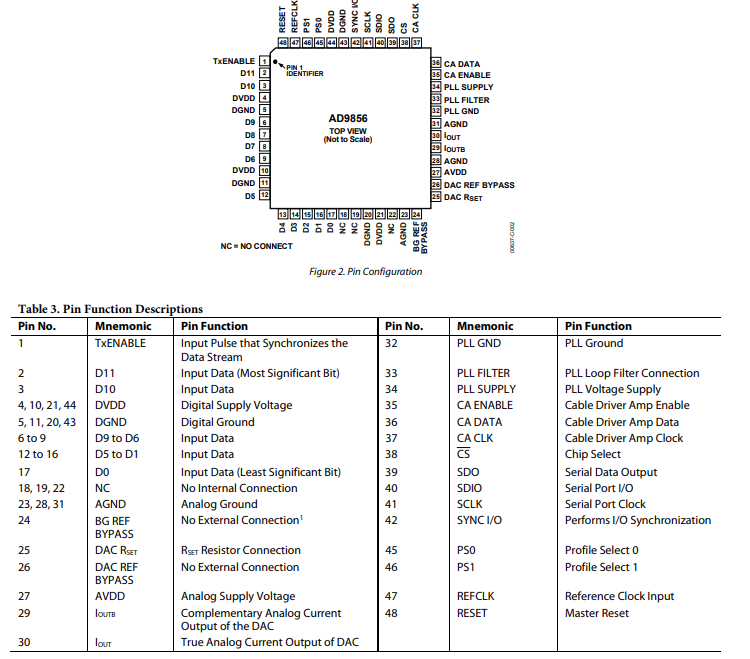

引脚配置描述

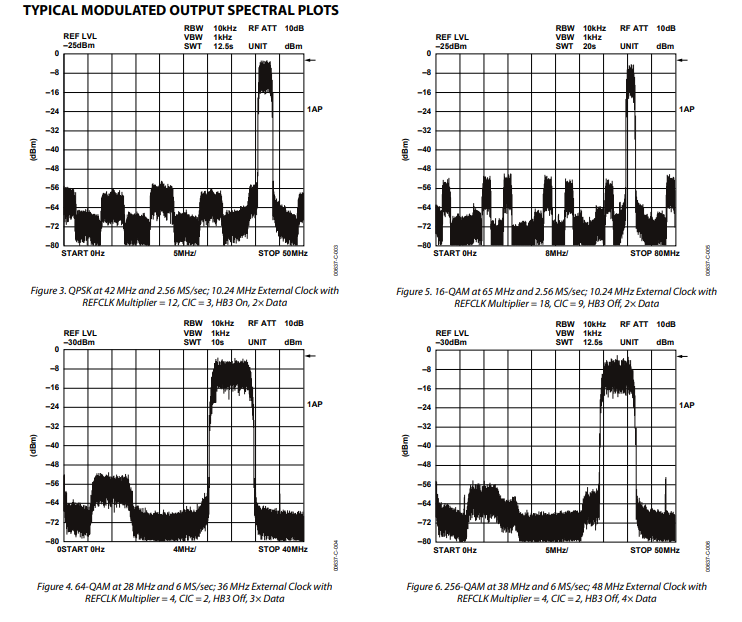

典型性能特征

工作原理

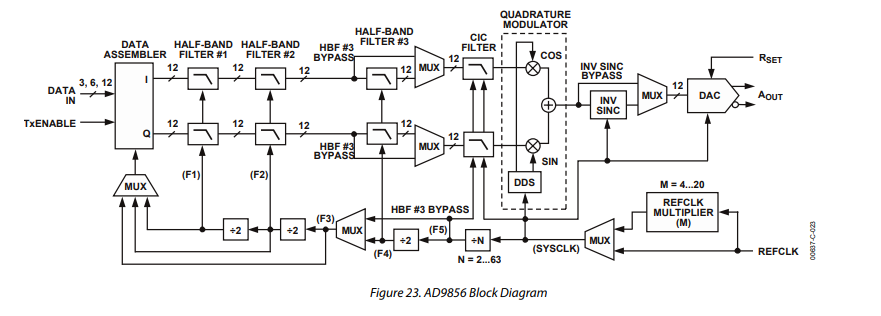

为了大致了解AD9856的功能,参考图23(该器件架构框图)会有所帮助。以下是对该器件功能的一般性描述。后续章节将详细介绍各个数据路径构建模块。

调制模式操作

AD9856接收12位数据字,这些数据字通过内部时钟选通进入数据汇编器。输入引脚TxENABLE起到阀门的作用,可根据数据汇编器的状态决定接受或忽略数据。用户可以选择将12位数据字作为单个12位字、双个6位字或四个3位字输入到AD9856中,这为用户提供了根据需求灵活使用较少接口引脚的方式。此外,输入到数据汇编器的交替12位字被视为符号的同相(I)和正交(Q)分量。

12位字输入到AD9856的速率称为输入采样率(f_{IN})。需注意,**f_{IN}**与基带数据的固定速率不同。相反,用户的基带数据在输入到AD9856之前至少需要进行两倍(×2)的上采样,以尽量减少与级联积分梳状(CIC)滤波器级相关的频率相关衰减(详见级联积分梳状滤波器部分)。

数据汇编器将输入的数据字对拆分为独立的I/Q数据流。I/Q数据字对出现在数据汇编器输出端的速率称为I/Q采样率(f_{IQ})。由于两个12位输入数据字用于构建离散的I和Q数据路径,所以输入采样率是I/Q采样率的两倍(即,f_{IN} = 2 × f_{IQ})。

数据汇编器的用户可以选择将12位数据字输出到AD9856,其输出采样率为$8 × f_{IQ}$ 。

一旦通过数据汇编器,I/Q数据流会输入到两个半带滤波器(半带滤波器1和2)。这两个滤波器的组合使采样率提高四倍(×4)。因此,在半带滤波器2的输出端,采样率为$4 × f_{IQ}** 。除了提高采样率之外,半带滤波器还提供低通滤波特性,这是抑制上采样过程产生的频谱镜像所必需的。进一步的上采样可通过可选的第三个半带滤波器(半带滤波器3)实现。启用该滤波器时,总上采样因子为八(×8)。因此,如果选择半带滤波器3,输出采样率为$8 × f_{IQ}** 。

通过半带滤波器级后,I/Q数据流会输入到级联积分梳状(CIC)滤波器。该滤波器配置为插值滤波器,可实现2到63(含)之间任意整数倍的进一步上采样。与半带滤波器类似,CIC滤波器具有低通特性,同样用于抑制上采样过程产生的频谱镜像。

CIC滤波器之后的数字正交调制器级用于将输入数据流的基带频谱向上变频到所需的载波频率(此过程称为上变频)。载波频率由直接数字合成器(DDS)进行数字控制。DDS使用其内部参考时钟(SYSCLK)以高精度生成所需的载波频率。载波以正交方式(90°相位偏移)应用于I和Q乘法器并求和,从而产生已调制载波的数据流。请注意,输入数据的采样率已从输入采样率**f_{IN}**转换为SYSCLK的输出采样率(见图23)。

-

深入解析AD9856:CMOS 200 MHz正交数字上变频器的卓越性能与应用2026-04-16 416

-

AD9857 CMOS 200 MSPS、14位正交数字上变频器技术手册2025-04-30 1315

-

2400 MHz上变频器的资料分享2022-08-11 1305

-

上变频器2400MHz开源项目2022-07-26 822

-

数字上变频器芯片Tames复调制2021-05-11 889

-

AD9856:CMOS 200 MHz数字上变频器数据表2021-05-09 810

-

AD9957: 内置14位DAC的1 GSPS正交数字上变频器2021-03-22 995

-

AD9957:内置18位I/Q数据路径和14位DAC的1GSPS正交数字上变频器 数据手册2021-03-19 1188

-

数字上变频器IC调制复杂调制2019-07-22 1371

-

AD9856 CMOS 200 MHz正交数字上变频器2019-02-22 389

-

基于数字上变频器的中频调制器2011-07-11 4483

-

数字正交上变频器AD98572009-04-22 990

全部0条评论

快来发表一下你的评论吧 !