AD9164 16位、12 GSPS、RF DAC和直接数字频率合成器技术手册

描述

概述

AD9164是一款高性能16位数模转换器(DAC)和直接数字频率合成器(DDS),支持高达6 GSPS的更新速率。DAC内核基于一个四通道开关结构,配合2倍插值滤波器,使DAC的有效更新速率在某些模式下高达12 GSPS。高动态范围和带宽使这些DAC非常适合最严苛的高速射频(RF) DAC应用。

DDS由一组32个32位数控振荡器(NCO)组成,各带相位累加器。

与100 MHz串行外设接口(SPI)和快跳模式配合使用时,支持相位相干快速跳频(FFH)和几种模式以支持多种应用。

数据表:*附件:AD9164 16位、12 GSPS、RF DAC和直接数字频率合成器技术手册.pdf

在基带模式下,元件的宽模拟带宽能力和高动态范围相结合,在最小一个载波至最大1.791 GHz信号带宽的满量程频谱范围内可支持DOCSIS 3.1电缆基础设施合规性。2倍插值滤波器(FIR85)使AD9164能够针对较低数据速率和转换器时钟进行配置,以降低系统总体功耗和滤波要求。在Mix-Mode™操作模式中,AD9164可在高达7.5 GHz的二阶和三阶奈奎斯特区内重构RF载波,同时仍保持出色的动态范围。输出电流可以在8 mA至38.76 mA范围内进行编程。AD9164数据接口由最多八个JESD204B串行器/解串器(SERDES)通道组成,可对其通道速度和通道数进行编程,从而实现应用灵活性。

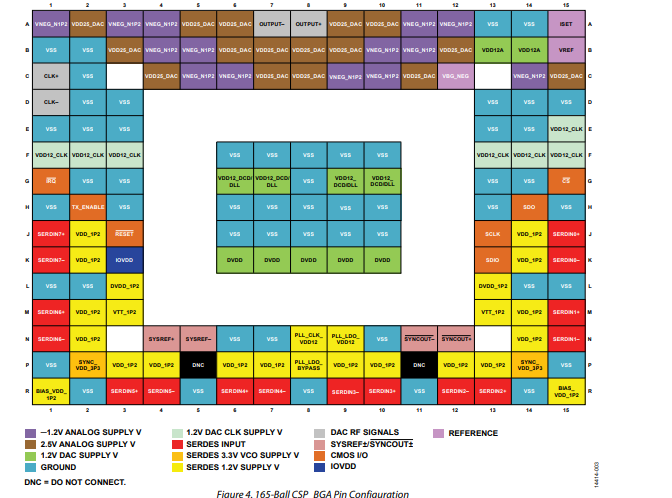

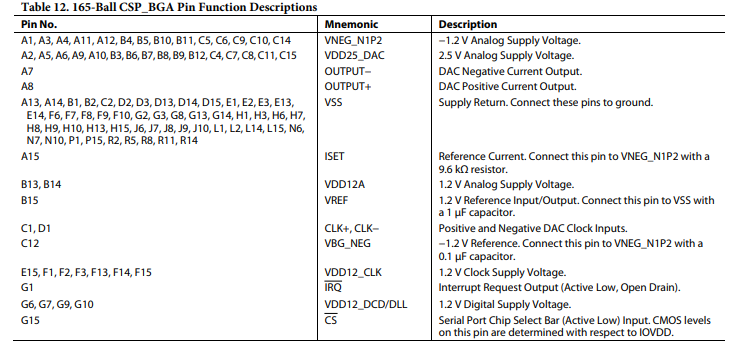

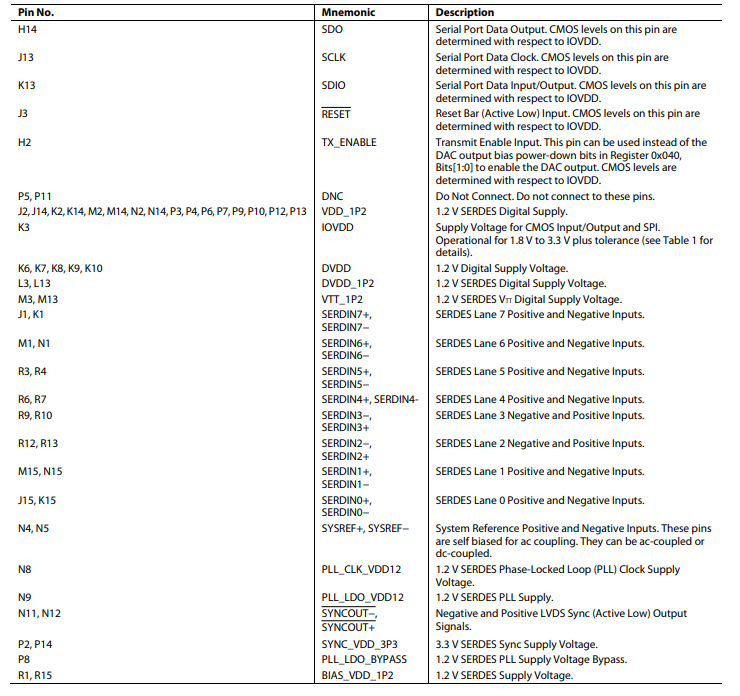

SPI接口可配置AD9164并监控所有寄存器的状态。AD9164提供165引脚、8 mm × 8 mm、0.5 mm间距CSP_BGA和169引脚、11 mm × 11 mm、0.8 mm间距、CSP_BGA两种封装,包括引脚选项。

应用

- 宽带通信系统

- DOCSIS 3.1电缆调制解调器终端系统(CMTS)/视频点播(VOD)/边沿正交幅度调制(EQAM)

- 无线通信基础设施

- W-CDMA、LTE、LTE-A、点对点

特性

- DAC更新速率高达12 GSPS(最小值)

- 6 GSPS直接RF频率合成(最小值)

- 直流至2.5 GHz(基带模式)

- 直流至6 GHz(2倍不归零(NRZ)模式)

- 1.5 GHz至7.5 GHz(混合模式)

- 旁通插值

- 2×、3×、4×、6×、8×、12×、16×、24×

- 出色的动态性能

- 快速跳频

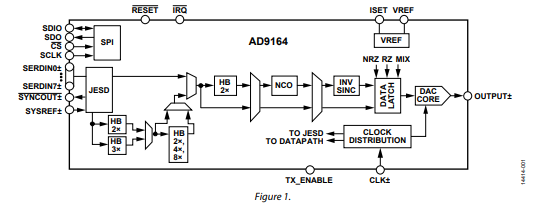

框图

引脚配置描述

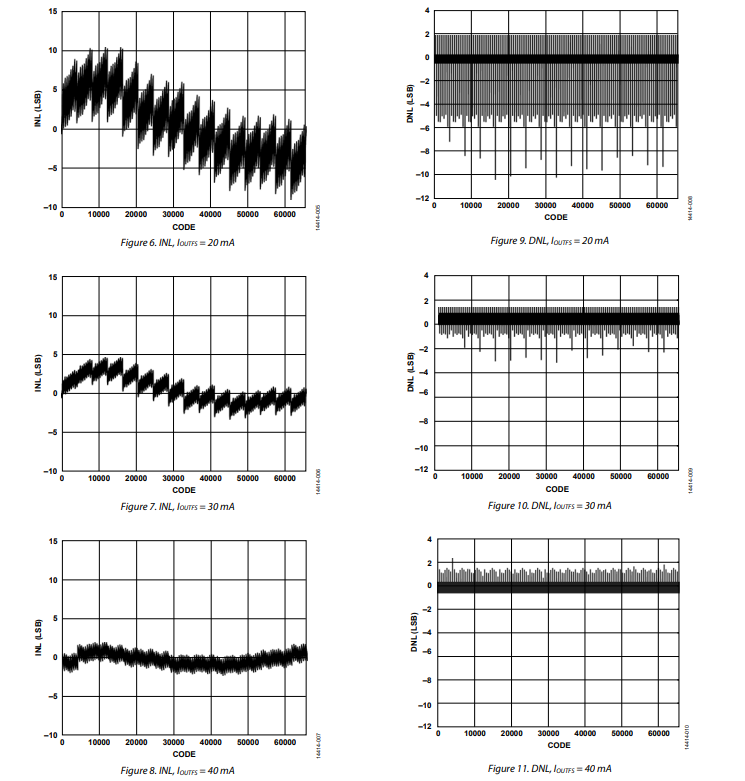

典型性能特征

主数字数据路径

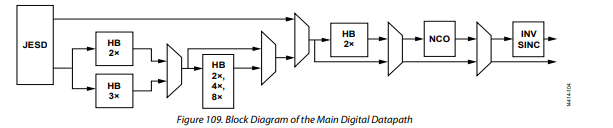

图109中的框图展示了主要数字数据路径的功能。数字处理包括一个输入插值模块,可选择2倍插值(1x、2x或3x插值),三个额外的2倍半带插值滤波器,一个最终的2倍NRZ模式插值滤波器FIR85(在某些情况下可绕过),一个由48位数控振荡器(NCO)组成的正交调制器以及一个反sinc模块。

所有的插值滤波器都接受同相(I)和正交(Q)数据流作为复数数据输入。同样,正交调制器和反sinc函数也接受输入数据作为复数数据流。因此,要使用数字数据路径功能,输入数据必须是复数数据流。

在旁路模式(1x插值)下,输入数据流应为实数据。

数据格式

AD9164所有模式下的输入数据格式均为16位二进制补码。数字数据路径和数模转换器(DAC)解码器以二进制补码格式运行。

为避免杂散频率泄漏,输入到DAC的数字码必须围绕零码进行平衡(正码数量必须等于负码数量)。也就是说,必须从输入数字码中去除输入直流偏移。否则,使用数控振荡器(NCO)时,杂散可能会出现在直流偏移附近。NCO频率的偏移在NCO频率调谐字(FTW)中表现为一个小杂散。

插值滤波器

主数字数据路径包含五个半带插值滤波器,以及用于2x NRZ模式的最终半带插值滤波器。这些滤波器中的第一对有两种选择,可设置为2x(HBA2)或3x(HBB3),如图109所示。这些滤波器有两种带宽选择,80%或90%。80%带宽的滤波器功耗比90%带宽的滤波器低。要选择滤波器带宽为90%,需将DATAPATH_CFG寄存器(0x111)的第4位编程为0b1。

在第一对滤波器之后是一系列2x半带滤波器,每个滤波器的可用带宽是前一个滤波器的一半。其中,HB4为45%,HB5为22.5%,HB6为11.25%。

最终的半带滤波器FIR85用于2x NRZ模式。它的时钟频率为2×**f_{DAC}速率,可用带宽为f_{DAC}**速率的45%。FIR85是一个复数滤波器,因此其带宽在0 Hz处居中。FIR85滤波器与复数插值模式配合使用,可提高DAC更新速率,并使镜像远离所需信号。

表34展示了如何选择每种可用的插值模式、它们的可用信号带宽以及最大数据速率。计算可用信号带宽(BW_{SIGNAL})的方法是将插值滤波器带宽(BW_{FILT})乘以**f_{DAC}**除以插值因子,公式如下:BW_{SIGNAL}=BW_{FILT}×(f_{DAC}/Interpolation Factor) 。

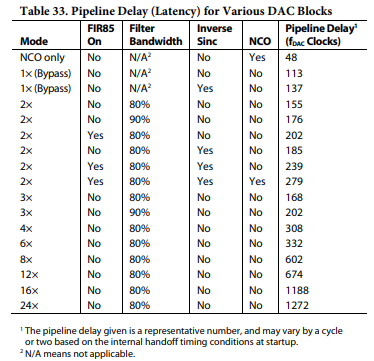

流水线延迟会根据所选的数字数据路径功能而变化。表33列举了数字数据路径模块的流水线延迟示例。这些延迟是在JESD204B延迟基础上额外增加的。

-

1 GSPS直接数字频率合成器AD9858概述2023-04-13 1164

-

UG-475:评估采用14位DAC的AD9912 1 GSPS直接数字频率合成器2021-05-27 1113

-

AD9174:双16位12.6 GSPS RF DAC和直接数字合成器数据表2021-05-26 1170

-

AD9164:16位、12 GSPS、RF DAC和直接数字合成器数据表2021-04-24 1151

-

AD9915: 2.5 GSPS直接数字频率合成器,内置12位数模转换器数据手册2021-03-19 942

-

高性能16位数模转换器AD9164怎么样?2019-10-23 3181

-

AD9914BCPZ数字频率合成器产品介绍2019-06-17 1673

-

AD9914BCPZ直接数字频率合成器2019-04-29 1547

-

采用AD9914 3.5 GSPS直接数字频率合成器的AD9914/PCBZ评估板2019-03-01 3223

-

3.5 GSPS直接数字频率合成器AD9914的优势特性2018-10-15 2763

-

AD9164BBCZ 直接数字频率合成器2018-07-29 1699

全部0条评论

快来发表一下你的评论吧 !