AD9102低功耗、14位、180MSPS、数模转换器和波形发生器技术手册

描述

概述

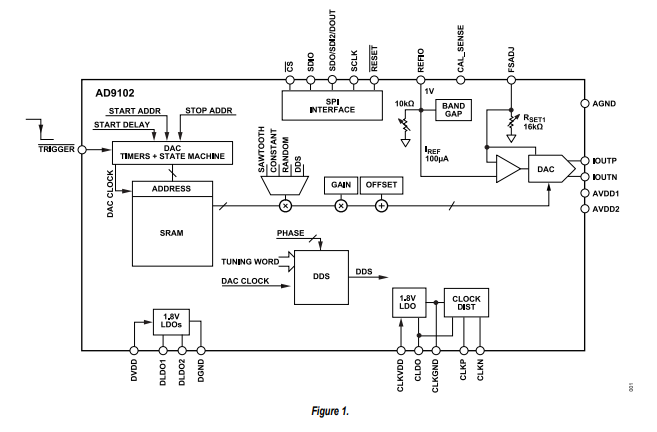

AD9102 TxDAC®和波形发生器是高性能DAC,集成片上模式存储器,用于复杂波形生成,具有直接数字频率合成器(DDS)。

该DDS是一个14位输出、最高180MHz的主机时钟正弦波发生器,带24位调谐字,支持10.8Hz/LSB的频率分辨率。

数据表:*附件:AD9102低功耗、14位、180MSPS、数模转换器和波形发生器技术手册.pdf

SRAM数据可包含直接生成的存储波形、施加于DDS输出或DDS频率调谐字的幅度调制模式。

内部模式控制状态机允许用户对DAC的模式周期以及DAC信号输出的周期内起始延迟进行编程。

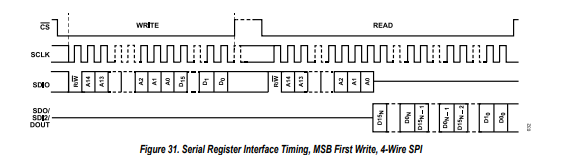

SPI接口用于配置数字波形发生器,并将模式载入SRAM。

在数字信号传送至DAC的过程中对信号进行增益调节和失调调节。

AD9102提供出色的交流和直流性能,并支持高达180 MSPS的DAC采样率。

AD9102具有灵活的工作电源范围(1.8 V至3.3 V)和低功耗,非常适合便携式和低功耗应用。

产品特色

- 高度集成。

片内DDS和4096 × 14模式存储器 - 低功耗。

DAC采用1.8 V至3.3 V单电源供电

为低功耗空闲期提供省电模式

应用

- 医疗仪器

- 便携式仪器

- 信号发生器、任意波形发生器

- 汽车雷达

特性

- 片内4096 × 14位模式存储器

- 片内DDS

- 功耗(3.3 V、4 mA输出)

- 96.54 mW (180 MSPS)

- 休眠模式:<5 mW(3.3 V时)

- 电源电压:1.8 V至3.3 V

- 差分电流输出:8 mA(最大值,3.3 V)

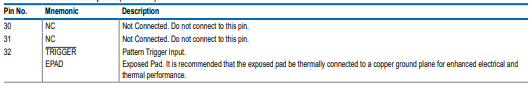

- SFDR至奈奎斯特频率

- 87 dBc(10 MHz输出)

- 相位噪声(1 kHz偏移、180 MSPS、8 mA):−150 dBc/Hz

- 小尺寸、32引脚、5 mm × 5 mm LFCSP无铅封装,3.6 mm × 3.6 mmexposed pad

框图

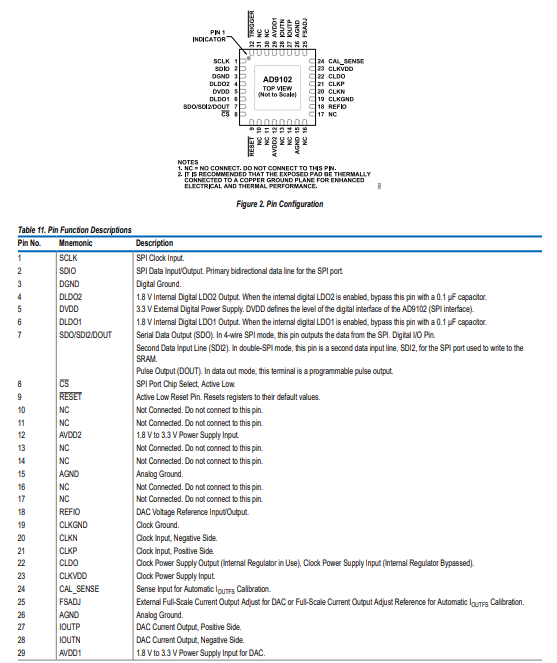

引脚配置描述

典型性能特征

工作原理

配置寄存器更新流程

大多数可通过SPI访问的寄存器都采用双缓冲。在模式生成期间,一组活动寄存器控制AD9102的操作,而另一组影子寄存器可随时写入。影子寄存器配置更新完成后,需将RAMUPDATE(寄存器0xD1)中的位0设为1,才能将寄存器组从影子寄存器传输至活动寄存器。无论模式生成器中PAT_STATUS(寄存器0xE1,位1)的状态如何,都需执行此操作。

RAMUPDATE适用于所有SPI设置,但不适用于4096×14位SRAM寄存器。有关SRAM更新流程,请参阅SRAM部分。由于采用双缓冲配置,SPI读操作返回的是影子寄存器中的值,而非活动寄存器中的值。

数模转换器(DAC)传输函数

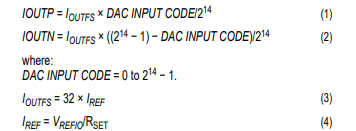

AD9102 DAC提供差分电流输出:IOUTP/IOUTN。芯片上生成的数字波形作为DAC的输入,采用二进制补码形式。每个数字波形字在输入到每个DAC内核之前会立即取反。DAC输入代码变量(公式1和公式2使用偏移二进制数系统(二进制补码取反))。

DAC输出电流计算公式如下:

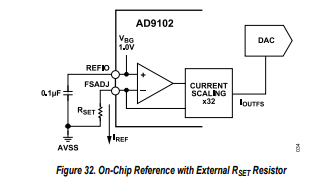

使用片上**R_{text{SET}}**电阻时,通过启用自动增益校准功能(详见自动增益校准部分),可提高DAC增益精度。

电压基准

AD9102包含一个标称值为1.0 V的内部带隙基准电压V_{text{BG}}。默认情况下,芯片上电时启用片上基准。使用片上基准时,REFIO端子需使用0.1 μF电容连接到AGND,如图32所示。

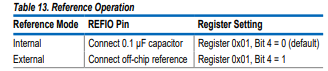

或者,可使用更精确的片外基准替换片上基准。要应用外部基准,需在POWERCONFIG(寄存器0x01,位4)中将REF_EXT设为1,然后将外部基准连接到REFIO引脚。在这种情况下,不需要0.1 μF电容,因为内部基准不会直接影响外部基准。

使用外部基准时,建议关闭内部基准以降低功耗。为此,需在POWERCONFIG(寄存器0x01,位5)中将REF_PDN设为1。外部基准可提供比片上带隙基准更严格的电压容差和/或更低的温度漂移。表13总结了基准连接和编程方法。

-

ADI推出集成复杂波形生成功能的DAC AD9106和AD91022012-12-14 6655

-

AD9653BCPZ-125 数模转换器2018-09-03 2497

-

AD9142BCPZ数模转换器2019-05-13 979

-

使用AD9117双路低功耗14位TxDAC数模转换器的AD9117-DPG2-EBZ评估板2019-10-22 2639

-

AD9102的相关资料分享2021-12-06 2545

-

AD9102锯齿发生器的波形来源,实现输出锯齿波应该配置那些寄存器呢?2023-12-04 635

-

基于18位数模转换器AD760的波形发生器的设计2009-09-03 587

-

低功耗、14位、180MSPS数模转换器和波形发生器2017-06-06 1184

-

AD9102 低功耗、14位、180MSPS、数模转换器和波形发生器2019-02-22 558

-

AD9102:低功耗、14位、180 MSPS数模转换器和波形发生器2021-03-19 985

-

AD9106:四通道、低功耗、12位、180 MSPS数模转换器和波形发生器2021-03-20 1107

-

AD9121:双14位1230 MSPS,TxDAC+数模转换器2021-04-20 1000

-

任意波形发生器芯片AD9102的应用2021-11-23 2416

-

DAC5672 14位275 MSPS数模转换器数据表2024-07-29 506

-

AD9102:高性能数模转换器与波形发生器的深度解析2026-04-13 293

全部0条评论

快来发表一下你的评论吧 !