LP2995系列 DDR 终端稳压器数据手册

描述

LP2995 线性稳压器旨在满足 JEDEC SSTL-2 和 SSTL-3 标准 DDR-SDRAM 终止规范。该器件包含一个高速运算放大器 对负载瞬变提供出色的响应。输出级可防止击穿,同时 根据需要在应用中提供 1.5A 的连续电流和高达 3A 的瞬态峰值 DDR-SDRAM 端接。LP2995 还集成了 V意义pin 提供 卓越的负载调整率和 V裁判output 作为芯片组的参考 和 DDR DIMM。

*附件:lp2995.pdf

特性

- 低输出电压偏移

- 与 +5v、+3.3v 和 2.5v 电源轨配合使用

- 拉电流和吸收电流

- 外部元件数量少

- 无需外部电阻器

- 线性拓扑

- 采用 SOIC-8、SO PowerPAD-8 或 WQFN-16 封装

- 成本低且易于使用

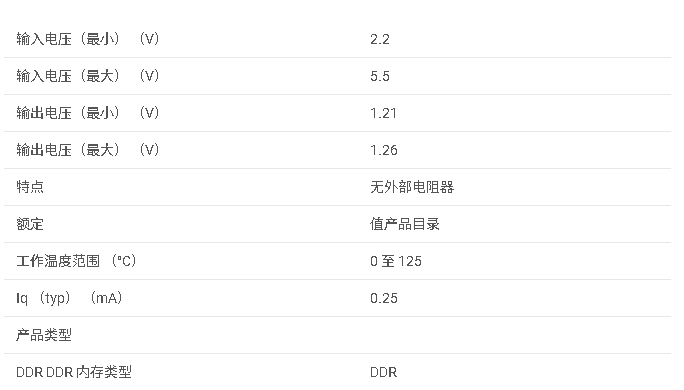

参数

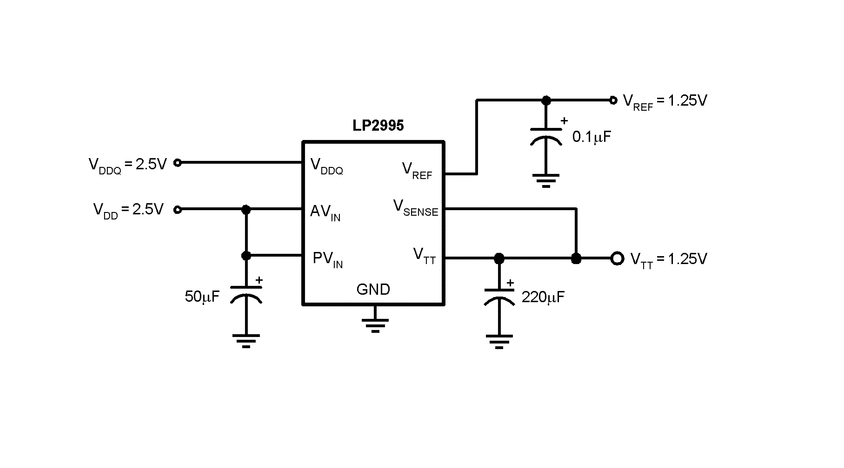

方框图

一、产品概述

LP2995是一款线性稳压器,专为满足JEDEC SSTL-2和SSTL-3规范的DDR-SDRAM终止电压而设计。该器件集成了高速运算放大器,以提供对负载瞬变的快速响应,并具备低输出电压偏移、源和沉电流能力、低外部元件数量以及线性拓扑结构等特点。

二、主要特性

- 低输出电压偏移:确保输出电压的稳定性。

- 源和沉电流能力:提供高达1.5A的连续电流和高达3A的瞬态峰值电流。

- 低外部元件数量:简化了电路设计。

- 线性拓扑结构:提供稳定的电压输出。

- 高速运算放大器:快速响应负载瞬变。

- 多种封装选项:包括SOIC-8、SO PowerPAD-8和WQFN-16封装。

三、引脚功能

LP2995提供不同封装选项,各封装的引脚功能基本一致,主要引脚包括:

- AVIN:模拟输入引脚,为内部控制电路供电。

- PVIN:功率输入引脚,为输出级功率运算放大器供电。

- VDDQ:参考电压输入引脚,用于生成内部参考电压。

- VREF:缓冲后的内部参考电压输出,用于为芯片组和DDR DIMM提供参考。

- VTT:调节后的输出电压,用于DDR-SDRAM的终止电阻。

- VSENSE:反馈引脚,用于改进远程负载调节。

- GND:接地引脚。

四、电气特性

- 参考电压(VREF) :典型值为1.25V(VDDQ/2),具有低输出阻抗。

- 输出电压偏移(VTT Offset) :在无负载条件下,偏移量在±15mV以内。

- 负载调节:在0至1.5A输出电流范围内,负载调节率为±0.5%。

- 静态电流(Iq) :典型值为400μA(AVIN=2.5V)。

五、应用电路

LP2995可应用于DDR-SDRAM的SSTL-2和SSTL-3终止方案。典型应用电路包括输入电容、输出电容、VTT终止电阻以及必要的旁路电容等元件。

六、热性能与封装

- 热性能:数据手册提供了不同封装和散热条件下的热阻(θJA)值,并建议了优化热性能的布局方法。

- 封装选项:包括SOIC-8、SO PowerPAD-8和WQFN-16封装,用户可根据应用需求选择合适的封装形式。

七、PCB布局考虑

为了确保LP2995的最佳性能,数据手册提供了PCB布局的详细建议,包括:

- 将AVIN和PVIN引脚短接,并在PVIN引脚附近放置旁路电容。

- 将GND引脚连接到接地平面,并使用多个过孔以改善热性能。

- 将VSENSE引脚连接到需要调节的VTT终止总线的中心位置。

- 将VDDQ引脚远程连接到DDR DIMM或芯片组的VDDQ电源轨。

- 在VREF引脚附近放置一个0.01μF或0.1μF的陶瓷旁路电容。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LP2998/LP2998 - Q1 DDR 端接稳压器:设计与应用指南2026-03-18 371

-

LP2998系列 带关断引脚的 1.5A DDR 终端稳压器数据手册2025-04-29 1172

-

LP2998-Q1 用于汽车应用的 DDR 终端稳压器数据手册2025-04-27 1150

-

TPS51200-EP 灌电流/拉电流 DDR 终端稳压器数据手册2025-04-26 1759

-

DDR终端调节器LP2996-N LP2996A数据表2024-04-07 406

-

DDR终端调节器LP2998/LP2998-Q1数据表2024-03-28 570

-

灌电流和拉电流 DDR 终端稳压器TPS51200数据表2024-03-13 588

-

LP2995DDR终端输出调节器相关资料下载2021-05-20 1031

-

LTC3617:±6A单片同步降压稳压器,用于DDR终端数据表2021-04-15 908

-

新唐科技DDR 总线终端稳压系列介绍2020-02-04 2450

-

TPS51200 汲极/源极双数据速率(DDR) 终端稳压器2008-09-01 2633

全部0条评论

快来发表一下你的评论吧 !