MAX5882 14位、4.6Gsps电缆下行RF直接合成DAC技术手册

描述

概述

MAX5882为14位、4.6Gsps数/模转换器(DAC),将电缆调制解调器终端(CMTS)和EQAM设备的多载波正交调幅(QAM)信号直接合成为RF输出。DAC具有优异的杂散特性和噪声、邻道功率(ACP)性能,并可根据电缆数据传输业务接口规范(DOCSIS®)的要求直接合成为47MHz至1003MHz电缆下行链路的多个载波。4.6Gsps刷新速率允许以数字方式产生高于2GHz带宽的信号。

器件具有四个14位、多路复用的低压差分信号(LVDS)输入端口,每个端口可工作在高达1150Mwps的双数据率(DDR)或单数据率(SDR)模式。输入支持差分高速收发器逻辑(DHSTL)输入电平。由于在时钟的上升沿和下降沿均触发转换,器件能够支持的速率为1/2 DAC刷新时钟频率。每个端口的输入数据速率为DAC刷新率的1/4或时钟速率的1/2。器件集成延时锁相环(DLL),简化与FPGA或ASIC器件的接口。利用DLL调节输出时钟(DATACLK)的相位,以确保输入LVDS数据总线与数据锁存片上时钟保持恰当的定时关系。

器件为电流控制型DAC,集成50Ω差分输出匹配电阻,以确保最佳动态性能。器件采用3.3V和1.8V电源供电,工作在4.6Gsps时,功耗仅为2.3W。器件工作在扩展商业级温度范围(0°C至+85°C),采用256 CSBGA无铅(Pb)/符合RoHS标准的封装。

数据表:*附件:MAX5882 14位、4.6Gsps电缆下行RF直接合成DAC技术手册.pdf

应用

- 广播级视频调制器

- 电缆调制解调器终端系统(CMTS)

- DOCSIS兼容Edge QAM设备

- 视频点播(VOD)

特性

- 4.6Gsps输出刷新率

- 直接合成RF输出,47MHz至1003MHz

- 不会将HD3混叠到电缆频带

- 业内领先的DOCSIS 3.0噪底指标

- -70dBc @ f

OUT= 900MHz,8通道(256 QAM) - -66dBc @ f

OUT= 900MHz,16通道(256 QAM) - -62dBc @ f

OUT= 900MHz,32通道(256 QAM) - -57dBc @ f

OUT= 500MHz,128通道(256 QAM)

- -70dBc @ f

- 9dBm (CW)高输出功率

- 支持低功耗设计

- 4:1多路复用LVDS输入

- 每个端口高达1150Mwps

- 双数据率(DDR)模式

- 片上DLL用于同步输入数据

- 奇偶校验错误标识

- 内部50Ω差分输出匹配电阻

- 输入寄存器扫描模式

- 紧凑的17mm × 17mm、256引脚CSBGA封装

- 备有评估板(定购MAX5882EVKIT+)

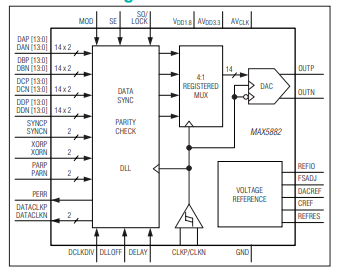

框图

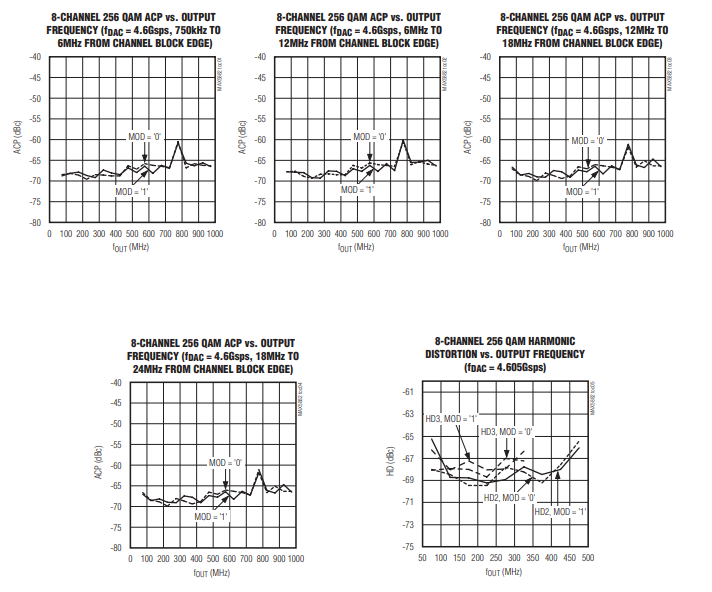

典型操作特性

应用信息

启动条件

该设备采用了保护电路,以防止数模转换器(DAC)输出端受损。当参考电压(VREFIO)低于0.4V时,内部时钟电路将被禁用。当DAC输出不工作时,保护电路处于激活状态。如果数据来源需要DATA时钟来正常运行,那么参考电压必须保持在0.4V以上。

设备的数字锁相环(DLL)电路需要一个有源、稳定的时钟输入和稳定的电源,才能准确运行。在施加初始电源并使时钟稳定后,DLL电路应通过将DLLOFF引脚设置为逻辑0来复位。然后可以根据需要更改DLL频率和延迟。

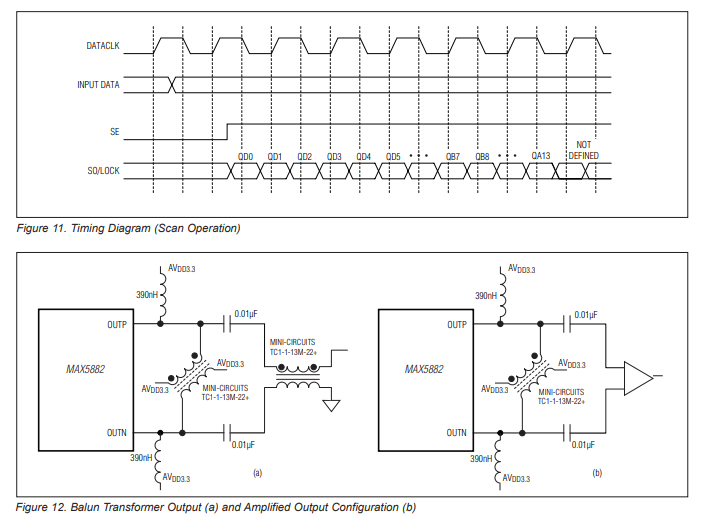

输出耦合

OUTP和OUTN之间的差分电压可使用变压器或差分放大器转换为单端电压。数模转换器(DAC)输出应上拉至AVDD3.3。建议使用偏置电阻将输出从两个独立电感分压器上拉。图12中展示了推荐的输出电路配置。为实现最大带宽并最小化变压器次级侧接地引线上的电感,请使用极短的走线,并在接地层上使用多个过孔进行连接。

频谱考量

DAC更新速率选择

该设备4.6Gsps的最大更新速率为系统设计提供了灵活性。在更新速率与性能或电路复杂度方面存在几种权衡,选择DAC更新速率时应考虑这些因素。

由于DAC输出在时钟的两个边缘上都有输出,所以在fDAC/2 - fOUT处会出现所需DAC输出的衰减镜像。DAC更新速率必须至少是电缆带宽内产生的最高频率的四倍,以将此镜像排除在频带之外。由于DOCSIS(数据业务接口规范)射频附件A定义了3.03MHz的上限频率,在某些情况下,为了将此镜像的带外抑制保持在40dB以上,需要1GHz的输出滤波器。随着DAC更新速率降低至较低要求,滤波器的设计变得越来越困难。不过,使用较低的更新速率有几个潜在优点。首先,随着更新速率从4.6Gsps的最大值降低到4Gsps,设备的整体杂散性能会提高。其次,系统输入的功率要求会降低。在4Gsps时,设备本身的功耗比4.6Gsps时大约低15%,而ASIC或FPGA等其他组件在较低更新速率下的功耗也会降低。另一个需要考虑的因素是,较高更新速率下的时序裕度会减小,且更难满足要求。

谐波失真

该设备具有较低的谐波失真。二次谐波失真(HD2)和三次谐波失真(HD3)通常是主要的谐波。在500MHz以下的频率,HD2在1GHz以下的频率通常低于-60dBc。当DAC更新速率高于4Gsps时,HD2和HD3在低于333MHz的输出频率下不会混叠到45MHz至1000MHz频段内。

时钟频率附近的谐波

该设备在fDAC/2 - 2×fOUT处存在杂散信号。此杂散信号低于DOCSIS限制,但可能会违反DOCSIS射频共存要求,即较低频道与较高输出频率共存时的要求。当fOUT = fDAC/6时,此杂散信号与输出频率重合。如有必要,可使用数字预失真来降低此杂散信号。

接地、旁路、电源和电路板布局注意事项

接地和电源去耦会显著影响设备的性能。不需要的数字串扰可能会通过输入、参考电压、电源和接地连接耦合进来,从而影响动态性能。应严格遵循高速、高频应用的正确接地和电源去耦准则。这可减少电磁干扰(EMI)和内部串扰,从而显著提升设备的动态性能。

需要使用具有独立接地和电源平面的多层印刷电路板(PCB)。建议将模拟输出和时钟输入作为受控阻抗微带线在电路板顶层直接布线,且不使用过孔连接时钟输入(CLKP、CLKN)和模拟输出(OUTP、OUTN)信号。根据走线长度和工作条件,可能需要使用低介电常数材料(如ROGERS RO4003)作为顶层材料,以便对数据时钟(DATACLKP、DATACLKIN)和DAC输出进行路由,从而将耦合到时钟输入和DAC输出的干扰降至最低。

数字信号应作为受控阻抗走线在接地平面之间布线。数字信号应远离敏感的模拟输入、参考输入感应线、公共模式输入,并且尽量远离时钟输入。尤其重要的是,要尽量减少数字信号与时钟之间的耦合,以优化高速输出频率下的动态性能。对称的时钟输入和模拟输出走线设计对于减少失真和优化DAC的动态性能至关重要。

数字信号路径应尽量短,走线长度应匹配,以避免数据延迟失配。

-

MAX5879 14位、2.3Gsps直接RF合成DAC,提供可选择频响技术手册2025-05-06 1212

-

AD9174双路、16位、12.6 GSPS RF DAC和直接数字频率合成器技术手册2025-04-30 1754

-

UG-475:评估采用14位DAC的AD9912 1 GSPS直接数字频率合成器2021-05-27 1082

-

AD9174:双16位12.6 GSPS RF DAC和直接数字合成器数据表2021-05-26 1140

-

AD9172:带通道器的双16位12.6 GSPS RF DAC产品手册2021-05-16 1528

-

AD9175:双11位/16位12.6 GSPS RF DAC,带宽带通道器产品手册2021-05-10 913

-

AD9164:16位、12 GSPS、RF DAC和直接数字合成器数据表2021-04-24 1119

-

AD9910: 1 GSPS、14位、3.3 V CMOS直接数字频率合成器2021-03-19 983

-

基于RF DAC的RF直接变频发送器实现设计2019-07-04 3227

-

MAX5882 14位,4.6Gsps下行电缆直接RF-DAC2012-04-26 1339

-

MAX5881直接RF合成DAC与FPGA的接口2009-04-16 955

-

MAX5881 12位、4.3Gsps下行电缆直接RF合成D2008-10-06 972

全部0条评论

快来发表一下你的评论吧 !