MAX5879 14位、2.3Gsps直接RF合成DAC,提供可选择频响技术手册

描述

概述

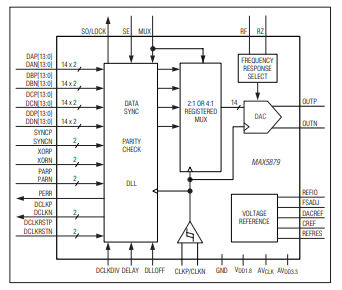

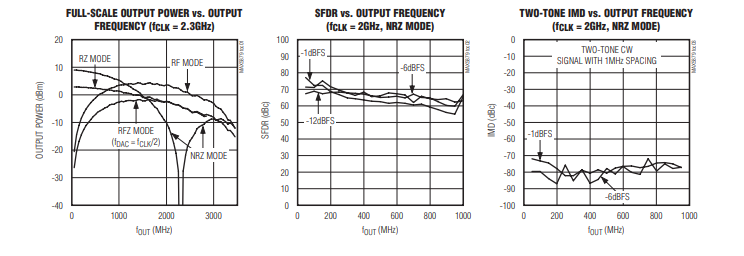

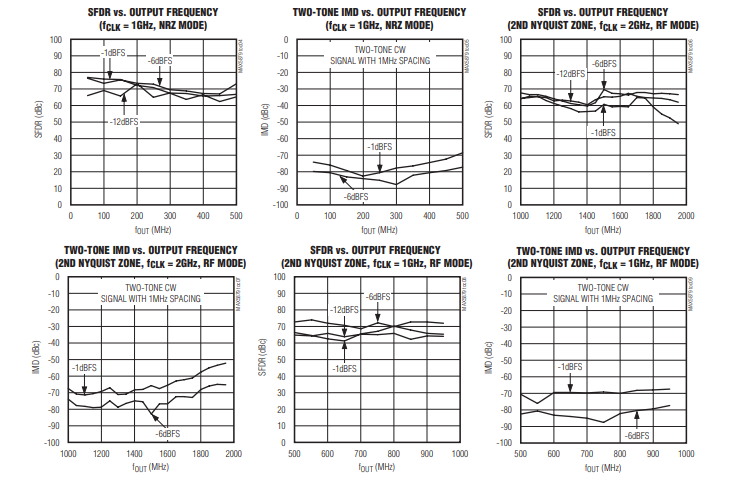

MAX5879是高性能、14位、2.3Gsps数/模转换器(DAC),在基带和高阶奈奎斯特区用于合成高频和宽带信号。2.3Gsps刷新速率,结合可选择的频率响应模式(NRZ、RZ、RF和RFZ),允许生成超过2GHz输出频率的数字信号。独特的RFZ模式可产生高达6阶的奈奎斯特信号,刷新速率可达1150Msps。器件具有优异的杂散、噪声和交调失真性能,可以直接合成超过1GHz的信号带宽。

数据表:*附件:MAX5879 14位、2.3Gsps直接RF合成DAC,提供可选择频响技术手册.pdf

器件具有四路14位、多路复用、低压差分信号(LVDS)输入端口,每个端口工作速率达1150Mwps。DAC工作时钟频率(f CLK )可达2.3GHz。器件具有一个可选择的2:1或4:1输入多路复用器,允许用户选择两个数据端口(每端口速率高达1150Mwps),或四个数据端口(每端口速率高达575Mwps)。相应地,每个端口的输入数据速率为DAC刷新速率的1/2或1/4。器件的延迟锁相环(DLL)可方便器件与FPGA或ASIC进行数据同步。奇偶输入和奇偶误差标识输出用于检测数据源与DAC之间的误码。器件还具有数据时钟复位电路,用于对齐多个DAC数据采集时钟。

器件具有四个可选择的频率响应输出模式:

- 不归零(NRZ)模式,在第一段奈奎斯特区提供最高动态范围/输出功率。

- 归零(RZ)模式,在第一、第二和第三段奈奎斯特区调整SNR,以改善增益平坦度。

- 射频(RF)模式,在第二和第三奈奎斯特区提供较高的SNR和优异的动态性能。

- 射频归零(RFZ)模式,f

CLK/2最大刷新速率下,在第三至第六奈奎斯特区提供高动态范围并改善增益平坦度。

器件采用电流型DAC架构,集成50Ω差分输出匹配电阻,确保器件的最佳动态性能。器件工作在3.3V和1.8V电源,40mA满量程电流下耗电1.8W;80mA满量程电流下耗电2.3W。器件工作在-40°C至+85°C扩展级温度范围,采用256焊球(17mm x 17mm) CSBGA封装。

应用

- 任意波形发生器

- 宽带通信

- 数字视频广播

- 直接数字合成器

- 边缘QAM和CMTS

- 雷达和航空设备

- 软件无线电

- 无线基础设施

特性

- 业界领先性能

- WCDMA ACLR:2.14GHz下为70dB

- DOCSIS ACP:400MHz、8通道(256 QAM)下为-70dBc

- 噪声密度:200MHz下为-165dBc/Hz

- 高输出功率:9dBm (CW)

- 频率响应模式:NRZ、RZ、RF、RFZ

- 2GHz输出带宽

- 2:1或4:1多路LVDS输入

- 每个端口达1150MHz

- 工作在1倍或2倍数据速率

- 片上DLL用于输入数据同步

- 复位功能用于多路DAC同步

框图

典型操作特性

应用信息

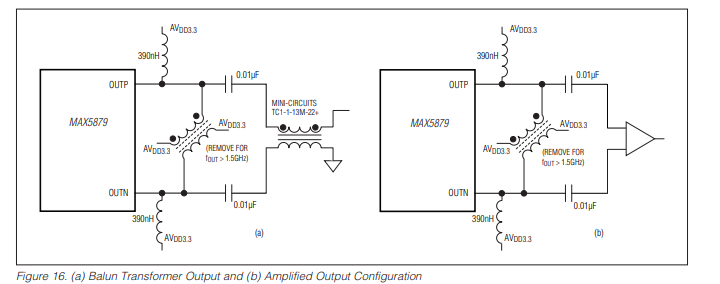

输出耦合

OUTP和OUTN之间的差分电压可使用变压器或差分放大器转换为单端电压。数模转换器(DAC)输出应上拉至AVDD3.3 。建议使用偏置抽头,利用分立电感和电容将输出上拉。图16中展示了推荐的输出电路配置。为实现最大带宽并尽量减小变压器次级侧接地引线上的电感,连接接地层时请使用极短的走线和多个过孔。

接地、旁路、电源及电路板布局注意事项

接地和电源去耦会对器件性能产生显著影响。不需要的数字串扰可能会通过输入、基准、电源和接地连接耦合进来,从而影响动态性能。高速高频应用的正确接地和电源去耦准则应严格遵守。这有助于减少电磁干扰(EMI)和内部串扰,而它们会显著影响器件的动态性能。

使用具有独立接地层和电源层的多层印刷电路板(PCB)是必要的。建议将模拟输出和时钟输入作为受控阻抗微带线在电路板顶层布线。

直接布设在接地层上方,且模拟输出(OUTP、OUTN)信号和时钟输入(CLKP、CLKN)不使用过孔。根据走线长度和工作条件,可能需要使用低损耗电介质材料(如ROGERS RO4003)作为顶层电介质材料。数据时钟(DCLKP、DCLKN)的布线应使耦合到时钟输入和DAC输出的干扰最小化。

数字信号应作为受控阻抗走线布设在接地层之间。数字信号应尽量远离敏感的模拟输入、基准输入感应线、共模输入和时钟输入。尤其重要的是,要尽量减小数字信号与时钟之间的耦合,以优化高速输出频率下的动态性能。对称的时钟输入和模拟输出走线设计对于最小化失真和优化DAC的动态性能至关重要。数字信号路径应尽量短,走线长度应匹配,以避免数据延迟失配。

该器件支持三个独立的电源输入,分别用于模拟3.3V(AVDD3.3)、开关电源(VDD1.8)和时钟(AVCLK)电路。每个AVDD3.3、VDD1.8和AVCLK输入都应在尽可能靠近输入的位置连接一个独立的47nF电容器,其另一端应连接到对应的接地层,以尽量减小环路电感。这三个电源电压也应在其离开印刷电路板的位置去耦,可使用钽电容或电解电容,并添加铁氧体磁珠,以及形成π型网络的去耦电容,这样也能改善性能。

-

探索MAX5882:14位、4.6Gsps电缆下游直接RF合成DAC的卓越性能2026-04-22 263

-

MAX5882 14位、4.6Gsps电缆下行RF直接合成DAC技术手册2025-05-06 1162

-

AD9164 16位、12 GSPS、RF DAC和直接数字频率合成器技术手册2025-04-30 2153

-

UG-475:评估采用14位DAC的AD9912 1 GSPS直接数字频率合成器2021-05-27 1113

-

AD9174:双16位12.6 GSPS RF DAC和直接数字合成器数据表2021-05-26 1170

-

AD9164:16位、12 GSPS、RF DAC和直接数字合成器数据表2021-04-24 1151

-

RF直接变频发送器的优势是什么?2019-08-23 1870

-

基于RF DAC的RF直接变频发送器实现设计2019-07-04 3237

-

利用MAX5879 DAC实现RF直接变频发送器 提升系统稳定性2017-11-24 1409

-

MAX5882 14位,4.6Gsps下行电缆直接RF-DAC2012-04-26 1349

-

MAX5879高性能数模转换器(DAC)2011-08-16 2415

-

MAX5881 12位、4.3Gsps下行电缆直接RF合成D2008-10-06 980

全部0条评论

快来发表一下你的评论吧 !