AD9837低功耗、8.5mW、2.3V至5.5V可编程波形发生器技术手册

描述

概述

AD9837是一款低功耗、可编程波形发生器,能够产生正弦波、三角波和方波输出。各种类型的检测、致动和时域反射(TDR)应用都需要波形发生器。输出频率和相位可通过软件进行编程,调整简单。频率寄存器为28位:时钟速率为16 MHz时,可以实现0.06 Hz的分辨率;而时钟速率为5 MHz时,则可以实现0.02 Hz的分辨率。

AD9837通过一个3线串行接口写入数据。该串行接口能够以最高40 MHz的时钟速率工作,并且与DSP和微控制器标准兼容。该器件采用2.3 V至5.5 V电源供电。

AD9837具有关断(SLEEP)功能。器件中不用的部分可以关断,以将功耗降至低点。例如,在产生时钟输出时,可以关断DAC。

AD9837采用10引脚LFCSP_WD封装。

数据表:*附件:AD9837低功耗、8.5mW、2.3V至5.5V可编程波形发生器技术手册.pdf

应用

- 频率激励/波形发生

- 液体和气流测量

- 传感器应用:接近度、运动和缺陷检测

- 线路损耗/衰减

- 测试与医疗设备

- 扫描/时钟发生器

- 时域反射(TDR)应用

特性

- 数字可编程频率和相位

- 功耗:8.5 mW(2.3 V时)

- MCLK速率:16 MHz(B级),5 MHz(A级)

- 28位分辨率:0.06 Hz(16 MHz参考时钟)

- 正弦波/三角波/方波输出

- 2.3 V至5.5 V电源供电

- 三线式SPI接口

- 扩展温度范围:–40°C至+125°C

- 关断选项

- 10引脚LFCSP封装

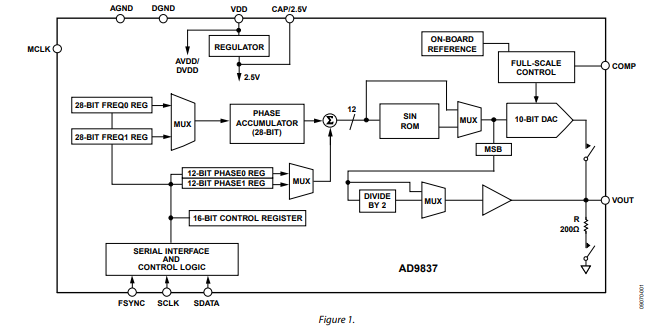

框图

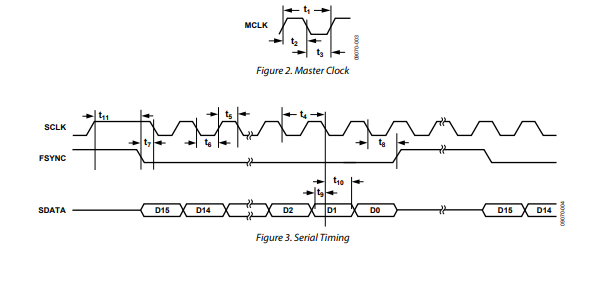

时序图

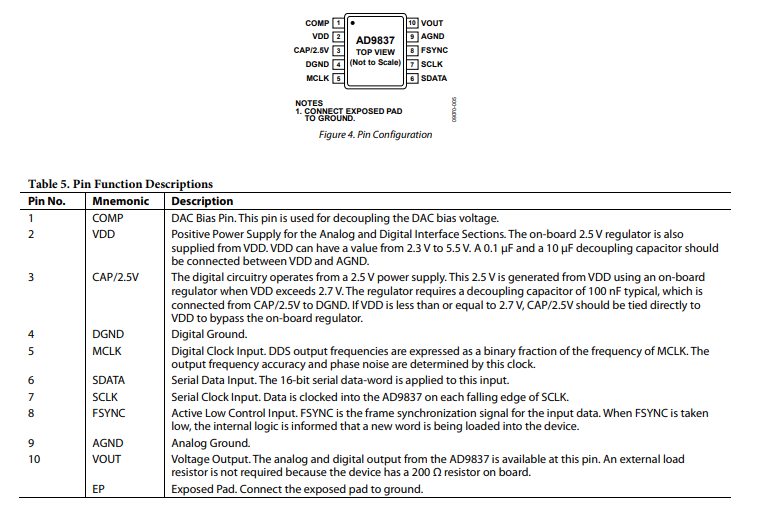

引脚配置描述

典型性能特征

应用信息

AD9837提供的多种输出选项,使其适用于广泛的应用,包括调制应用。AD9837可用于执行简单调制,如频率转换键控(FSK)。更复杂的调制方案,如高斯最小移频键控(GMSK)和正交相移键控(QPSK),也可通过AD9837实现。

在FSK应用中,AD9837的两个频率寄存器被加载不同的值。一个频率代表频移空间频率,另一个代表标记频率。通过使用AD9837控制寄存器中的FSEL位,用户可以调制载波频率在这两个值之间。

AD9837有两个相位寄存器,启用后可实现相移键控(PSK)。使用PSK时,当调制器的LSB输入为高电平时,载波频率会发生相移,即相位会改变一定量。

AD9837也适用于信号发生器应用。由于DAC数据的MSB在YOUT引脚可用,该器件可用于生成方波。

鉴于其低电流消耗,该器件也适用于可作为本地振荡器使用的应用。

接地与布局

印刷电路板的设计应确保AD9837的模拟和数字部分分开,并限制在电路板的特定区域内。这便于使用可分离的接地层,这是一种普遍被认为能为接地平面提供最佳屏蔽效果的技术。数字和模拟接地平面应仅在一处连接。唯一需要AGND到DGND连接的器件是AD9837。如果AD9837处于多个器件需要AGND到DGND连接的系统中,连接应仅在一点进行,并且应建立从该点到AD9837的稳定接地路径。

避免在器件下方布线数字线路,这些线路会产生噪声。模拟接地平面应在AD9837下方布线,以避免噪声耦合。为AD9837供电的电源线应尽可能宽,以降低阻抗,并减少电源线上出现的尖峰噪声。像时钟这样的快速开关信号,应屏蔽良好,防止其辐射噪声到电路板的其他部分。

避免数字信号和模拟信号交叉。电路板两侧的走线应成直角相交,以减少馈通效应。在双层板上,微带线技术是最佳选择,但并非总是可行,因为电路板的另一侧专门用于接地平面和信号。

良好的去耦很重要。AD9837应使用0.1 μF陶瓷电容进行电源旁路,并与10 μF钽电容并联。为获得最佳性能,去耦电容应尽可能靠近器件放置,理想情况下应紧挨着器件。

与微处理器接口

AD9837具有串行接口,可使其直接与多个微处理器连接。该器件使用外部串行时钟将数据或控制信息写入器件。串行时钟的频率最高可达40 MHz。串行时钟可以是连续的,也可以根据需要空闲或低电平。每次向AD9837写入数据时,都会拉低FSYNC并保持低电平,直到写入16位数据。FSYNC信号将加载到AD9837中的16位信息成帧。

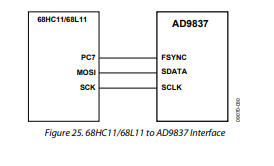

AD9837与68HC11/68L11接口

图25展示了AD9837与68HC11/68L11微控制器之间的串行接口。微控制器被配置为主设备,通过将SPCR中的MSTR位设置为1来实现。这会设置串行时钟(SCK);MOSI输出驱动串行数据线SDATA。由于微控制器没有专用的帧同步引脚,FSYNC信号由端口线(PC7)派生。正确操作接口的设置条件如下:

- 写操作期间SCK空闲为高电平(CPOL = 0)

- SCK下降沿数据有效(CPHA = 1)

当数据要从AD9837传输时,FSYNC线(PC7)拉低。串行数据到68HC11/68L11以8位字节传输,只有在出现下降沿时钟沿时才会传输。要将数据加载到AD9837中,PC7在第一个8位传输后保持低电平,然后对AD9837执行第二次串行写操作。只有在第二个8位传输后,才应再次拉高FSYNC。

-

AD9833低功耗可编程波形发生器:特性、应用与工作原理2026-04-16 342

-

AD9837:低功耗可编程波形发生器的技术剖析与应用2026-04-13 160

-

AD9833:低功耗可编程波形发生器的卓越之选2026-03-03 282

-

AD9838 11mW功耗、2.3V至5.5V的完整DDS技术手册2025-05-06 1416

-

UG-269:评估AD9837低功耗8.5 mW、2.3 V至5.5 V可编程波形发生器2021-03-20 874

-

AD9834: 20 mW功耗、2.3 V至5.5 V、75 MHz的完整DDS2021-03-19 725

-

2.3V至5.5V的LMX2306/16/26频率合成器2020-09-30 2412

-

用于便携式医疗仪器的16MHz时钟合成器评估板EVAL-AD9837SDZ2019-02-28 2907

-

AD9837 低功耗、8.5 mW、2.3 V至5.5 V可编程波形发生器2019-02-22 857

-

低功率8.5毫瓦2.3V到5.5V可编程波形发生器ad9837数据表2017-10-19 1379

-

低功耗、8.5mW、2.3V至5.5V可编程波形发生器2017-06-08 1445

-

AD9837,pdf (Programmable Waveform Generator)2011-04-30 1630

全部0条评论

快来发表一下你的评论吧 !