AD9912 1 GSPS直接数字频率合成器,内置14位数模转换器技术手册

描述

概述

AD9912是一款集成14位数模转换器(DAC)的直接数字频率合成器(DDS)。AD9912具有一个48位频率调谐字(FTW),可以合成步长不超过4μHz的频率。通过调整DAC系统时钟可以实现绝对频率精度。

AD9912还集成了系统时钟锁相环(PLL),支持低至25MHz的系统时钟输入。

AD9912在−40℃至+85℃工业温度范围内工作。

数据表:*附件:AD9912 1 GSPS直接数字频率合成器,内置14位数模转换器技术手册.pdf

应用

- LO捷变频率合成

- 低抖动、微调时钟产生

- 测试与测量设备

- 无线基站和控制器

- 安全通信

- 快速跳频

特性

- 1 GSPS内部时钟速度(直接输出高达400MHz)

- 集成1 GSPS 14位DAC

- 48位频率调谐字,分辨率为4μHz

- 差分HSTL比较器

- 灵活的系统时钟输入接受晶振或外部基准时钟

- 片内低噪声PLL REFCLK乘法器

- 2个SpurKiller通道

- 低抖动时钟倍频器,频率高达750 MHz

- 单端CMOS比较器;频率 <150 MHz

- 可编程输出分频器,支持CMOS输出

- 串行I/O控制

- 出色的动态性能

- 软件控制关断功能

- 采用两种64引脚LFCSP封装

- 残余相位噪声(250 MHz)

- 10 Hz偏移:-113 dBc/Hz

- 1 kHz偏移:-133 dBc/Hz

- 100 kHz偏移:-153 dBc/Hz

- 40 MHz偏移:-161 dBc/Hz

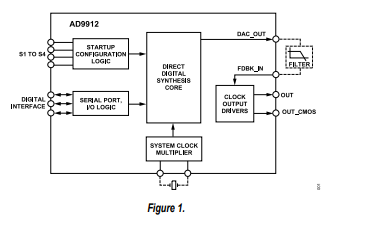

框图

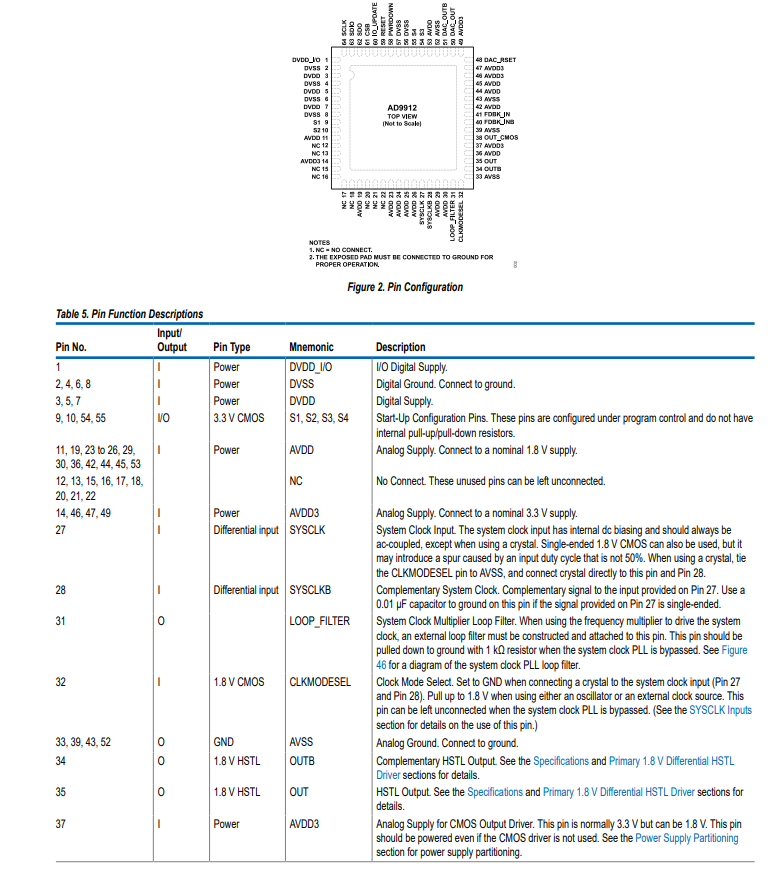

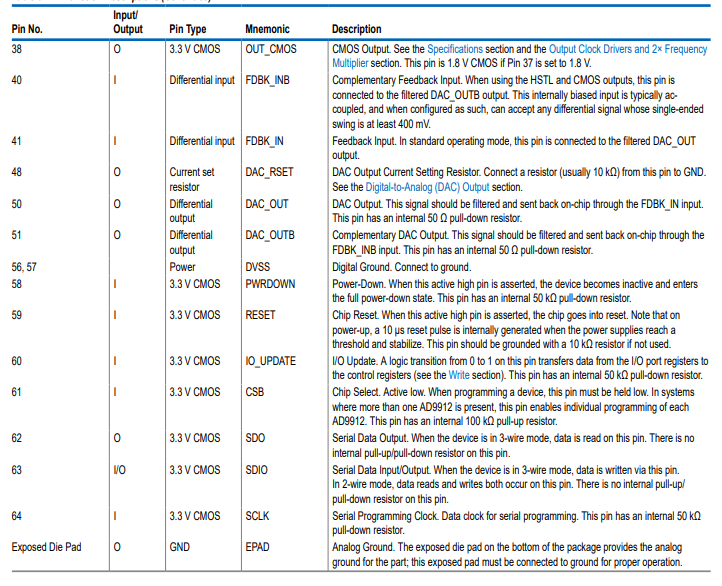

引脚配置描述

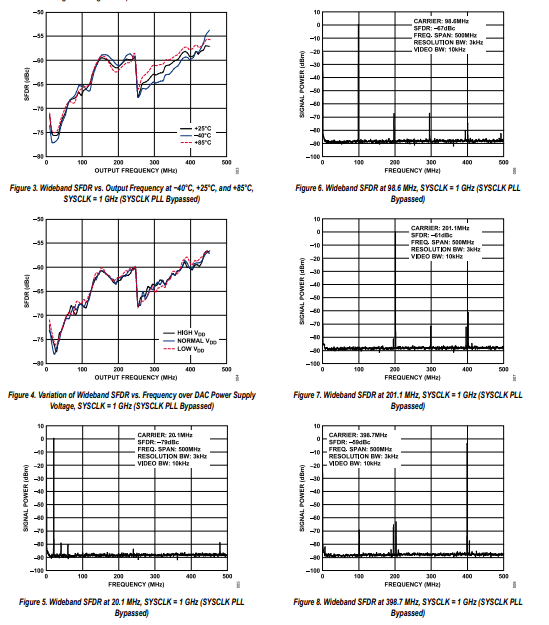

典型性能特征

操作理论

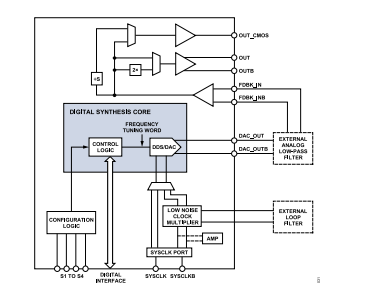

图39. 详细框图

AD9912是一款高性能、低噪声的14位直接数字频率合成器(DDS)时钟合成器,集成了比较器,适用于需要产生灵活、精细调谐的方波或正弦波输出信号的应用。通过直接数字合成器(DDS)与集成数模转换器(DAC),实现了数控振荡器(DCO)功能,由系统时钟驱动。

该器件采用基于锁相环(PLL)的倍频器,可使用低成本、低频源作为系统时钟。为获得最佳抖动性能,应绕过系统时钟PLL,并提供低噪声、高频系统时钟。根据采样理论,DDS的输出频率上限为采样时钟频率(fs)的50%(fs为DAC采样速率),但实际应用中,通常建议上限为40%fs,以确保所需片外重构滤波器的选择性。

重构滤波器的输出信号可反馈至AD9912进行进一步处理。输出电路包括HSTL和CMOS输出缓冲器,以及频率倍增器,适用于需要高于DDS奈奎斯特频率的应用。

AD9912还提供预编程的频率配置文件,允许用户在无需编程器件的情况下进行频率调谐。以下各节将分别介绍各个功能模块。

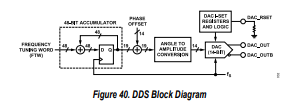

直接数字合成器(DDS)

DDS生成的正弦波频率由频率调谐字(FTW)确定(即数字值)。与模拟正弦波发生器不同,DDS使用数控模块并在采样系统中运行。因此,它需要一个采样时钟(fs),作为DDS的基本定时源。累加器相当于一个模数为2^48的计数器,其可编程步长由频率调谐字(FTW)决定。DDS的框图如图40所示。

DDS的输入是一个48位的FTW,为累加器提供速率值。在每个fs周期,累加器将FTW的值加到其运行总和上。例如,给定FTW = 5,累加器在每个fs周期将增加5。当累加器达到其容量上限(在这种情况下为2^48 )时,它会溢出并回滚,保留溢出部分。累加器回滚的平均速率决定了输出正弦波的频率。以下公式定义了累加器的回滚速率,并确定了DDS的输出频率(fDDS):

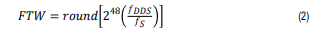

对该公式求解FTW可得:

例如,给定fs = 1 GHz,fDDS = 19.94 MHz,则FTW = 5,471,873,547.255(0x04FA05143B7F )。

-

AD9912:高性能直接数字合成器的深度解析2026-04-16 65

-

AD9914 3.5 GSPS直接数字频率合成器,内置12位数模转换器技术手册2025-05-06 1463

-

1 GSPS直接数字频率合成器AD9858概述2023-04-13 1132

-

带14位DAC合成器AD9912英文手册2022-11-29 648

-

UG-475:评估采用14位DAC的AD9912 1 GSPS直接数字频率合成器2021-05-27 1083

-

AD9915: 2.5 GSPS直接数字频率合成器,内置12位数模转换器数据手册2021-03-19 913

-

高性能16位数模转换器AD9164怎么样?2019-10-23 3156

-

AD9914BCPZ数字频率合成器产品介绍2019-06-17 1655

-

AD9914BCPZ直接数字频率合成器2019-04-29 1512

-

使用AD9912直接数字频率合成器的AD9912A/PCBZ评估板2019-02-28 2872

-

3.5 GSPS直接数字频率合成器AD9914的优势特性2018-10-15 2742

全部0条评论

快来发表一下你的评论吧 !