AD9854 CMOS 300 MSPS正交完整DDS技术手册

描述

概述

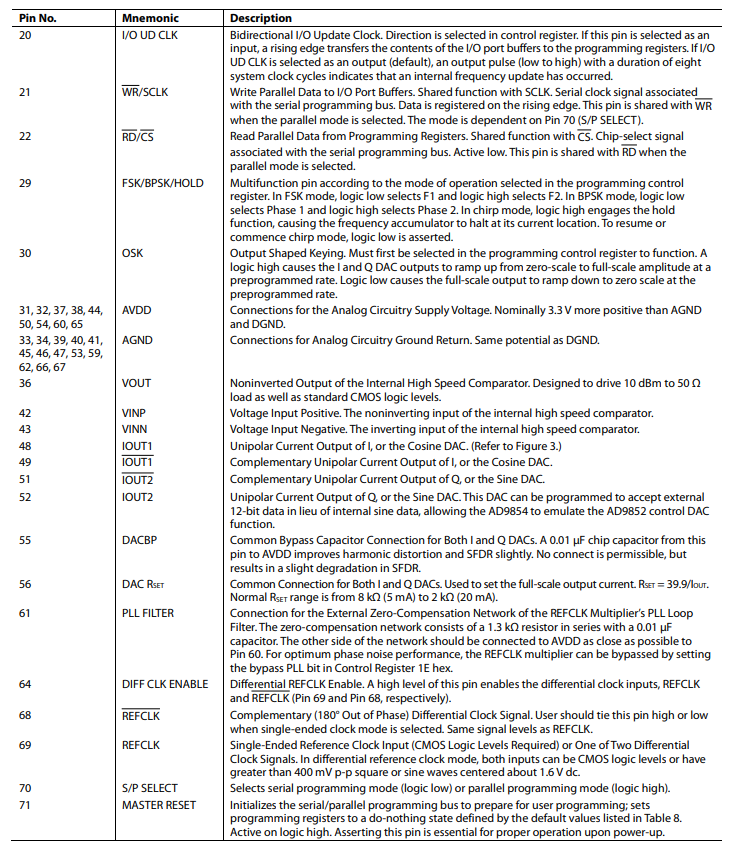

AD9854 数字频率合成器是一款高度集成的套件,该套件使用高级 DDS 技术,外加两个内部高速、高性能正交 DAC,构成可数字化编程的 I 和 Q 频率合成器功能。在以精确时钟源为基准时,AD9854 可生成高度稳定的频率、相位和幅度可编程正弦和余弦输出,在通信、雷达和许多其他应用中用作捷变 LO。AD9854 的创新型高速 DDS 内核提供 48 位频率分辨率(使用 300 MHz SYSCLK 时,调谐分辨率为 1 μHz)。为相位-幅度转换保持 16 位分辨率可确保出色的无杂散动态范围 (SFDR)。

数据表:*附件:AD9854 CMOS 300 MSPS正交完整DDS技术手册.pdf

AD9854 的电路架构允许以高达 150 MHz 的频率生成同步正交输出信号,并且能够以高达每秒 1 亿次的新频率对这些输出信号进行数字化调谐。对于捷变时钟发生器应用,可以通过内部比较器将(外部滤波的)正弦波输出转换为方波。此套件提供两个 14 位相位寄存器和单个引脚用于 BPSK 操作。

对于更高阶的 PSK 操作,可以将 I/O 接口用于相变。12 位 I 和 Q DAC 与创新型 DDS 架构结合后,可以提供出色的宽带和窄带输出 SFDR。如果不需要正交功能,则还可以将 Q DAC 配置为用户可编程的控制 DAC。在配置有比较器的情况下,12 位控制 DAC 有助于在高速时钟发生器应用中实现静态占空比控制。

两个 12 位数字倍频器允许对正交输出进行可编程幅度调制、开/关输出形状调整键控和精密幅度控制。还包括线性调频功能,以促进实现宽带宽扫频应用。AD9854 的可编程 4× 至 20× REFCLK 倍频器电路可在内部从较低频率的外部基准时钟生成 300 MHz 的系统时钟。这可省去用户实施 300 MHz 系统时钟源的费用和困难。

直接 300 MHz 时钟还适应单端或差分输入。支持斜升 FSK 的单引脚传统 FSK 和增强频谱质量。AD9854 使用高级 0.35 µm CMOS 技术,在使用单一 3.3 V 电源的情况下提供高级功能。

AD9854 与 AD9852 单信号音频率合成器之间具有引脚兼容性。它可在 −40°C 至 +85°C 的扩展工业温度范围内工作。

应用

- 捷变正交 LO 频率合成

- 可编程时钟发生器

- 用于雷达和扫描系统的 FM 线性调频源

- 测试与测量设备

- 商用和业余 RF 激励器

特性

- 300 MHz内部时钟速率

- FSK、BPSK、PSK、线性调频、AM操作

- 两个集成式12位数模转换器(DAC)

- 超高速比较器,均方根抖动:3 ps

- 出色的动态性能

- 80 dB SFDR(A

OUT为100 MHz,±1 MHz时)

- 80 dB SFDR(A

- 4×至20×可编程参考时钟倍频器

- 两个48位可编程频率寄存器

- 两个14位可编程相位偏移寄存器

- 12位可编程幅度调制和开关输出形键控功能

- 单引脚FSK和BPSK数据接口

- 通过输入/输出接口提供PSK功能

- 线性或非线性FM线性调频功能,具有单引脚频率保持功能

- 升频FSK

- 在时钟发生器模式下总抖动<25 ps rms

- 自动双向频率扫描

- Sin(x)/x校正

- 简化控制接口

- 兼容10 MHz串行2线或3线SPI

- 100 MHz并行8位编程

- 3.3 V单电源

- 多种关断功能

- 单端或差分输入参考时钟

- 小型80引脚LQFP或TQFP封装,带裸露焊盘

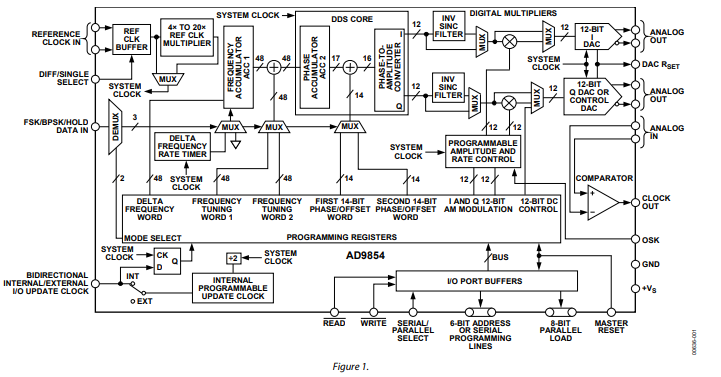

框图

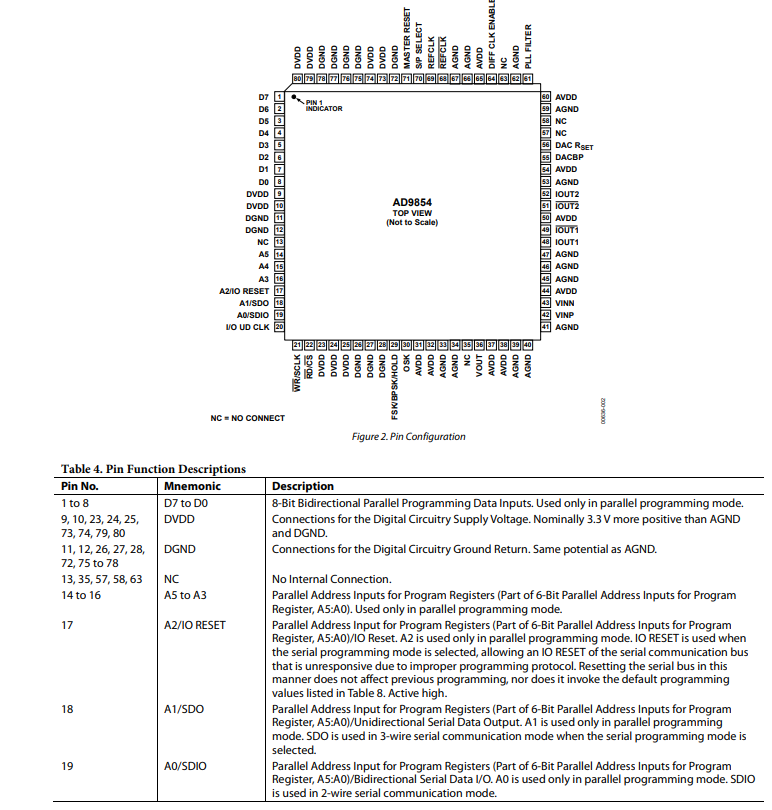

引脚配置描述

典型性能特征

典型应用

工作原理

AD9854正交输出数字合成器是一款高度灵活的器件,适用于广泛的应用领域。该器件由一个48位相位累加器、一个可编程参考时钟乘法器、反混叠滤波器、数字乘法器、两个12位/300 MHz数模转换器(DAC)、一个高性能模拟比较器以及接口逻辑组成。这款高度集成的器件可配置为合成本地振荡器(LO)、灵活的时钟发生器,或频移键控/二进制相移键控(FSK/BPSK)调制器。

如需了解该器件功能模块的工作原理,请参阅模拟器件公司(Analog Devices)关于数字信号合成的技术教程。该教程包含器件的技术说明、信号通过DDS的流程,以及各种数字合成实现的基本应用信息。此文档《数字信号合成技术教程》可在DDS技术文库(DDS Technical Library)获取,网址为www.analog.com/dds 。

工作模式

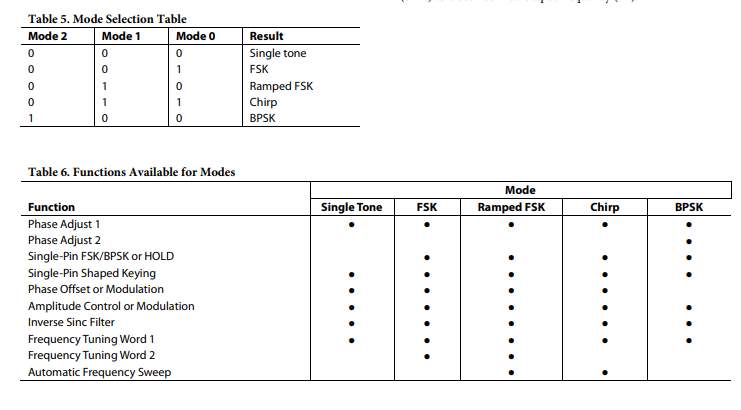

AD9854有五种可编程工作模式。要选择一种模式,控制寄存器(并行地址1Eh)中的三位必须按表5所示进行编程。

在每种模式下,某些功能可能会被禁用。表6列出了每种模式下的功能及其可用性。

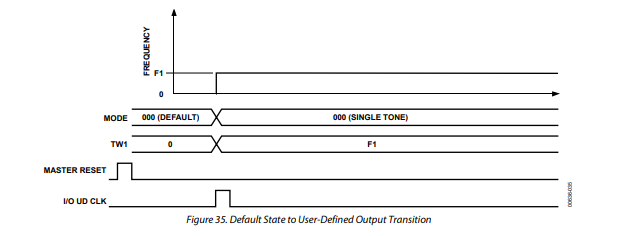

单音模式(模式000)

这是默认模式,当主复位(MASTER RESET)引脚置位时生效。如果用户在控制寄存器中对该模式进行编程,也可以访问此模式。相位累加器负责生成输出频率,其值由频率调谐字I寄存器提供的48位数值确定,这些寄存器的默认值为0。其余适用寄存器的默认值进一步决定了单音输出信号的特性。

主复位后的默认值将器件配置为输出频率为0 Hz且相位为零的信号。在上电和复位时,I通道和Q通道DAC的输出为直流值,等于中间刻度输出电流。这是默认的幅度设置0.0。有关输出幅度控制的更多详细信息,请参阅“输出幅度键控(OSK)”部分。28个控制寄存器中的全部或部分必须进行编程,才能产生用户定义的输出信号。

图35展示了从默认状态(0 Hz)到用户定义输出频率(F1)的转换情况。

-

AD9854:高性能CMOS 300 MSPS正交直接数字频率合成器的技术剖析2026-04-16 337

-

正交DDS信号的上变频基波输出挑战2019-04-04 6356

-

求AD9854产生正交信号的程序分享2018-10-31 1908

-

DDS芯片AD9854测试报告2018-10-29 2463

-

STM32的AD9854 DDS模块调试该怎么做?2018-08-28 2378

-

STM32的AD9854 DDS模块调试总结2018-05-16 20250

-

基于AD9854的信号发生器设计2017-12-09 9091

-

DDS工作原理及基于AD9854的信号发生器的设计2017-11-16 1945

-

ad9854调试使用心得2017-11-03 5402

-

CMOS 300MSPS完整的数字显示示波器AD9854数据表2017-10-19 1103

-

基于DDS芯片AD9854的信号产生器设计2017-08-13 1536

-

基于AD9854的DDS外围电路设计和程序2016-06-17 1382

-

DDS芯片AD9854及其在扩频通信中的应用_胡淑均2016-05-09 1233

-

【DIY信号发生器】AD9854方案2014-06-17 6917

全部0条评论

快来发表一下你的评论吧 !