AD5932可编程单扫描波形发生器技术手册

描述

概述

AD5932是一款提供可编程频率扫描的波形发生器。这款器件采用支持增强型频率控制的嵌入式数字处理技术,能够生成合成的模拟或数字频率步进波形。采用预先编程的频率配置文件可以避免连续的写周期,从而释放了重要的DSP/微控制器资源。波形从已知相位开始,并可以连续地增加相位,因此能够轻松的确定相移。AD5932功耗仅为6.7 mA,为波形产生提供方便的低功耗解决方案。

数据表:*附件:AD5932可编程单扫描波形发生器技术手册.pdf

AD5932在目标范围内的定义时长内输出各频率,然后在扫描范围内步入下一频率。可对该器件输出特定频率的时长进行预先编程并让器件自动递增该频率;或者,频率通过CTRL引脚进行外部递增。在范围结束时,AD5932继续输出最后一个频率直至重置器件。另外,AD5932还通过MSBOUT引脚提供数字输出。

对AD5932进行编程时,用户需要输入起始频率、频率步进、增量数量,以及器件输出各频率的时间间隔。频率扫描配置文件可通过切换CTRL引脚来启动和执行。

AD5932通过三线式串行接口写入数据,能够在高达40 MHz的时钟速率下工作。该器件采用2.3 V至5.5 V电源供电。

请注意,AVDD和DVDD彼此独立并可采用不同的电压工作。AD5932还具有待机功能,能够关断器件中没有使用的部分。

AD5932提供16引脚、无铅TSSOP封装。

应用

- 频率扫描/雷达

- 网络/阻抗测量

- 增量式频率激励

- 传感器应用

– 近距和运动

特性

- 可编程频率配置文件;无需外部元件

- 输出频率高达25 MHz

- 预编程的频率配置文件能将DSP/微控制器的写操作次数减到最少

- 正弦波/三角波/方波输出

- 频率步进的自动或单引脚控制

- 关断模式:20 µA

- 电源:2.3 V至5.5 V

- 汽车应用温度范围:-40°C至+125°C

- 16引脚、无铅TSSOP封装

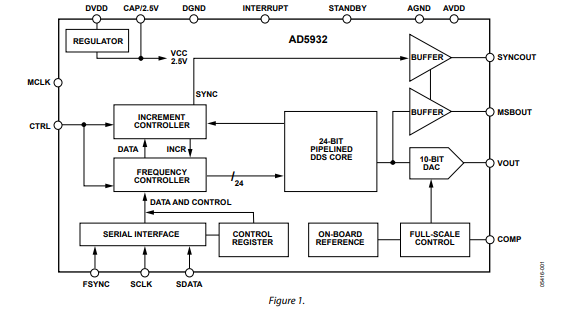

框图

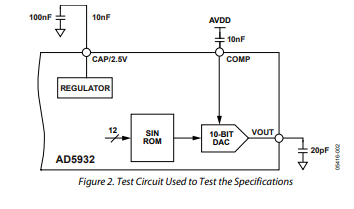

规格测试电路

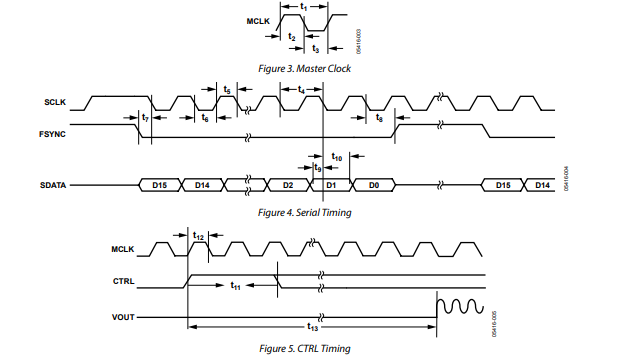

主时钟和时序图

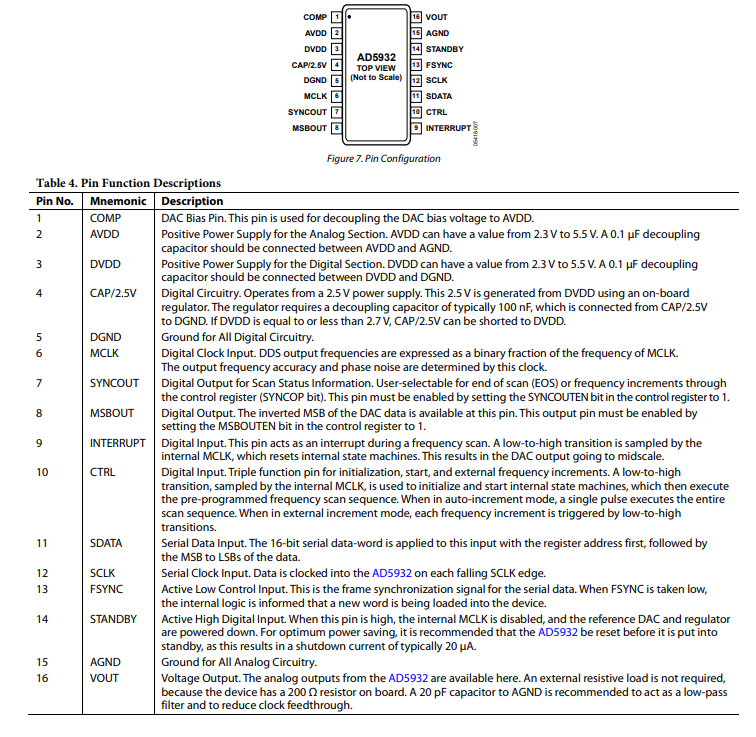

引脚配置描述

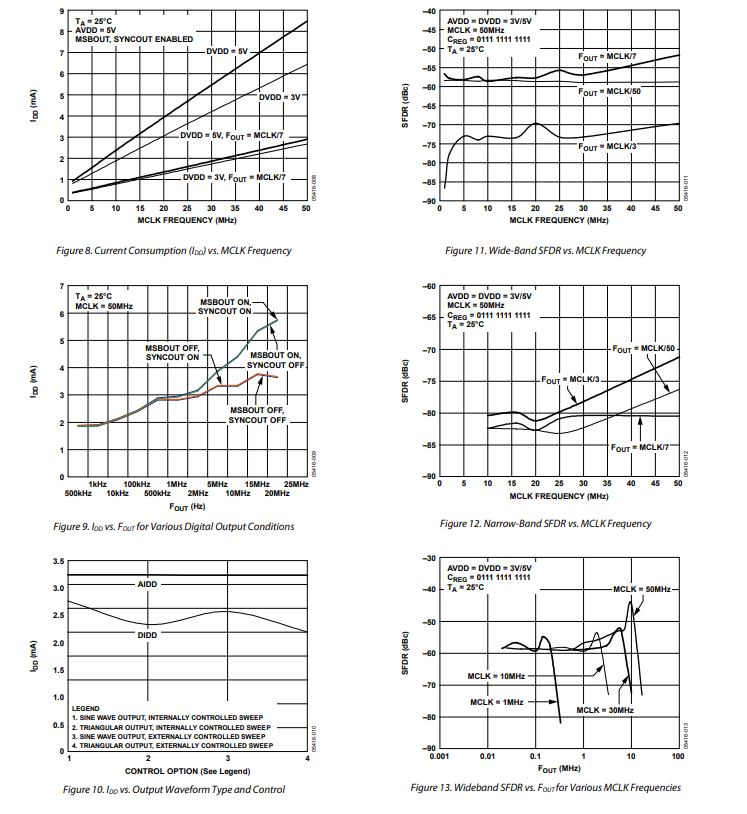

典型性能特征

工作原理

AD5932是一款通用型合成波形发生器,能够提供数字可编程波形,涵盖频率和时域范畴。该器件内置嵌入式频率处理功能,可对用户可编程的频率曲线进行扫描,从而增强频率控制能力。由于该器件具备预编程特性,它能从数字信号处理器(DSP)/微控制器的连续写周期中解脱出来,以生成特定波形。

频率曲线

频率曲线由起始频率(FSTART)、频率增量(Δf)和频率扫描中的增量数(NSTEP)定义。频率增量之间的时间间隔(TINT),可由器件自动确定(自动增量模式),也可通过硬件引脚(外部增量模式)进行外部控制。对于自动更新,时间间隔可以是固定数量的时钟周期,或是固定数量的输出波形周期。

在自动增量模式下,CTRIL引脚的单个脉冲会启动并执行频率扫描。在外部增量模式下,CTRIL引脚同样会启动扫描,但频率增量间隔由CTRIL引脚上连续0/1转换之间的时间间隔决定。

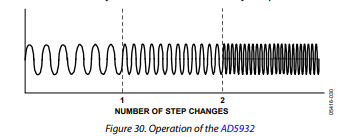

图30展示了一个2步频率扫描的示例。请注意,AD5932的频率输出信号是连续可用的,因此在所有频率增量下相位都是连续的。

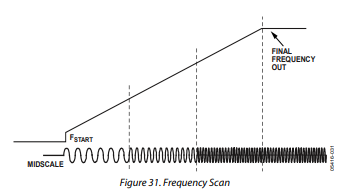

当AD5932完成从起始频率到最终频率的频率扫描时(见图31),从FSTART开始,以增量方式增加(FSTART + NSTEP × Δf),它会持续输出扫描中的最后一个频率。需注意,频率扫描时间由(NSTEP + 1)× TINT给出。

串行接口

AD5932具有标准的三线串行接口,与SPI*、QSPI*、MICROWIRE*和DSP接口标准兼容。

在串行时钟输入SCLK的控制下,数据以16位字的形式加载到器件中。此操作的时序图如图4所示。

FSYNC输入是一个电平触发输入,起到帧同步和芯片使能的作用。只有在FSYNC为低电平时,才能将数据传输到器件中。要开始串行数据传输,FSYNC应拉低,并遵循最小的FSYNC到SCLK下降沿建立时间ts。在FSYNC变为低电平后,在SCLK的下降沿,数据会移入器件的输入移位寄存器。在第16个SCLK下降沿之后,FSYNC可以拉高,但需遵循最小的SCLK到FSYNC上升沿建立时间tu。或者,FSYNC可以在多个16个SCLK脉冲期间保持低电平,然后在数据传输结束时拉高。这样,FSYNC就是一个连续的16位字的数据流。在这种情况下,FSYNC应在第16个SCLK下降沿之后拉高。最后一个字只能在FSYNC拉高后加载。

SCLK可以是连续的,或者,SCLK可以空闲为高电平或低电平,以进行写操作。

给AD5932上电

AD5932上电时,器件处于未定义状态,因此在使用前必须进行复位。七个寄存器(控制寄存器和频率寄存器)必须重置为已知值。控制寄存器组应是用户编程的第一个寄存器,这样可以设置器件。需注意,对控制寄存器的写入会自动重置内部状态机,并提供模拟输出的中间刻度,因为它与INTERRUPT引脚执行相同的功能。通常,接下来是加载所有所需的频率参数。在频率扫描开始之前,DAC输出保持在中间刻度,直到在CTRIL引脚处触发。

-

AD9833低功耗可编程波形发生器:特性、应用与工作原理2026-04-16 347

-

可编程频率扫描波形发生器AD5932:特性、应用与设计指南2026-04-14 61

-

AD9833:低功耗可编程波形发生器的卓越之选2026-03-03 285

-

AD5930可编程频率扫描及输出突发波形发生器技术手册2025-05-06 1234

-

AD5930:可编程扫频和输出猝发波形发生器数据表2021-04-23 1076

-

AN-260:使用数字可编程延迟发生器2021-04-14 868

-

AN-1044: 将AD5932编程为扫频输出和单频输出2021-03-21 665

-

AD9837: 低功耗、8.5 mW、2.3 V至5.5 V可编程波形发生器2021-03-19 827

-

AD5932 可编程单扫描波形发生器2019-02-22 898

-

AD9833型高精度可编程波形发生器及其应用2016-01-22 1684

-

基于DDS的可编程的波形发生器2015-11-02 700

-

AD9833型高精度可编程波形发生器设计方案2010-02-26 7079

-

基于AD9833的高精度可编程波形发生器系统设计2009-05-26 1335

-

可编程脉冲发生器电路图2009-04-07 1579

全部0条评论

快来发表一下你的评论吧 !