AD9835 50MHz直接数字频率合成器、波形发生器技术手册

描述

概述

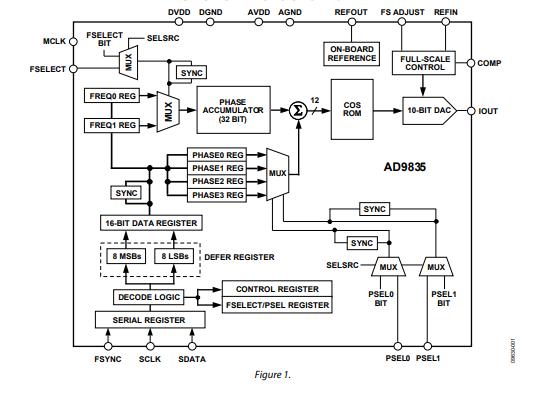

AD9835是一款数控振荡器,在单个CMOS芯片内集成了一个相位累加器、一个COS查找表以及一个10位数模转换器,提供相位调制和频率调制两种调制能力。

最高支持50 MHz时钟速率。频率控制精度可达40亿分之一。调制通过串行接口载入寄存器来实现。用户可使用一个关断位在不用时关断AD9835,将功耗降低至1.75 mW。

该器件采用16引脚TSSOP封装。

数据表:*附件:AD9835 50MHz直接数字频率合成器、波形发生器技术手册.pdf

应用

- 频率激励/波形发生

- 频率相位调谐和调制

- 低功耗RF/通信系统

- 液体和气流测量

- 传感器应用:接近度、运动和缺陷检测

- 测试与医疗设备

特性

- 5 V电源

- 50 MHz速度

- 片内COS查找表

- 片内10位DAC

- 串行载入

- 关断选项

- 温度范围:−40°C至+85°C

- 200 mW功耗

- 16引脚TSSOP封装

框图

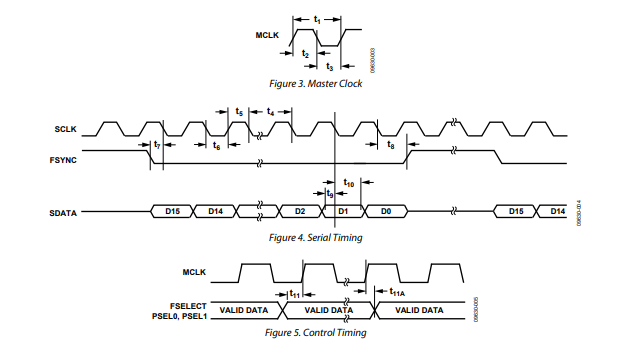

时序图

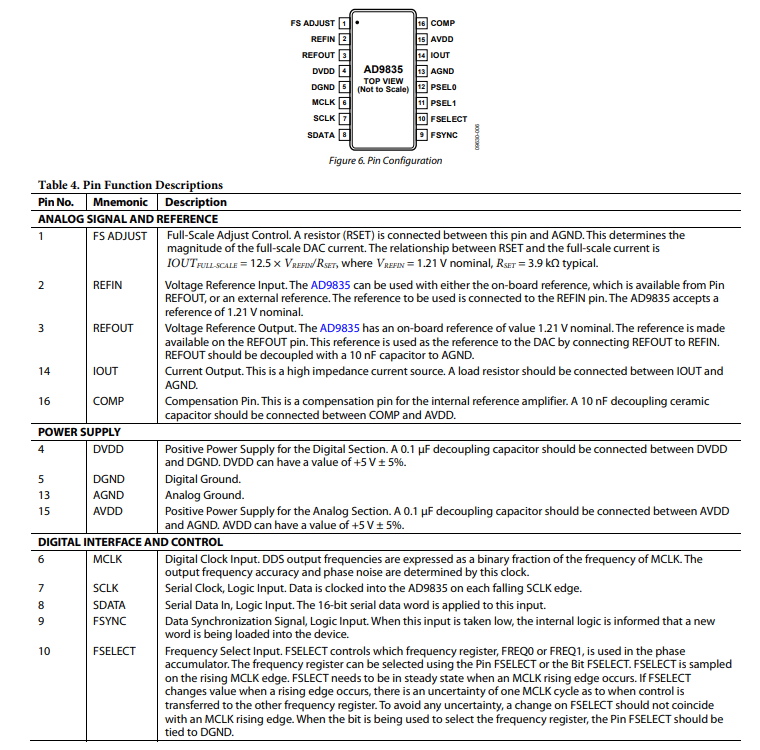

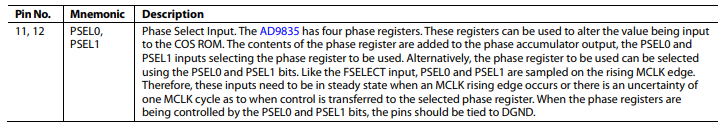

引脚配置描述

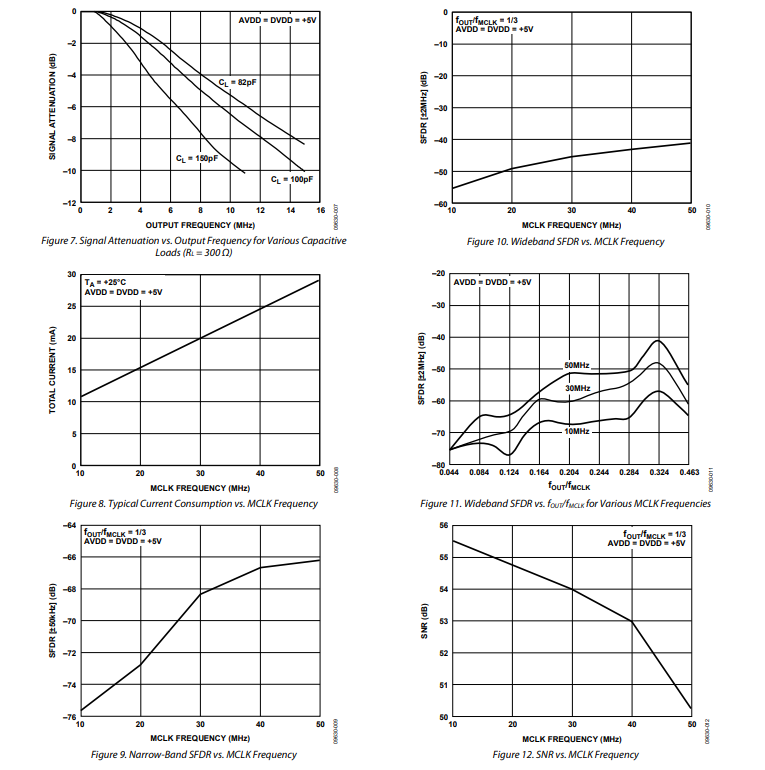

典型性能特征

应用信息

AD9835具备的功能使其适用于调制应用。该器件可用于执行简单的调制,如频移键控(FSK)。更为复杂的调制方案,如高斯最小移频键控(GMSK)和正交相移键控(QPSK),也可通过AD9835来实现。

在FSK应用中,AD9835的两个频率寄存器会被加载不同的值,其中一个频率代表频移空间频率,另一个则代表标记频率。数字数据流中的FSELECT引脚会使AD9835在这两个值之间对载波频率进行调制。

AD9835有四个相位寄存器,这使该器件能够实现相移键控(PSK)。在PSK调制中,载波频率的相位会发生偏移,偏移量与输入到调制器的比特流相关。四个移位寄存器的存在,简化了数字信号处理器(DSP)与AD9835之间所需的交互。

AD9835也适用于信号发生器应用。鉴于其低电流消耗特性,该器件适用于可用作本地振荡器的应用。

接地与布局

承载AD9835的印刷电路板在设计时,应确保模拟部分和数字部分相互分离并限定在特定区域内。这有助于实现接地层的分离,而这是一种普遍认为能为接地平面提供最佳屏蔽效果的技术。数字接地平面和模拟接地平面应仅在一处连接。对于AD9835而言,是唯一需要进行AGND(模拟地)到DGND(数字地)连接的器件,其AGND引脚和DGND引脚应进行连接。如果在一个系统中,多个器件都需要AGND到DGND的连接,那么连接点应仅设置一个,并且应尽可能在靠近AD9835的位置建立稳定的接地路径。

应避免在器件下方布设数字线路,因为这些线路会引入噪声。模拟接地平面应在AD9835下方铺设,以防止噪声耦合。为AD9835供电的电源线应尽可能宽,以便降低阻抗,并减少电源线上的尖峰噪声。像时钟信号这类快速开关信号,应使用数字接地进行屏蔽,以避免其向电路板的其他部分辐射噪声。

要防止数字信号与模拟信号交叉。电路板两侧的走线应相互垂直,以减少馈通效应。在双层板中,微带线技术通常是最佳选择,但并非总是可行,因为电路板的另一侧往往要专门用于接地平面,而信号则布置在另一侧。

良好的去耦至关重要。AD9835的模拟电源和数字电源相互独立,分别引出,以尽量减少模拟部分与数字部分之间的耦合。所有模拟电源和数字电源都应进行去耦处理,将AGND和DGND分别与0.1 μF陶瓷电容并联10 μF钽电容 。为实现最佳的去耦性能,这些电容应尽可能靠近器件放置,理想情况是紧贴器件。在使用同一电源为AD9835的AVDD(模拟电源)引脚和DVDD(数字电源)引脚供电的系统中,建议采用系统电源旁路。推荐在AVDD引脚处采用模拟电源去耦,在DGND引脚与DVDD引脚之间采用数字电源去耦。

将AD9835与微处理器连接

AD9835具有标准串行接口,可使其直接与多个微处理器连接。该器件使用外部串行时钟将数据或控制信息写入内部。串行时钟的频率最高可达20 MHz。串行时钟可以是连续的,也可根据需要空闲或保持低电平。每次向AD9835写入数据时,FSYNC(帧同步)信号都会被拉低,并保持低电平状态,直至16位数据写入完成。FSYNC信号用于将加载到AD9835中的16位信息成帧。

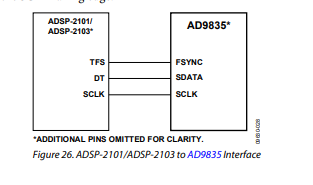

AD9835与ADSP - 21XX接口

图26展示了AD9835与ADSP - 21xx之间的串行接口。ADSP - 21xx应设置为在SPORT传输交替成帧模式(FSTW = 1)下运行。ADSP - 21xx应按如下方式配置:内部时钟操作(ISCLK = 1),16位字长(SLEN = 15),内部帧同步信号(ITFS = 1),并生成帧同步信号(TFSR = 1)。

通过将字写入Tx寄存器来启动传输。数据在串行时钟的上升沿输出,并在AD9835中通过SCLK的下降沿进行时钟控制。

-

AD9835:一款高性能的直接数字合成器2026-04-16 426

-

DDS直接数字频率合成器、信号发生器、函数发生器2022-03-24 16442

-

AD9832:25 MHz直接数字合成器,波形发生器数据表2021-05-08 1083

-

AD9835:50 MHz直接数字合成器,波形发生器数据表2021-04-17 938

-

EVAL-AD9835EBZ描述了AD9835直接数字频率合成器(DDS)的评估板2019-10-29 1990

-

怎么设计直接数字频率合成器?2019-08-21 1712

-

什么是频率合成器2019-08-19 5782

-

基于DDS的频率合成器设计介绍2019-07-08 3049

-

AD9914BCPZ数字频率合成器产品介绍2019-06-17 1674

-

AD9914BCPZ直接数字频率合成器2019-04-29 1547

-

AD9835 50 MHz 直接数字频率合成器、波形发生器2019-02-22 1015

-

基于FPGA的直接数字频率合成器的设计2010-08-09 566

-

一种基于DDS芯片AD9835的多种信号发生器2009-08-19 1188

全部0条评论

快来发表一下你的评论吧 !