AD9851 180MHz完整DDS频率合成器技术手册

描述

概述

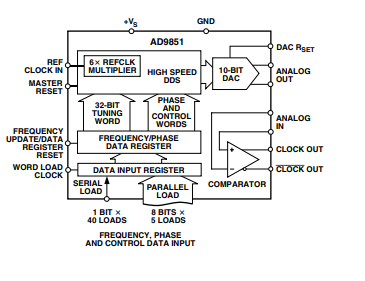

AD9851是一款高度集成的器件,采用先进的DDS技术,内置一个高速、高性能数模转换器和比较器,共同构成数字可编程频率合成器和时钟发生器。以精密时钟源作为基准时,AD9851能产生一个频率稳定、相位可编程的数字化模拟输出正弦波。该正弦波可以直接用作频率源,或在内部转换为适合捷变时钟发生器应用的方波。

AD9851的创新型高速DDS内核提供一个32位频率调谐字;对于180 MHz基准时钟,输出调谐分辨率可以达到0.040 Hz。AD9851内置独特的X6基准时钟乘法器电路,无需高速参考振荡器。该6X PLL乘法器对无杂散动态范围(SFDR)和相位噪声特性的影响极小。该器件还提供5位数字控制相位调制,使其输出能够以180°、90°、45°、22.5°、11.25°及其任意组合的增量发生相移。

数据表:*附件:AD9851 180MHz完整DDS频率合成器技术手册.pdf

特性

- 180 MHz时钟速率,具有可选6x基准时钟乘法器

- 片内高性能10位DAC和具迟滞特性的高速比较器

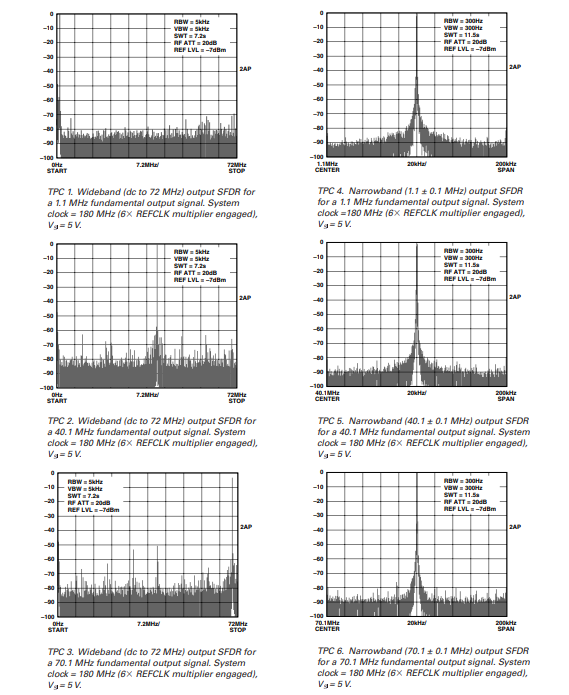

- SFDR >43 dB (70 MHz AOUT)

- 32位频率调谐字

- 简化的控制接口:并行或串行异步加载格式

- 5位相位调制与偏移能力

- 比较器抖动:小于80 ps 峰峰值 (20 MHz)

- 2.7 V至5.25 V单电源供电

- 低功耗:555 mW (180 MHz)

- 省电功能:4 mW (2.7 V)

- 超小型28引脚SSOP封装

框图

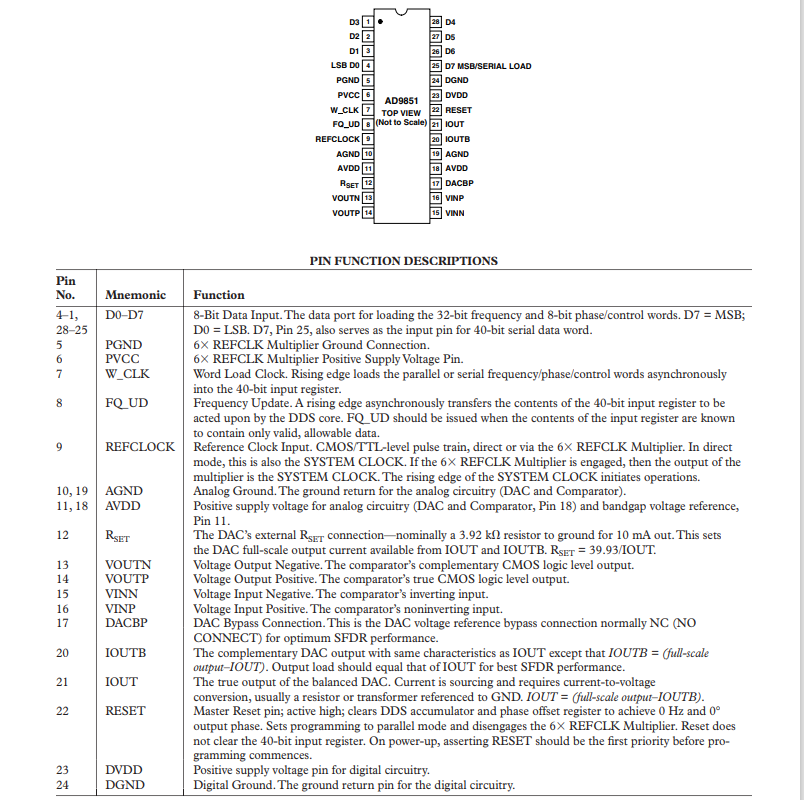

引脚配置描述

典型性能特征

工作原理与应用

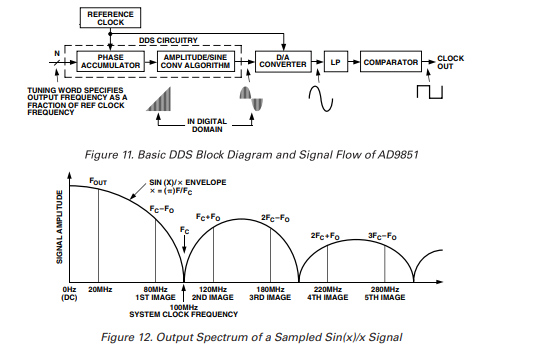

AD9851采用直接数字合成(DDS)技术,通过数控振荡器(NCO)生成频率/相位可调的正弦波。数字正弦波通过内部10位高速数模转换器(D/A转换器)转换为模拟正弦波。板载高速比较器可将模拟正弦波转换为低抖动、与TTL/CMOS兼容的输出方波。DDS技术是一种创新的电路架构,允许完全数字控制频率、相位和幅度,从而实现高分辨率的增量输出频率选择。AD9851在180 MSPS的频率下可实现约0.04 Hz的频率分辨率。用户可选择直接使用参考时钟,或启用6倍REFCLK乘法器。AD9851的输出波形始终是连续的,一个输出频率的变化不会影响另一个频率。

AD9851的基本功能框图和信号流程如图11所示。

DDS电路本质上是一个数字频率合成器,其增量分辨率由系统时钟和相位累加器调谐字中的位数(N)决定。相位累加器是一个可变模计数器,每次接收到时钟脉冲时,其存储的值都会增加。当计数器达到满量程时,它会循环,使相位累加器的输出相位连续。调谐字设置计数器的模数,这实际上决定了每个时钟脉冲时相位累加器中添加的增量(Δ相位)的大小。添加的值越大,下一个时钟脉冲时相位累加器循环的速度就越快,从而导致输出频率越高。

AD9851采用创新的14位三角函数算法,以数学方式将32位相位累加器的值转换为10位量化幅度,并传递给DAC。该独特算法使用的查找表比传统方法少得多,有助于AD9851实现小尺寸和低功耗。

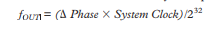

AD9851的输出频率、系统时钟和调谐字之间的关系由以下公式确定:

其中:

- ( Delta text{相位} ) = 32位频率调谐字的十进制值。

- 系统时钟 = 直接输入参考时钟(单位:MHz),若启用6倍REFCLK乘法器,则为输入时钟(单位:MHz)的6倍。

- ( f_{OUT} ) = 输出信号频率,单位为MHz。

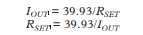

DDS内核的数字正弦波驱动内部高速10位D/A转换器,该转换器针对动态性能和低毛刺能量进行了优化,从而实现了AD9851的低杂散和低抖动性能。DAC可配置为单端(见图9和图10)、2倍输出或差分输出,输出值由以下表达式确定:

由于AD9851的输出是采样信号,其频谱遵循奈奎斯特采样定理。具体而言,其输出频谱包含基波加上采样时钟(fs)的整数倍频率的混叠信号。所选输出频率的图形表示如图12所示,显示了采样频谱与混叠图像的关系。正常可用带宽被认为从直流扩展到1/2系统时钟。

-

DS856直接数字频率合成器(DDS)替代AD9851,AD9858,AD9914S-CSL2025-04-24 4098

-

基于DDS的频率合成器设计介绍2019-07-08 3028

-

什么是频率合成器2019-08-19 5761

-

如何采用DDS实现频率合成器的设计?2021-04-20 1730

-

AD9850 DDS 频率合成器的原理及应用2008-04-10 1540

-

同步多个基于DDS的频率合成器AD98502011-11-29 914

-

DDS芯片AD9851在频率合成信号发生器中的应用2016-12-17 1400

-

基于DDS驱动PLL结构的宽带频率合成器的设计与实现2017-10-27 1250

-

ad9850和ad9851模块介绍2017-11-06 11949

-

AD9851 180 MHz完整DDS频率合成器2019-02-22 735

-

AD9851高集成度DDS频率合成器的电路原理图数据手册免费下载2019-04-30 1591

-

AD9850:CMOS,125 MHz完整DDS合成器数据表2021-04-18 817

-

AD9851数字信号合成变频资料分享2022-07-23 677

-

AN-587: 同步多个基于DDS的频率合成器AD9850/AD98512025-01-13 468

-

AD9851:高性能CMOS 180 MHz DDS/DAC合成器的深度解析2026-04-16 329

全部0条评论

快来发表一下你的评论吧 !