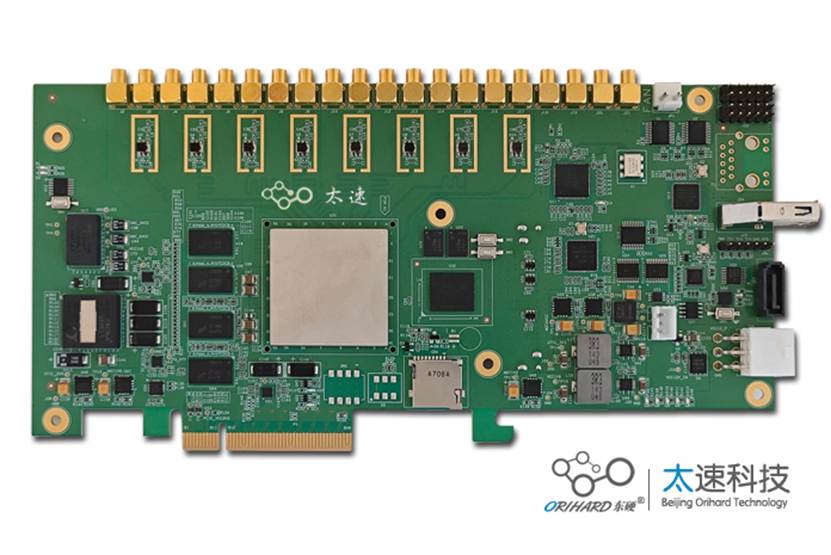

基于RFSOC的8路5G ADC和8路9G的DAC PCIe卡

电子说

描述

一、板卡概述

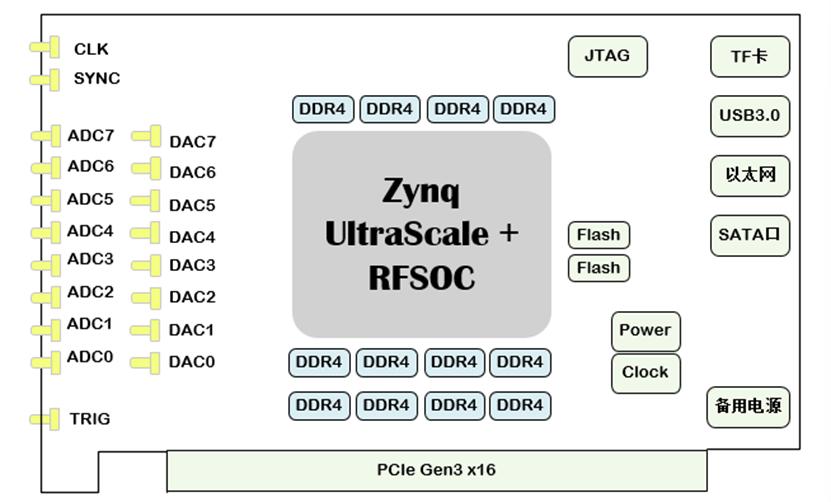

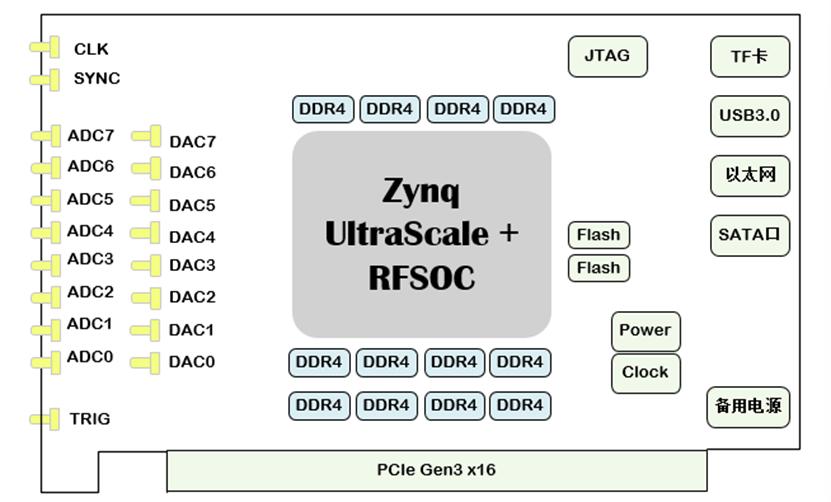

板卡使用Xilinx最新的第三代RFSOC系列,单颗芯片包含8路ADC和DAC,64-bit Cortex A53系列4核CPU,Cortex-R5F实时处理核,以及大容量FPGA。

对主机接口采用PCIe Gen4x8,配合PCIe DMA传输,支持高速数据采集和传输。

二、产品特性:

● 基于Zynq RFSoC系列FPGA,支持8路最高5G ADC和8路最高9G的DAC;

● 支持外部时钟输入1路, 外触发,外同步各1路;

● PL 1组64 bit 2400M DDR4,支持PL部分高速存储和处理。 单组4GB字节容量,PL部分8GB字节容量。

● 支持16个GPIO

PS部分内容:

● PS部分1组64bit位宽DDR4,单组4GB字节

● 可配置的Dual QSPI 加载

● 支持MicroSD卡加载

● 1000Base-T以太网(RJ45)端口(CPU端)

● USB接口支持,调试RS232 1路,

● 标准PCIe全高半长板型(167 x 111 mm ),适配常见主机、服务器

● PCIe Gen4 x8,高速数据通讯,附带DMA传输例程

软件开发内容:

接口

AD

DA

ARM AXI

DDR

PCIe

指标

8路

5Gbps

14bit

8路

9.85Gbps 14bit

DMA 传输

400MB/s

一组10GB/s,

共2组

PCIeX8 V4.0,8GB/s

PL部分,主要分为:

1,PCIe XDMA部分,PCIe分为寄存器通道和数据DMA通道,寄存器用于板卡控制和状态监控,。实现参考累加数的PCIe上传,实现8GB/秒传输。

2,DDR4读写参考程序。

3,RF硬件控制,用于控制板卡上PLL,ADC和DAC控制。

4,AD数据接口模块,实现AD数据采集入PL;

5,DA数据接口模块,实现DDS数据或者AD采集数据环回DA播出。

6,PL端 40路 IO的输入输出测试。

PS部分软件

ARM的DDR读写, SD卡,EMMC读写,Flash读写,网络和RS232读写。

Linux移植,甲方来完成。

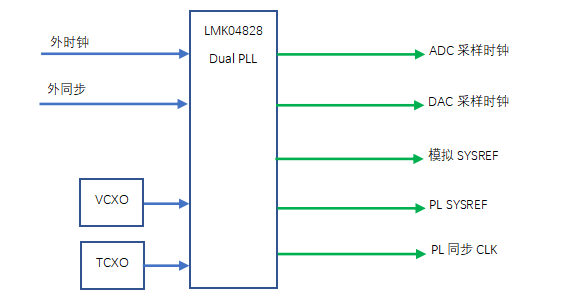

时钟设计:

板卡时钟灵活,支持多种应用配置,模拟部分的时钟,采用LMK04828,双PLL锁相环。

如果采用板内时钟,用TCXO和VCXO双锁相环,提供稳定可靠的模拟时钟。同时也输出一路给FPGA进行数字处理。

该方案也支持使用外部独立输入时钟,通过LMK04828扇出后输出给ADC和DAC。

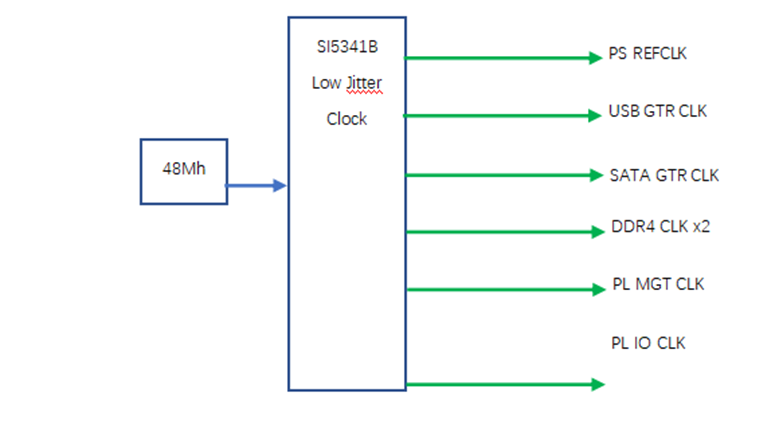

数字部分,使用高集成度的SI5341B,单路芯片输出PS和PL所需的各路时钟。

-

什么是5G NR?2017-05-03 237895

-

5G的8大关键技术2019-07-10 4216

-

PCIe数据卡设计资料第611篇:基于VU9P的双路5Gsps AD 双路6Gsps DA PCIe数据卡2022-01-25 703

-

iTOP-3399开发板5G方案展示 |迅为快讯2022-03-09 1863

-

迅为5G工业互联网方案RK3399开发平台2022-03-11 3419

-

iTOP-RK3399开发板支持Android8.1系统5G模块方案2022-04-14 2575

-

支持5G的开发板迅为RK3399开发板更支持4G全网通和物联网卡功能速速体验2022-05-07 3297

-

Xilinx ZYNQ UltraScale+RFSoCZU27DR 开源RFSOC算法验证评估板2023-08-25 2167

-

花火聚合路由器怎么样 支持4G和5G的8链路 叠加带宽2020-09-04 7023

-

ZU47DR-8通道ADC + 8通道DAC + 8x25G 6U VPX数据处理卡2024-04-10 4193

-

RFSOC47DR-8通道ADC + 8通道DAC 100G光纤卡2024-04-11 3875

-

基于RFSOC 27或47DR 8路ADC + 8路DA 6U VPX板卡2024-10-10 2501

-

高速数据采集卡设计方案:886-基于RFSOC的8路5G ADC和8路9G的DAC PCIe卡2025-04-08 1328

-

3U VPX板卡设计原理图:821-基于RFSOC的8路5G ADC和8路9G的DAC 3U VPX卡2025-12-18 625

全部0条评论

快来发表一下你的评论吧 !