AD9953 400 MSPS、14位DAC、1.8 V CMOS直接数字频率合成器技术手册

描述

概述、

AD9953是一款直接数字频率合成器(DDS),内置一个14位DAC,工作速度最高达400 MSPS。该器件采用先进的DDS技术,内置一个高速、高性能DAC,构成数字可编程的完整高频合成器,能够产生最高达200 MHz的频率捷变模拟输出正弦波。它包括一个集成1024 × 32静态RAM,支持多种模式下的灵活扫频功能。该器件专为提供快速跳频和精密调谐分辨率(32位频率调谐字)而设计。频率调谐字和控制字均通过串行I/O端口载入AD9953。

AD9953的额定工作温度范围为–40°C至+105°C扩展工业温度范围。

数据表:*附件:AD9953 400 MSPS、14位DAC、1.8 V CMOS直接数字频率合成器技术手册.pdf

应用

- VHF/UHF LO捷变频合成

- 雷达和扫描系统的FM线性调频源

- 非线性PSK/FSK调制器

- 测试与测量设备

特性

- 400 MSPS内部时钟速度

- 集成14位数模转换器

- 32位调谐字

- 相位噪声 ≤ –120 dBc/Hz(1 kHz偏移,DAC输出)

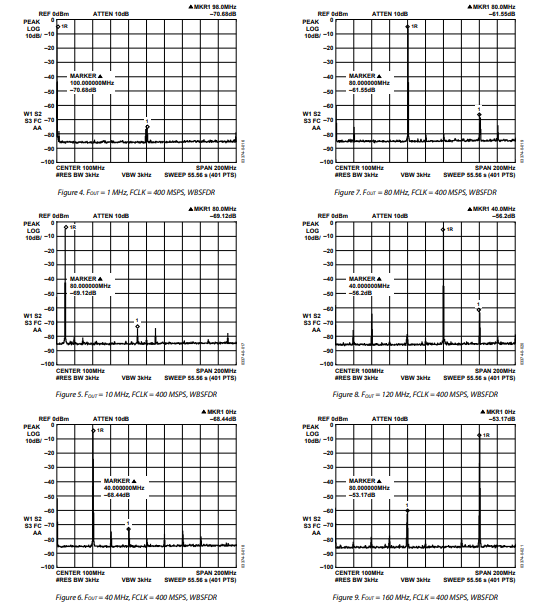

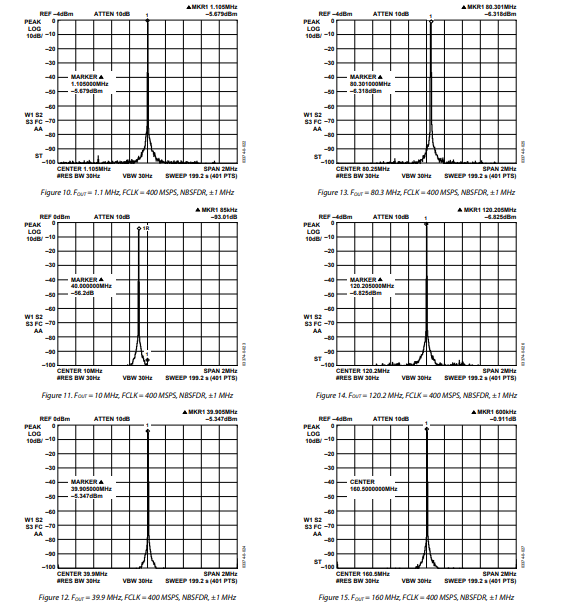

- 出色的动态性能>80 dB SFDR

(AOUT为160 MHz ± 100 kHz偏移时) - 串行I/O控制

- 1.8 V电源

- 软件与硬件控制省电功能

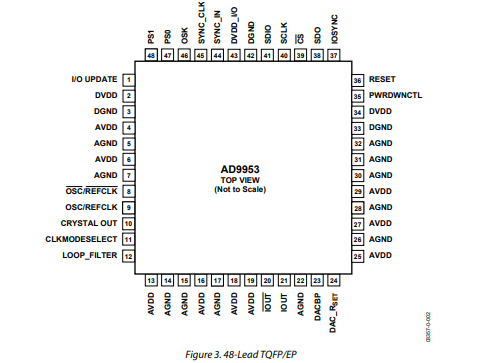

- 48引脚TQFP/EP封装

- 支持大部分数字输入的5 V输入电平

- PLL REFCLK乘法器(4x至20x)

- 欲了解更多特性,请参考数据手册

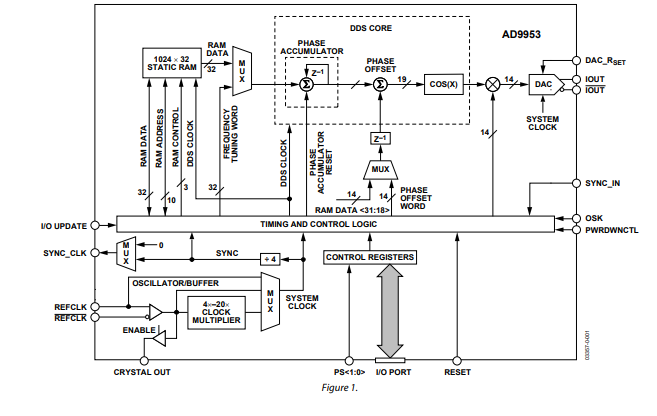

框图

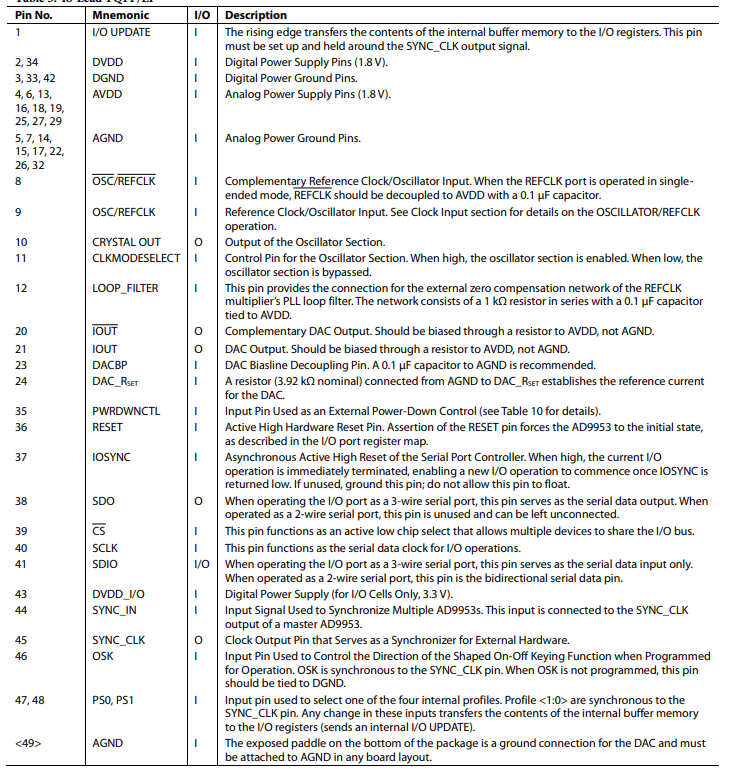

引脚配置描述

典型性能特征

工作原理

组件模块

直接数字合成(DDS)内核

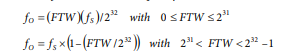

DDS 的输出频率 (f_o) 是系统时钟(SYSCLK)频率、频率调谐字(FTW)的值以及累加器容量(此处为 $2^{32}** )的函数。其确切关系如下,其中 **f_s$ 为 SYSCLK 的频率:

相位累加器的输出值通过 COS(x) 函数模块转换为幅度值,然后路由至数模转换器(DAC)。

在某些应用中,需要将输出信号强制设为零相位。仅将 FTW 设置为 0 无法实现此目的,因为这只会让 DDS 保持当前相位值。因此,需要一个控制位来将相位累加器输出强制设为零。

上电时,清零相位累加器位设为逻辑 1 ,但该位的缓冲存储器被清零(逻辑 0 )。因此,上电时,在首次发出 I/O 更新之前,相位累加器将保持清零状态。

锁相环(PLL)

PLL 可对 REFCLK 频率进行倍频。通过对控制功能寄存器 2 的 5 位 REFCLK 倍频器部分(位 <7:3>)进行编程来控制倍频操作。

当编程值范围在 0x04 到 0x14(十进制 4 到 20 )时,PLL 将 REFCLK 输入频率乘以相应的十进制值。不过,PLL 的最大输出频率限制为 400 MHz。每当 PLL 值发生变化时,用户需注意留出时间让 PLL 锁定(约 1 毫秒)。

通过编程一个不在 4 到 20(十进制)范围内的值可绕过 PLL。绕过 PLL 时,PLL 会关闭以节省功耗。

时钟输入

AD9953 支持多种时钟方法。支持差分或单端输入时钟,以及通过片上振荡器和/或锁相环(PLL)倍频器,这些均通过用户可编程位进行控制。AD9953 可配置为六种配置模式之一来生成系统时钟。

这些模式通过 CLKMODESELECT 引脚、CFR1<4> 和 CFR2<7:3> 进行配置。请注意,CLKMODESELECT 引脚符合 1.8 V 逻辑电平,将 CLKMODESELECT 引脚连接到逻辑高电平可启用片上晶体振荡器电路。启用片上振荡器后,将外部晶体与 AD9953 的 REFCLK 和 REFCLKB 输入相连,以生成 20 MHz 至 30 MHz 范围内的低频参考时钟。该振荡器生成的信号在传输到芯片其余部分之前会经过缓冲。此缓冲信号可通过 CRYSTAL OUT 引脚获取。CFR1<4> 位可用于启用或禁用缓冲器,从而开启或关闭系统时钟。振荡器本身在启动期间不会断电,以避免与开启晶体振荡器相关的长启动时间。将 CFR2<9> 写入逻辑高电平可启用晶体振荡器输出缓冲器;将 CFR2<9> 写入逻辑低电平可禁用振荡器输出缓冲器。

将 CLKMODESELECT 连接到逻辑低电平可禁用片上振荡器及其振荡器输出缓冲器。振荡器禁用后,必须由外部振荡器提供 REFCLK 和/或 REFCLKB 信号。对于差分工作模式,这些引脚由互补信号驱动。对于单端工作模式,应在未使用引脚与模拟电源之间连接一个 0.1 μF 电容器,以实现去耦。此外,PLL 可用于将参考频率乘以 4 到 20 范围内的整数。表 4 总结了时钟工作模式。请注意,PLL 倍频器由 CFR2<7:3> 位控制,与 CFR1<4> 位无关。

-

AD9953:高性能直接数字合成器的探秘与应用2026-04-16 70

-

AD9951 400 MSPS、14位DAC、1.8 V CMOS直接数字频率合成器技术手册2025-05-07 1435

-

AD9913低功耗、250 MSPS、10位DAC、1.8V CMOS直接数字频率合成器技术手册2025-05-06 1132

-

UG-475:评估采用14位DAC的AD9912 1 GSPS直接数字频率合成器2021-05-27 1083

-

AD9859:400 MSPS 10位、1.8 V CMOS直接数字合成器数据表2021-04-16 708

-

AD9953:400 MSPS,14位,1.8 V CMOS直接数字合成器数据表2021-04-15 713

-

AD9910: 1 GSPS、14位、3.3 V CMOS直接数字频率合成器2021-03-19 983

-

AD9914BCPZ直接数字频率合成器2019-04-29 1512

-

400MSPS,14位1.8伏CMOS直接数字频率合成器AD9953数据表2017-10-20 1081

-

GM4920:双通道800MSPS 14位直接数字频率合成器(DDS)2012-03-02 4909

-

AD9953,pdf datasheet (400 MSPS2009-10-24 982

全部0条评论

快来发表一下你的评论吧 !