AD9850 CMOS、125 MHz完整DDS频率合成器技术手册

描述

概述

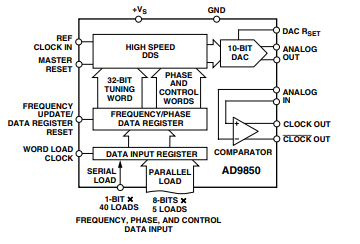

AD9850是一款高度集成的器件,采用先进的DDS技术,内置一个高速、高性能数模转换器和比较器,共同构成完整的数字可编程频率合成器和时钟发生器。以精密时钟源作为基准时,AD9850能产生频谱纯净的频率/相位可编程、模拟输出正弦波。该正弦波可以直接用作频率源,或转换为适合捷变时钟发生器应用的方波。AD9850的创新型高速DDS内核提供一个32位频率调谐字;对于125 MHz基准时钟输入,输出调谐分辨率可以达到0.0291 Hz。AD9850的电路架构允许产生最高达到基准时钟频率一半(或62.5 MHz)的输出频率,而且输出频率能以最高每秒2300万新频率的速率发生数字式改变(异步)。该器件还提供五位数字控制相位调制,使其输出能够以180°、90°、45°、22.5°、11.25°及其任意组合的增量发生相移。AD9850还内置一个高速比较器,它经过配置可以接受DAC的(外部)滤波输出,以产生低抖动方波输出,这样该器件便可用作捷变时钟发生器。

频率调谐、控制和相位调制字均以并行字节或串行加载格式载入AD9850。并行加载格式由一个8位控制字(字节)的五次迭代加载组成,第一个字节控制相位调制、省电使能和加载格式,第二至第五个字节组成32位频率调谐字。串行加载通过单个引脚上的40位串行数据流完成。AD9850完整DDS利用先进的CMOS技术提供这一突破性功能与性能,而功耗仅155 mW(+3.3 V电源)。

AD9850采用节省空间的28引脚SSOP表面贴装封装,工作温度范围为–40°C至+85°C扩展工业温度范围。

数据表:*附件:AD9850 CMOS、125 MHz完整DDS频率合成器技术手册.pdf

特性

- 125 MHz时钟速率

- 片内高性能DAC和高速比较器

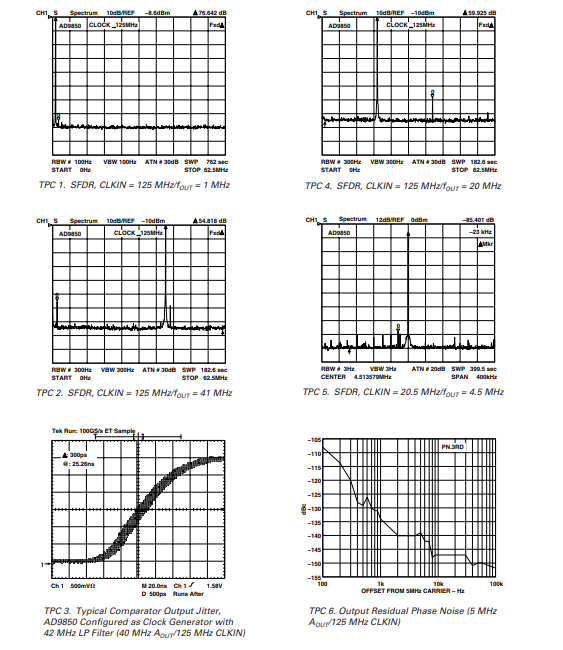

- DAC SFDR > 50 dB (40 MHz AOUT)

- 32位频率调谐字

- 简化的控制接口:并行字节或串行加载格式

- 相位调制能力

- 3.3 V或5 V单电源供电

- 低功耗:380 mW(125 MHz,5 V)

155 mW(100 MHz,3.3 V) - 省电功能

- 超小型28引脚SSOP封装

框图

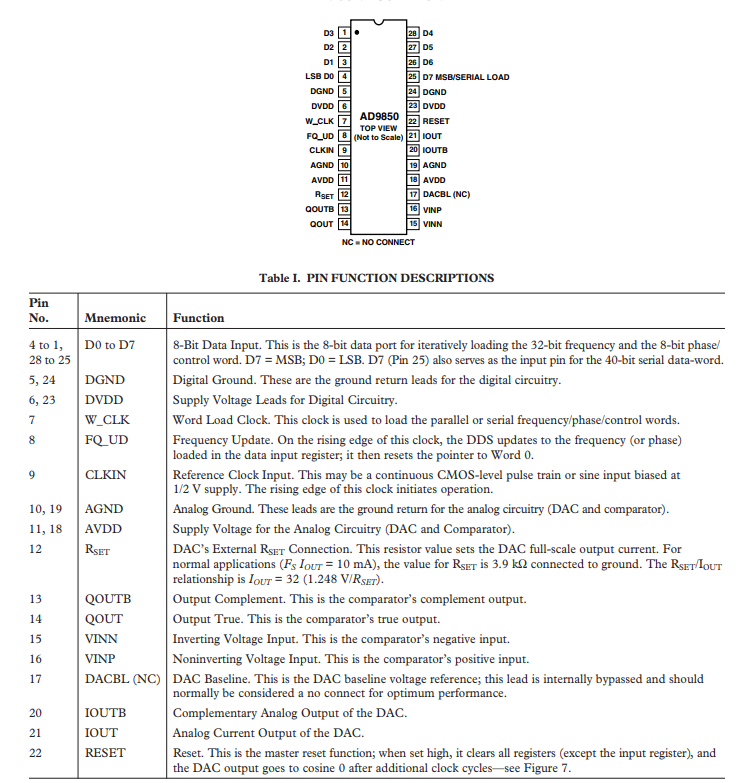

引脚配置描述

典型性能特征

工作原理与应用

AD9850采用直接数字合成(DDS)技术,以数字控制振荡器的形式,在10位高速数模转换器的帮助下生成频率/相位可调的正弦波。数模转换器将数字波形转换为模拟波形,片上高速比较器将模拟正弦波转换为低电压正射极耦合逻辑(LVTTL)/互补金属氧化物半导体(CMOS)兼容的方波输出。DDS技术具有创新的电路架构,可实现对输出频率的全数字控制,从而实现高分辨率的输出频率控制。AD9850允许输出频率分辨率达到0.0291Hz,基准时钟为125MHz时可实现相位连续变化。

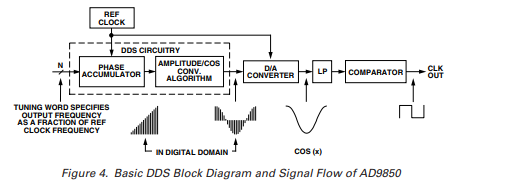

图4展示了配置为时钟发生器的AD9850的基本功能框图和信号流。

DDS电路本质上是一个数字分频器功能,其增量分辨率由参考时钟除以调谐字中的位数确定。相位累加器是一个可变模计数器,它接收时钟脉冲时存储相位增量数。当计数器溢出时,它会折返,使相位累加器的输出连续。

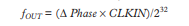

频率调谐字设置计数器的模数,这实际上决定了相位增量(Δ相位)的大小,即下一个时钟脉冲时相位累加器的增加值。加法增量越大,输出频率越高,从而实现更高的输出频率。AD9850使用一种创新的专有算法,将数学上精确的14位截断值转换为近似余弦值。这种独特的算法利用了简化的只读存储器(ROM)查找表和数字信号处理器(DSP)技术来执行此功能,有助于将AD9850的尺寸和功耗降至最低。AD9850的输出频率、参考时钟和调谐字之间的关系由以下公式确定:

其中:

- ΔPhase是32位调谐字的值。

- f_{CLKIN} 是输入参考时钟频率,单位为MHz。

- f_{OUT} 是输出频率,单位为MHz。

DDS模块的数字正弦波输出驱动内部10位高速数模转换器,该转换器将正弦波重构为模拟波形。这种DDS具有优化的动态性能和低杂散能量,体现为AD9850的低抖动性能。

-

深入解析AD9850:一款高性能DDS合成器2026-04-16 438

-

AD9850高集成度频率合成器中文资料2025-03-21 660

-

AN-587: 同步多个基于DDS的频率合成器AD9850/AD98512025-01-13 520

-

完整的直接数字频率合成器 AD9850 的分立、低相位噪声、125MHz 晶振解决方案2024-12-18 2164

-

AD9850:CMOS,125 MHz完整DDS合成器数据表2021-04-18 853

-

AN-419: 用于完整的直接数字频率合成器AD9850的分立、低相位噪声、125MH晶振2021-03-19 908

-

AD9850 CMOS、125 MHz完整DDS频率合成器2019-02-22 975

-

AD9850芯片原理及使用方法总结2018-04-13 57607

-

ad9850和ad9851模块介绍2017-11-06 11983

-

CMOS,125兆赫完整的DDS频率合成器AD9850数据表2017-10-19 1221

-

同步多个基于DDS的频率合成器AD98502011-11-29 935

-

用AD9850激励的锁相环频率合成器2009-12-08 2514

-

锁相环频率合成器-ad9850激励2008-07-17 803

-

AD9850 DDS 频率合成器的原理及应用2008-04-10 1548

全部0条评论

快来发表一下你的评论吧 !