半导体存储器测试图形技术解析

描述

文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了存储器测试中的晶圆拣选工作。

在半导体存储器测试中,测试图形(Test Pattern)是检测故障、验证可靠性的核心工具。根据测试序列长度与存储单元数N的关系,测试图形可分为N型、N²型和N³/₂型三大类。

以下从行业视角,对这三类测试图形进行技术解析与案例分享,分述如下:

N型测试图形

N²型测试图形

N³/₂型测试图形

N型测试图形

N型测试图形:基础故障的“筛查利器”

N型测试图形的测试序列长度与N成正比,聚焦于存储单元、输入/输出缓冲器等基础模块的故障检测。

一、 全“0”/全“1”图形

测试原理:按地址顺序向所有存储单元写入全“0”或全“1”,再按相同顺序读出并比较。

行业价值:

优势:可检测输入缓冲器、输出驱动器及存储单元的固定故障(Stuck-at Fault)。

局限:几乎无法检测地址解码器故障(如地址线短路)。

案例:某DRAM芯片通过全“0”测试后,发现输出驱动器存在固定“0”故障,导致数据总线冲突。

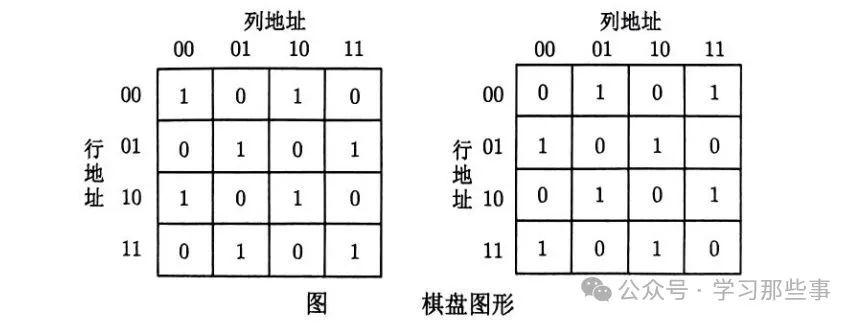

二、棋盘图形(Checkerboard)

测试原理:向相邻存储单元交替写入“0”和“1”,形成棋盘状分布。

行业价值:

优势:可检测相邻单元间的干扰故障(如电荷共享)。

局限:对地址故障检测能力有限。

案例:某SRAM芯片在棋盘测试中,发现相邻单元在写入相反数据时出现位翻转,定位为字线耦合电容过大。

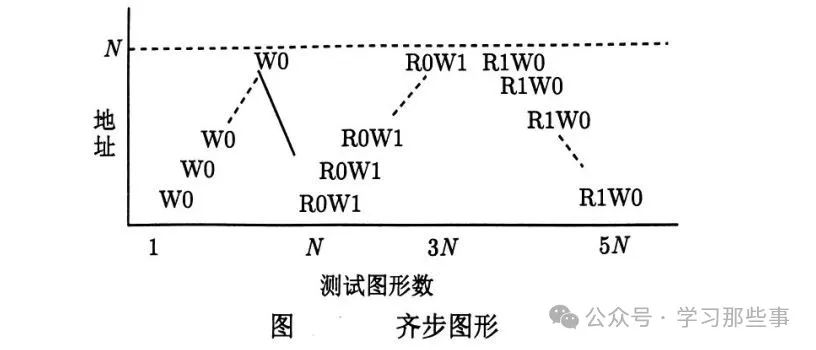

三、 齐步图形(Marching Pattern)

测试原理:在全“0”或全“1”背景上,按地址顺序逐个读写并改写存储单元,再反向重复。

行业价值:

优势:可检测地址故障(如地址线开路)和数据保持故障。

标准:JEDEC标准中March C+算法即基于此原理,覆盖95%以上的存储器故障。

案例:某NAND Flash通过齐步测试发现地址解码器存在偏移故障,导致连续地址映射错误。

N²型测试图形

N²型测试图形:地址与数据故障的“双重猎手”

N²型测试图形的测试序列长度与N²成正比,通过全面覆盖地址与数据组合,检测复杂故障。

一、走步图形(Walking Pattern)

测试原理:以某一存储单元为基准,逐次写入反码并检测其他单元是否受干扰。

行业价值:

优势:可检测存储单元间干扰(如行/列相邻干扰)。

案例:某DRAM芯片在走步测试中,发现某字线上的单元在写入反码时,相邻字线单元出现位翻转,定位为字线间距过小。

二、 跳步图形(Galloping Pattern)

测试原理:在走步图形基础上,每次检测后增加对基准单元的复核。

行业价值:

优势:覆盖所有地址与数据变化组合,检测隐蔽故障。

局限:测试时间较长,适用于高可靠性要求场景(如汽车电子)。

案例:某MRAM芯片通过跳步测试发现读出放大器存在阈值漂移,导致数据误判。

三、 跳步写恢复图形(Galloping Write Recovery)

测试原理:在写操作后,持续检测基准单元内容是否受干扰。

行业价值:

优势:专用于检测写操作引发的干扰故障(如写恢复时间不足)。

案例:某ReRAM芯片在跳步写恢复测试中,发现写操作后相邻单元出现数据翻转,定位为写驱动电路设计缺陷。

N³/₂型测试图形

N³/₂型测试图形:大容量存储器的“效率革命”

随着存储器容量向Tb级演进,N²型测试图形的时间成本激增。N³/₂型测试图形通过优化测试策略,将序列长度压缩至N³/₂,成为大容量存储器的首选。

一、 正交走步图形(Orthogonal Walking)

测试原理:基准单元在地址空间移动时,仅检测其所在行/列的干扰。

行业价值:

优势:测试时间缩短至N³/₂,同时保持对行/列干扰的检测能力。

案例:某3D NAND芯片通过正交走步测试,发现层间干扰导致的数据保持失效。

二、 对角线走步图形(Diagonal Walking)

测试原理:基准单元沿存储矩阵主对角线移动,其他单元全面检测。

行业价值:

优势:进一步压缩测试时间,适用于大规模阵列。

局限:对非对角线方向的干扰检测能力较弱。

案例:某CMOS图像传感器通过该测试,发现像素阵列对角线方向的耦合噪声。

三、移动对角线图形(Moving Diagonal)

测试原理:每次移动对角线后,重新写入并检测所有单元。

行业价值:

优势:平衡测试时间与覆盖率,适用于中等规模存储器。

案例:某LPDDR5芯片通过该测试,发现多bank并行访问时的时序冲突。

行业趋势:从“全面覆盖”到“智能筛选”

四、现代存储器测试正面临两大挑战

容量爆炸:Tb级存储器使N²型测试时间长达数小时,需通过压缩算法(如CompactTest)将时间压缩至分钟级。

低功耗需求:移动设备对测试功耗提出严苛要求,需采用动态电压调整(DVS)技术降低测试能耗。

从N型到N³/₂型测试图形,半导体行业在测试效率与故障覆盖率之间不断寻求平衡。随着3D集成、存算一体等新技术涌现,测试图形设计正从“经验驱动”向“AI驱动”演进,通过机器学习预测故障模式,实现测试资源的精准配置。未来,测试图形将成为连接芯片设计与制造工艺的“智能纽带”,持续推动存储器技术的可靠性边界。

-

半导体存储器的基本结构和分类2024-08-20 4560

-

半导体存储器的基本结构和特点2024-08-10 3761

-

半导体存储器有哪些 半导体存储器分为哪两种2024-02-01 5728

-

半导体存储器的介绍与分类2023-07-12 2694

-

存储器集成电路测试,记忆体积体电路测试,Memory IC Test2023-05-31 2089

-

存储系统及半导体存储器2022-07-08 787

-

半导体存储器及其测试.pdf2021-07-30 2030

-

半导体存储器及其测试2021-03-19 2099

-

什么是半导体存储器2019-04-21 3199

-

数字电子技术--半导体存储器2016-12-12 1178

-

半导体存储器,半导体存储器原理图解2010-03-01 27264

-

半导体存储器课件(PPT电子教案)2009-07-15 803

-

半导体存储器测试技术2008-08-17 2432

全部0条评论

快来发表一下你的评论吧 !