527-基于3U VPX XCZU15EG+TMS320C6678的信号处理板

电子说

描述

概述

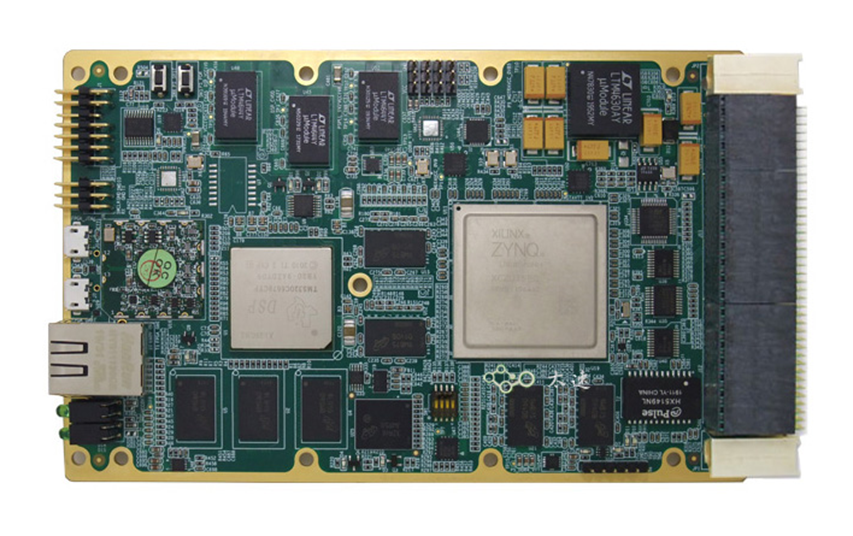

本板卡系我司自主研发的基于3U VPX风冷、导冷架构的信号处理板,适用于高速图像处理,雷达信号处理等。芯片采用工业级设计。

板卡采用标准3U VPX架构,板上集成一片Xilinx公司ZynqUltraScale+系列FPGA XCZU15EG,一片TI公司的多核浮点处理器TMS320C6678,一片STM32 MCU用于板卡状态监控、电源控制及健康管理功能,板卡集成多片DDR、Flash、PHY、RS422等芯片。

板卡的电气与机械设计依据VPX标准(VITA 46.0),支持导冷,能够满足用户在特殊环境下的使用需求。

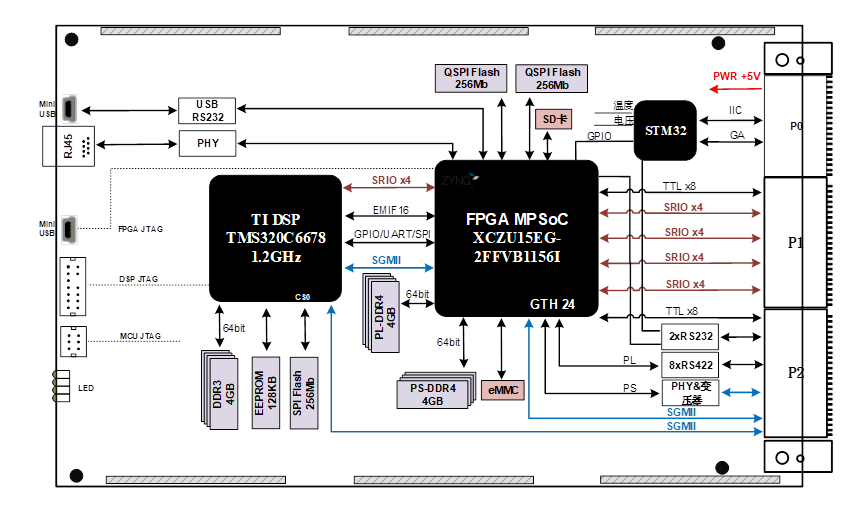

图 1:板卡结构框图

硬件参数

表 1:板卡硬件参数

| 处理器 |

FPGA: Xilinx XCZU15EG-2FFVB1156I DSP: TI TMS320C6678 主频1.25GHz |

| 协处理器 | MCU:STM32F103C8T6 |

| 内存 |

FPGA-PS: 类型DDR4,位宽64bit,容量4GB FPGA-PL: 类型DDR4,位宽64bit,容量4GB DSP: 类型DDR3,位宽64bit,容量4GB |

| 加载方式 |

FPGA:QSPI,SD卡,eMMC可选择 DSP:SPI加载模式,SPI Flash 32MB |

| LED | 四个,电源状态指示灯,FPGA状态指示,DSP状态指示,MCU状态指示 |

| 仿真器接口 |

FPGA: Micro USB接口 DSP: 2x 7Pin JTAG接口,间距2.54mm, MCU: 3pin JTAG接口,间距2.54mm, |

| 复位方式 | 外复位 |

| 前面板 |

4个状态指示灯 3个处理器仿真器接口 1路FPGA-PS串口 1路FPGA-PS 千兆以太网 |

| VPX接口 |

P0: IIC总线,外复位,外参考时钟 P1: GTX x16,TTL/LVTTLIO x8 P2: 8路RS422,2路RS232,1路1000BASE-T,2路SGMII,TTL/LVTTL IO x8 |

性能指标

板载一片Xilinx FPGA XC7V690T-2FFG1761I。

板载一片TI DSP TMS320C6678。

板载一片ST MCU STM32F103C8T6。

DSP连接一组DDR3,64bit位宽,容量4GB,数据速率1333MT/s。

FPGA PS连接一组DDR4,64bit位宽,容量4GB,数据速率2400MT/s。

FPGA PL连接一组DDR4,64bit位宽,容量4GB,数据速率2400MT/s。

DSP 采用SPI 加载方式,SPI Flash容量32MB。

FPGA 采用QSPI,SD卡,eMMC加载方式。

DSP和FPGA通过SRIO x4@5Gbps/Lane,SGMII高速总线互联。

DSP和FPGA通过EMIF16,GPIO,SPI,UART等低速总线互联。

VPX P1支持4组 SRIO x4@5Gbps/Lane。

VPX P1 支持8个TTL/LVTTL电平IO。

VPX P2 支持8路RS422接口至FPGA PL。

VPX P2 支持1路RS232接口至FPGA PL。

VPX P2 支持1路RS232接口至MCU。

VPX P2支持1路1000BASE-T至FPGA-PS。

VPX P2支持1路SGMII至FPGA。

VPX P2支持1路SGMII至DSP。

VPX P2支持8个TTL/LVTTL电平IO。

板卡芯片采用工业级。

板卡结构采用标准VPX 3U大小,支持风冷、导冷结构。

物理特性

尺寸:大小为100mm x 160mm

工作温度:商业级 0℃ ~ +55℃,工业级-40℃~+85℃

工作湿度:10%~80%

供电要求

单电源供电,整板功耗:50W

电压:DC +12V, 5A

纹波:≤10%

应用领域

高速信号处理

软件无线电

雷达信号处理

审核编辑 黄宇

- 相关推荐

- 热点推荐

- 信号处理板

-

【VPX315】青翼凌云科技基于 3U VPX 总线架构的 JFMQL100TAI + FT-M6678 智能信号处理平台2025-10-16 728

-

【VPX361】青翼凌云科技基于3U VPX总线架构的XCZU47DR射频收发子模块2025-09-15 2540

-

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX双FMC接口通用信号处理平台2025-09-01 1169

-

光纤图像处理卡设计原理图:520-基于ZU15EG 适配AWR2243的雷达验证底板 XCZU15EG架构高速信号处理板2025-08-28 801

-

高速图像处理卡设计原理图:527-基于3U VPX XCZU15EG+TMS320C6678的信号处理板2024-12-25 1391

-

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信号处理卡2024-11-08 1706

-

信号计算主板设计方案:735-基于3U VPX的AGX Xavier GPU计算主板2024-07-18 1448

-

KU115+ZU19EG+DSP6678的双FMC 6U VPX处理板2024-04-08 2587

-

VPX信号处理卡设计原理图:18-基于双TMS320C6678 DSP的3U VPX的信号处理平台2024-02-17 2704

-

基于6U VPX TMS320C6678+XC7K325T的信号处理板是什么?2021-06-25 2045

-

和大家分享一个基于6U VPX TMS320C6678+XC7K325T的信号处理板2018-12-19 3610

-

高性能6U VPX高速信号处理平台2016-04-14 3091

-

240-4C6678_K7_DDR3_VPX高速信号处理板2015-09-18 3242

-

18-基于双TMS320C6678 DSP的3U VPX的信号处理平台2015-05-15 2767

全部0条评论

快来发表一下你的评论吧 !