基于8051 IP调试器设计方案

描述

01概 述

8051 IP调试器是一种对基于8051指令系统的IP核进行调试的软硬件结合工具,需要与集成开发环境(IDE)结合使用。

调试器可加速开发者查找和修复程序错误,允许开发者单步执行代码、设置断点、查看变量和寄存器的值,以及修改内存内容,分析程序执行流程,提高MCU程序开发效率。

晶华微8051 IP核芯片,是基于S8051XC3 IP核进行设计的,因此本技术文章基于S8051XC3 IP核进行调试器原理讲解。

下图是晶华微基于8051指令系统的IP核,设计的SD8Link调试器实物图,后续将以SD8Link调试器展开讲解8051 IP调试器设计方案。

图1 SD8Link调试器实物图

02SD8Link调试器原理

首先调试器接收IDE编译生成的可执行文件(例如:HEX文件),通过JTAG和OneWire接口,将程序烧录到8051IP核的Flash空间内或是RAM空间。待IDE进入DEBUG模式后,可进行复位、全速、单步、停止、设置断点、查看变量和寄存器的值,进而调试程序,分析程序执行流程,查找和修改程序错误。

调试模块的功能由数据寄存器(DREG)、指令寄存器(IREG)、硬件断点寄存器(HWBP)等寄存器控制,这些寄存器可以通过JTAG或OneWire接口进行读写。

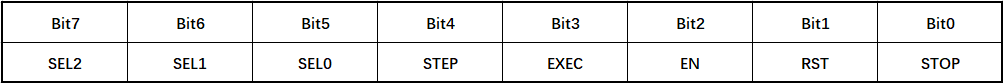

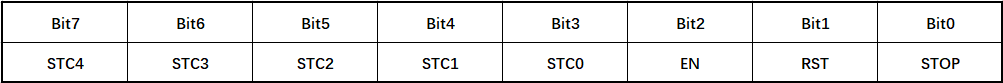

数据寄存器(DREG),由读写2个寄存器组成,对CPU状态进行读写控制

写

读

数据寄存器(DREG)数据位说明

表1 DREG数据位说明

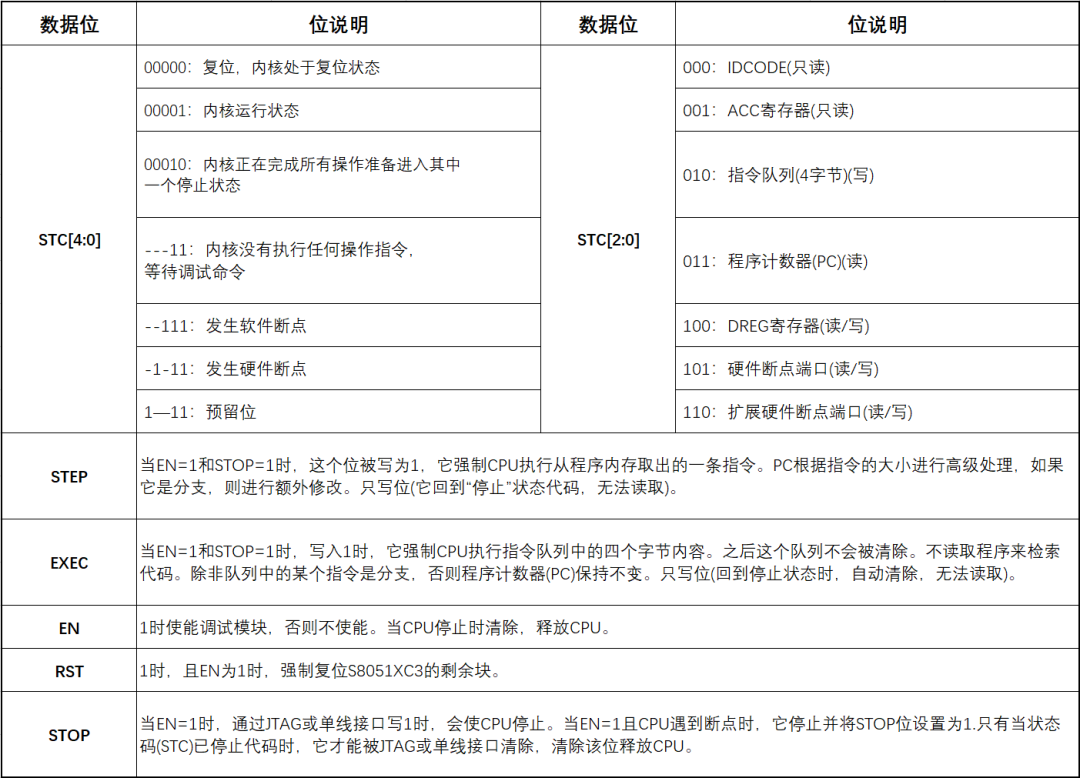

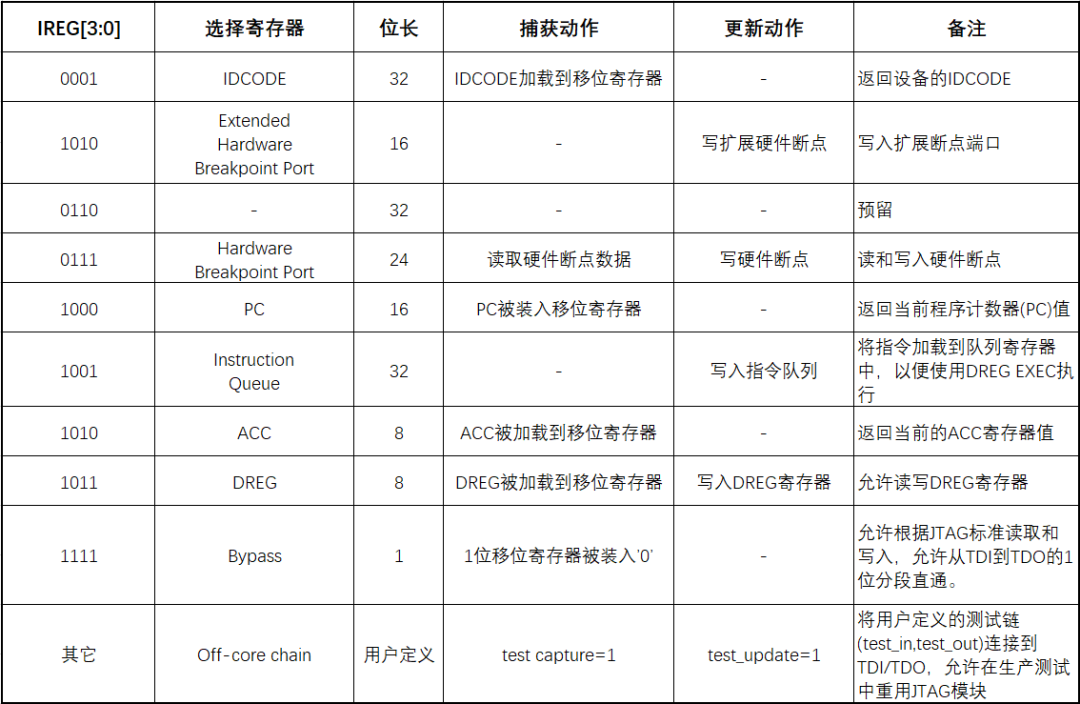

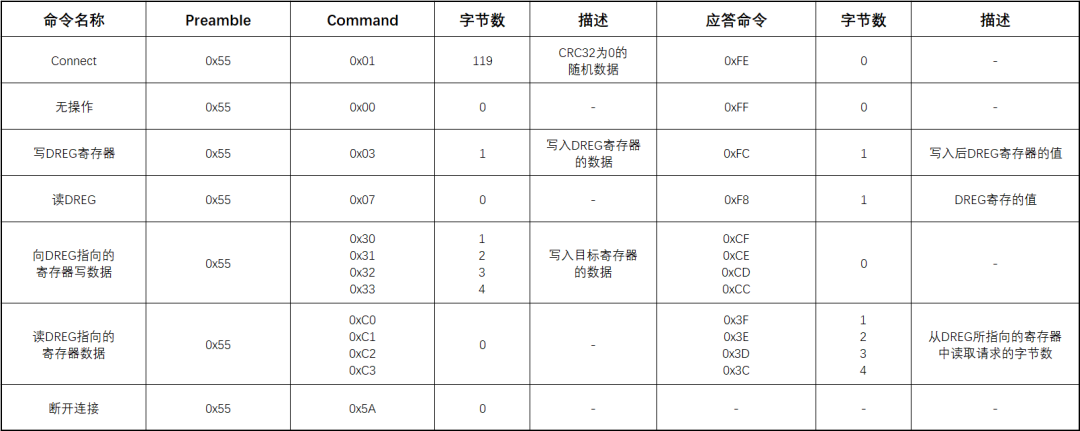

指令寄存器(IREG),JTAG和OneWire接口对应不同的指令

表2 JTAG指令寄存器

表3 OneWire接口命令

SD8Link采用JTAG与芯片通讯说明

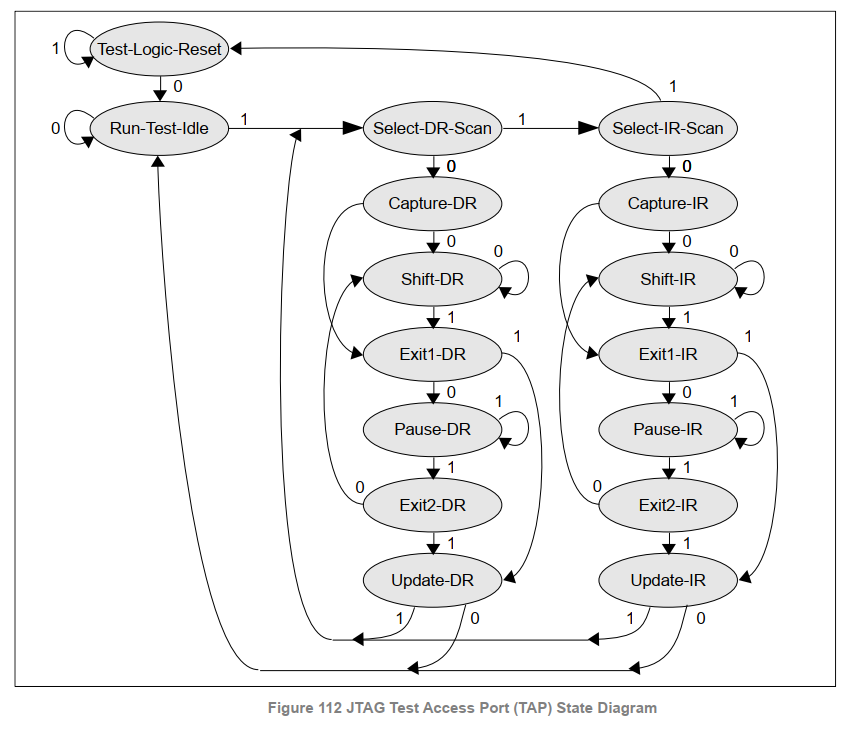

芯片JTAG采用TMS/TCK/TDI/TDO四线进行通讯,TAP状态机控制流程如下图所示,以“TMS”信号作为输入控制。

图2 JTAG状态机控制流程

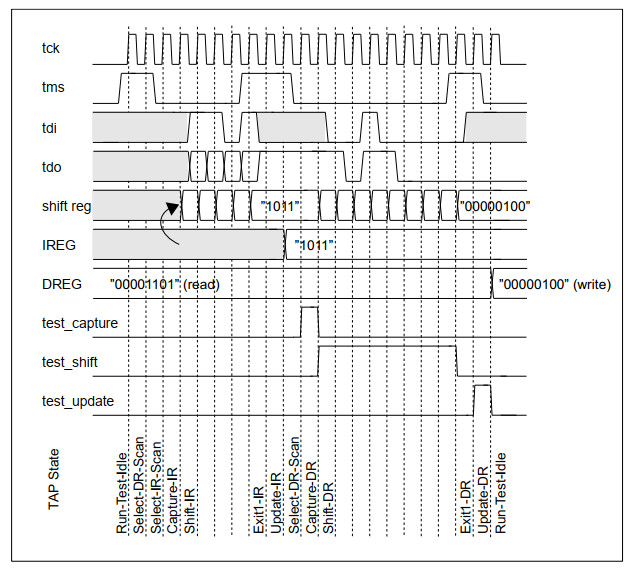

上图2右半部分流程用于选择“表1 JTAG指令寄存器”的寄存器,作为左半部分流程操作的寄存器,例如下图是写DREG寄存器时的完整时序图。

图3 JTAG写DREG寄存器时序图

SD8Link采用OneWire与芯片通讯说明

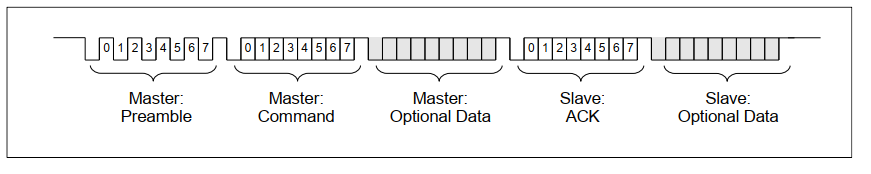

根据“表2 OneWire接口命令”,按照下图传输一帧数据的一般数据格式进行读写操作,对于主机数据或从机应答数据字节长度为0的操作,对应数据格式中不存在Data数据。

图4 OneWire数据格式

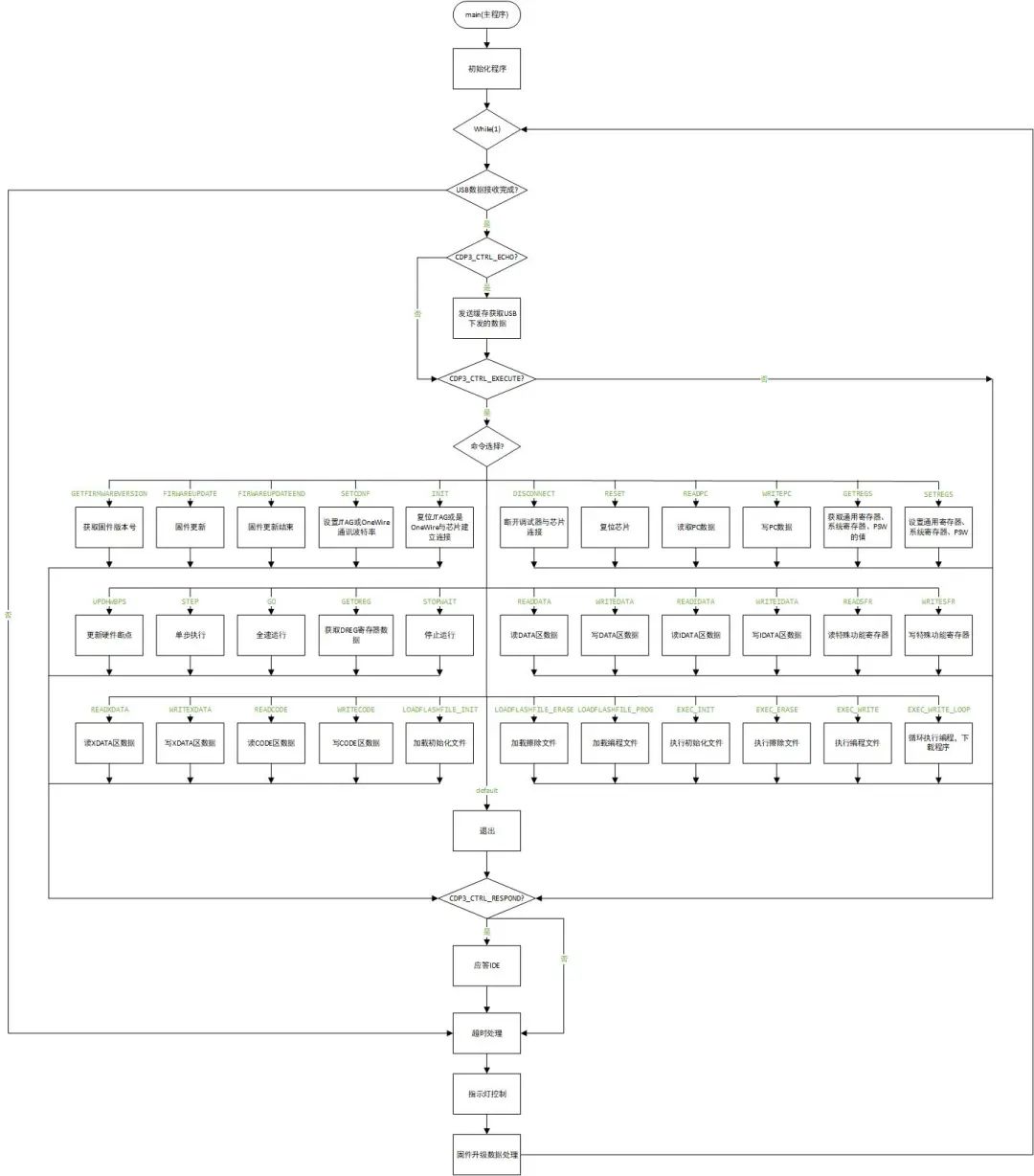

03SD8Link调试器程序流程图

图5 调试器程序流程图

04SD8Link调试器性能特点

支持多种芯片调试,例如SD81F233、SD82F354、SD82F466、SD82P253等等;

支持使用Keil实现固件在线升级功能,可扩展兼容更多8051 IP设计的IC;

支持JTAG和OneWire(单线异步)两种接口模式,方便客户设计选择使用;

支持设置断点、单步执行、变量查看、存储器读写等多种调试功能;

支持调试器提供3.3V电源输出,500mA带负载能力。

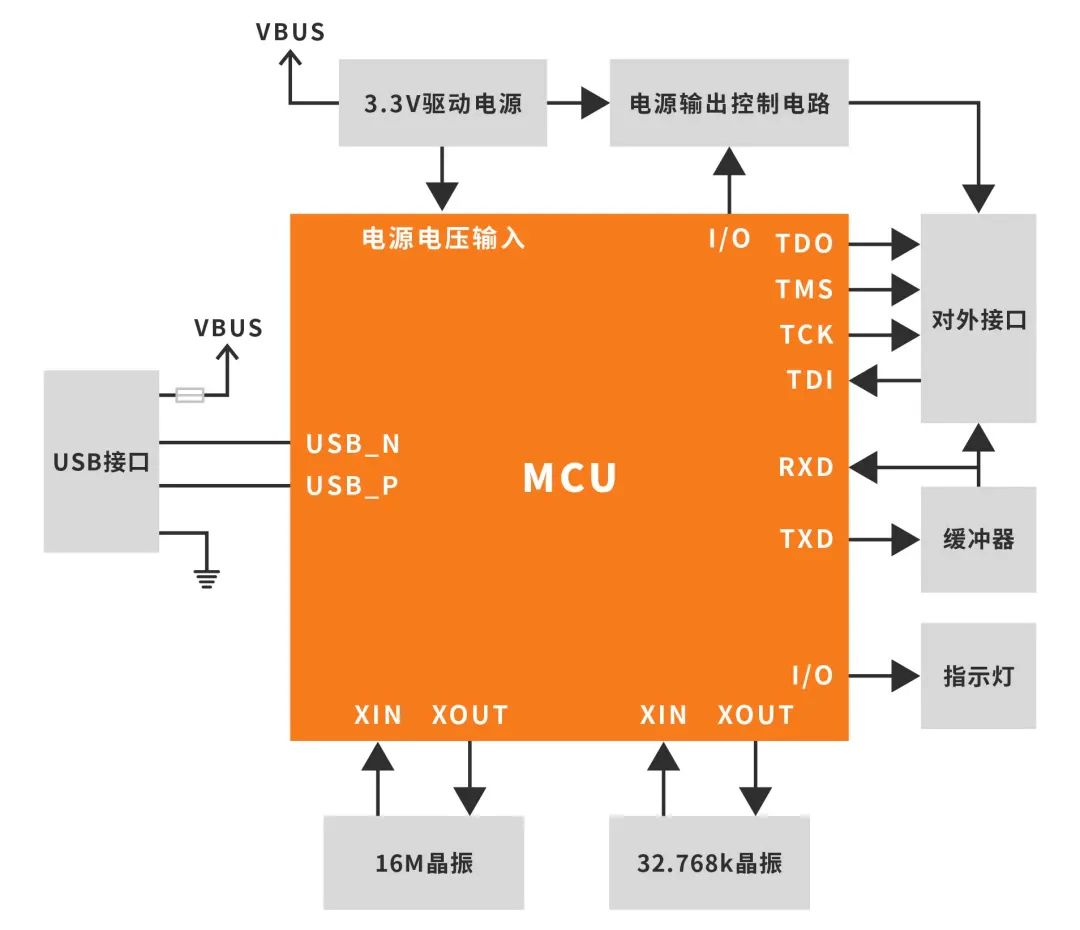

05SD8Link调试器电路框图

图6 调试器电路框图

-

怎么实现基于SoPC的通用在线调试器设计?2021-05-28 1794

-

基于DCC和JTAG的ARM硬件仿真调试器的研究与实现2010-10-27 998

-

基于CodeWarrior集成开发环境的调试器原理2011-12-27 1056

-

基于SOPC的M8051嵌入式调试器设计2012-10-15 9902

-

调试器模块(可按键调试)2016-01-13 737

-

使用在PICkit™ 3线调试器2017-09-22 923

-

gdb调试器解析2017-10-18 1185

-

基于SOPC的M8051调试器设计及系统测试2018-03-30 3310

-

Microchip 调试器(MDB) 用户指南2018-05-25 1233

-

Microchip调试器(MDB)用户指南2021-05-12 1203

-

逻辑调试器link-logic2022-01-12 788

-

串口/网络数据调试器2023-05-09 591

-

Microchip调试器(MDB)用户指南2023-09-22 603

-

应用单片机开发的ST LINK调试器设计制作2024-03-06 2651

-

MPLAB® PICkit™ Basic调试器技术解析与应用指南2025-09-29 1028

全部0条评论

快来发表一下你的评论吧 !