寄存器和cache的区别介绍

电子常识

描述

CACHE简介

cache高速缓冲存储器一种特殊的存储器子系统,其中复制了频繁使用的数据以利于快速访问。存储器的高速缓冲存储器存储了频繁访问的RAM位置的内容及这些数据项的存储地址。当处理器引用存储器中的某地址时,高速缓冲存储器便检查是否存有该地址。如果存有该地址,则将数据返回处理器;如果没有保存该地址,则进行常规的存储器访问。因为高速缓冲存储器总是比主RAM存储器速度快,所以当RAM的访问速度低于微处理器的速度时,常使用高速缓冲存储器。

CACHE替换机构

当CPU访问Cache未命中时,应从主存中读取信息,同时写入Cache。若Cache未满,则直接写入;若Cache已满,则需要进行替换。替换机构由硬件组成,并按替换算法进行设计,其作用是指出替换的页号。常用的替换算法有先进先出算法(FIFO)和近期最少使用算法(LRU)。

cache的读写操作

1、读操作

访存时,将主存地址同时送主存和Cache,一则启动对主存的读操作,二则在Cache中按映像方式从中获取Cache地址,并将主存标记与Cache标记比较:若相同,则访问命中,从Cache中读取数据。因为Cache速度比主存速度快,所以不等主存读操作结束,即可继续下一次访存操作;若不相同,则访问未命中,则从主存中读取数据,并考虑是否按某种替换算法更新Cache某页的内容。

2、写操作

将数据写入主存有两种方法,写回法和些直达法。

写回法:信息暂时只写入Cache,并用标志加以注明,直到该页内容需从Cache中替换出来时,才一次写入主存。优点是操作速度快,缺点是写回主存前,主存中没有这些内容,与Cache不一致,易造成错误。

寄存器简介

寄存器是中央处理器内的组成部分。寄存器是有限存贮容量的高速存贮部件,它们可用来暂存指令、数据和地址。在中央处理器的控制部件中,包含的寄存器有指令寄存器(IR)和程序计数器(PC)。在中央处理器的算术及逻辑部件中,存器有累加器(ACC)。

寄存器原理

存器的基本单元是D触发器,按照其用途分为基本寄存器和移位寄存器

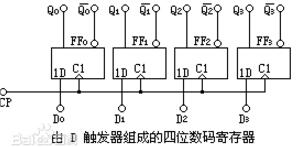

基本寄存器(见图)是由D触发器组成,在CP脉冲作用下,每个D触发器能够寄存一位二进制码。在D=0时,寄存器储存为0,在D=1时,寄存器储存为1。

在低电平为0、高电平为1时,需将信号源与D间连接一反相器,这样就可以完成对数据的储存。

需要强调的是,目前大型数字系统都是基于时钟运作的,其中寄存器一般是在时钟的边缘被触发的,基于电平触发的已较少使用。(通常说的CPU的频率就是指数字集成电路的时钟频率)

移位寄存器按照移位方向可以分为单向移位寄存器和双向移位寄存器

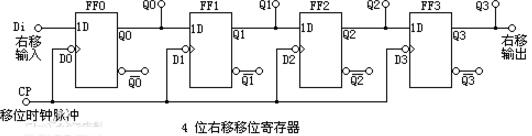

单向移位寄存器是由多个D触发器串接而成(见图),在串口Di输入需要储存的数据,触发器FF0就能够储存当前需要储存数据,在CP发出一次时钟控制脉冲时,串口Di同时输入第二个需要储存是的数据,而第一个数据则储存到触发器FF1中。

双向移位寄存器按图中方式排列,调换连接端顺序,可以控制寄存器向左移位,增加控制电路可以使寄存器右移,这样构成双向移位寄存器。

寄存器的主要技术

重命名技术

寄存器重命名,是CPU在解码过程中对寄存器进行重命名,解码器把“其它”的寄存器名字变为“通用”的寄存器名字,本质上是通过一个表格把x86寄存器重新映射到其它寄存器,这样可以让实际使用到的寄存器远大于8个。这样做的好处除了便于前面指令发生意外或分支预测出错时取消外,还避免了由于两条指令写同一个寄存器时的等待。

乱序执行技术

采用乱序执行技术使CPU内部电路满负荷运转并相应提高了CPU运行程序的速度。这好比请A、B、C三个名人为春节联欢晚会题写横幅“春节联欢晚会”六个大字,每人各写两个字,如果这时在一张大纸上按顺序由A写好“春节”后再交给B写“联欢”,然后再由C写“晚会”,那么这样在A写的时候,B和C必须等待,而在B写的时候C仍然要等待而A已经没事了。

但如果采用三个人分别用三张纸同时写的做法,那么B和C都不必等待就可以同时各写各的了,甚至C和B还可以比A先写好 也没关系(就像乱序执行),但当他们都写完后就必须重新在横幅上按“春节联欢晚会”的顺序排好(自然可以由别人做,就象CPU中乱序执行后的重新排列单元)才能挂出去。

寄存器和cache的区别

寄存器是内存阶层中的最顶端,也是系统获得操作资料的最快速途径。寄存器通常都是以他们可以保存的位元数量来估量,举例来说,一个“8位元寄存器”或“32位元寄存器”。寄存器现在都以寄存器档案的方式来实作,但是他们也可能使用单独的正反器、高速的核心内存、薄膜内存以及在数种机器上的其他方式来实作出来。

寄存器通常都用来意指由一个指令之输出或输入可以直接索引到的暂存器群组。更适当的是称他们为“架构寄存器”。

寄存器是中央处理器的一部分,是有限存贮容量的高速存贮部件,可用来暂存指令、数据和地址。是CPU必须的。

Cache缓存则是为了弥补CPU与内存之间运算速度的差异而设置的的部件,并不是每个CPU都有的。(明显例子是奔腾和部分赛扬间差异)

-

寄存器间接寻址和寄存器寻址的区别2024-10-05 5180

-

寄存器和高速缓存有什么区别2024-09-10 5006

-

寄存器寻址和直接寻址的区别2024-07-12 5916

-

存储器和寄存器的区别2024-05-12 5946

-

AArch64寄存器介绍2022-08-24 7760

-

寄存器与内存的区别2020-12-31 10951

-

寄存器由什么组成2018-08-21 38449

-

一文看懂暂存器和寄存器的区别2018-04-11 17417

-

闪存存储器是寄存器吗?_寄存器和存储器的区别2017-10-11 12561

-

寄存器与移位寄存器2016-05-20 1297

-

ARM寄存器详解2010-07-10 3306

全部0条评论

快来发表一下你的评论吧 !