ADUCM410具有MDIO接口的16位模拟输入/输出、Arm Cortex-M33的精密模拟微控制器技术手册

描述

概述

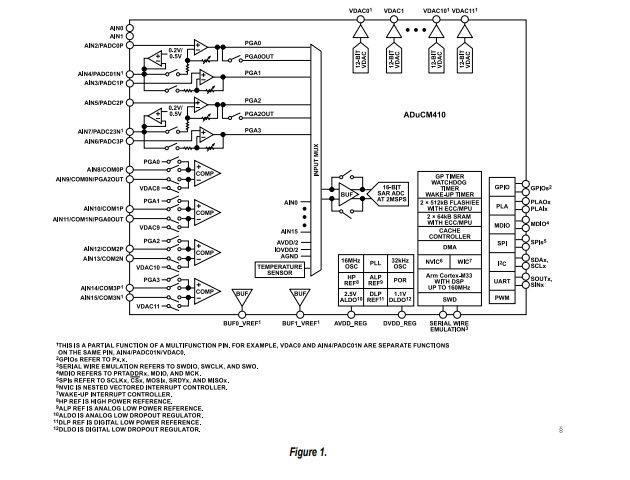

ADuCM410 是一款完全集成的单封装套件,包括高性能模拟外设套件和数字外设套件(由 160MHz Arm^®^ Cortex-M33 处理器控制)以及用于数字码和数据的集成闪存。

数据表:*附件:ADUCM410具有MDIO接口的16位模拟输入 输出、Arm Cortex-M33的精密模拟微控制器技术手册.pdf

ADuCM410 上的模数转换器 (ADC) 使用多达 16 个输入引脚提供 16 位、2 MSPS 数据采集,这些引脚可通过可编程增益放大器 (PGA) 或互阻抗放大器 (TIA) 进行编程,用于电压和电流测量,从而实现单端或差分操作。此外,还可以测量裸片温度和电源电压。

ADC 输入电压范围为 0 V 至 VREF。提供了一种时序控制器,使用户可以选择一组要按时序测量的 ADC 通道,而无需在时序期间进行软件干预。该时序可以选择性地以用户可选择的速率自动重复。

多达 12 个通道的 12 位电压数模转换器 (VDAC) 提供了支持输出的缓冲区。

ADuCM410 可进行配置,以便数字和模拟输出通过看门狗或软件复位时序保持其输出电压。因此,即使在 ADuCM410 自行复位时,产品也可以保持功能。

ADuCM410 具有低功耗 ARM Cortex-M33 处理器和 32 位精简指令集计算机 (RISC) 机器,通过浮点单元 (FPU) 提供高达 240 MIPS 的峰值性能。还集成了 2× 512 kB 闪存/EE 存储器和128 kB 静态随机存取存储器 (SRAM)—两者都具有单比特错误校正 (SEC) 和双比特错误检测 (DED)、错误检查和纠正 (ECC)。闪存包含两个独立的 512 kB 模块支持一个闪存模块执行程序,同时另一个闪存模块进行写入/擦除操作。

ADuCM410 采用片内振荡器工作,锁相环频率为 160 MHz。该时钟可以选择性地进行分频,以降低功耗。可以通过 ADuCM410 软件设置其他低功耗模式。

该套件包括一个管理数据输入/输出 (MDIO) 接口,能够以高达 10 MHz 的频率运行。 通过合并物理地址 (PHYADR) 和设备地址 (DEVAD) 硬件比较器,可以简化用户编程。不可擦除内核数字码与用户闪存中的标志相结合,使用户数字码在两个独立的硬件闪存块之间可靠地切换。

ADuCM410 集成了一系列片内外设,可以在应用中根据需要在软件控制下进行配置。这些外设包括 2× 个通用异步接收器变送器 (UART)、3× 个 I^2^C 和 3× 个串行外设接口 (SPI) 串行输入/输出通信控制器、通用输入/输出 (GPIOs)、32 单元可编程逻辑阵列 (PLAs)、5 个通用定时器、一个唤醒定时器 (WUT) 和一个系统看门狗定时器 (WDT)。还提供了具有八个 16 位脉宽调制输出通道 (PWM)。

GPIO 引脚 (Px.x) 在高阻抗输入模式下上电。在输出模式下,软件在开漏模式和推挽模式之间进行选择。上拉和下拉电阻可以通过软件禁用和启用。GPIO 引脚可以根据 IOVDDx 引脚配置不同的电压电平,如 3.3 V、1.8 V 和 1.2 V。在 GPIO 输出模式下,可以保持输入使能以监控 GPIO 引脚。GPIO 引脚也可编程设置为数字或模拟外设信号,在这种情况下,引脚特性需满足特 定要求。

Arm Cortex-M3 处理器具有大量的配套生态系统,通过 Arm 串行线调试端口访问,使 ADuCM410 的产品调试更轻松。片内工厂固件支持通 过 MDIO 或 I2C 进行在线串行下载。这些特性都集成在一个支持此精密模拟微控制器的低成本开发系统中。

请注意,在本数据手册全文中,多功能引脚(例如 VDAC7/P4.2)可能使用引脚全称或引脚的单一功能指代,例如 P4.2(如果仅与该功能相关时)。

应用

- 光纤网络 100 Gbps/200 Gbps/400 Gbps 和更高频率模块

- 工业控制

- 自动化

- 仪器仪表系统

特性

- 模拟输入/输出

- 多通道,16-位,2 MSPS ADC

- 高达 16 个外部通道

- 片内裸片温度监视器

- 4 个电源监视器通道

- 4 个支持电压和电流测量的 PGA/TIA 通道

- 差分和单端模式

- 0 V 至 VREF 模拟输入范围

- 12 位电压输出 DACs

- 8× 0 V 至 2.5 V, 1 kΩ 加载

- 4× 0 V 至 2.5 V, 2.5 kΩ 加载

- 片内低漂移 1.2 V 或 2.5 V 基准电压源

- 缓冲 1.25 V 或 2.5 V 输出

- 4 个电压比较器

- 多通道,16-位,2 MSPS ADC

- 微控制器

- 32 位 Arm Cortex-M33 内核,32 位 RISC 架构,FPU

- 串行线端口支持数字码下载和调试

- 存储器

- 2× 512 kB 独立闪存/EE 存储器

- 10,000 次循环闪存/EE 耐久性

- 10 年闪存/EE 保留 (Tj=125C)

- 20 年闪存/EE 保留 (Tj=85C)

- 具有 ECC 的 128 kB SRAM

- 软件触发,通过 MDIO 或 I^2^C 进行电路内可重编程

- 时钟选项:

- 16 MHz 片内振荡器

- 具有可编程分频器的 160 MHz PLL 输出

- 外部时钟脉冲源

- 片内外设

- 2× UART, 3× SPI, 3× I2^2^C 串行输入/输出

- 多电平电压(3.3 V,1.8 V,1.2 V)GPIOs

- 频率高达 10 MHz 的 MDIO 从机

- 5×通用定时器

- 唤醒定时器 (WUTs)

- 监控定时器 (WDTs)

- 32 元素 PLA

- 16 位 PWM

- 10 个外部中断

- 电源

- 多种电源:电压 DAC 和 ADC 为 3.3 V,数字输入/输出为 3.3 V、1.8 V 或 1.2 V

- 低功率应用的操作模式

- 封装和温度范围

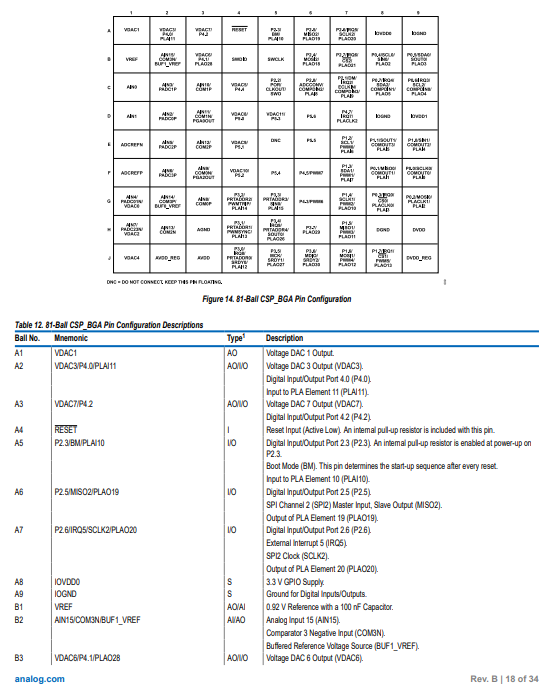

- 5 mm × 5 mm, 81球 CSP_BGA 和 3.46 mm × 3.46 mm 64 球 WLCSP

- BGA 封装使用 ULA 模塑化合物

- 完全指定在 −40°C 至 +105°C 环境中运行

- 工具

- 低成本快速启动开发系统

- 完全第三方支持

框图

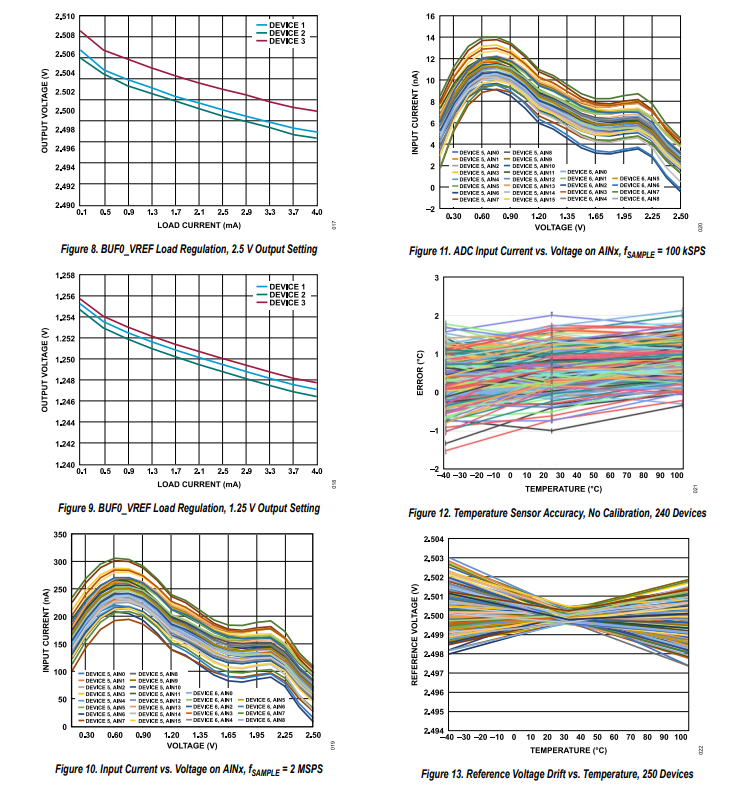

典型性能特征

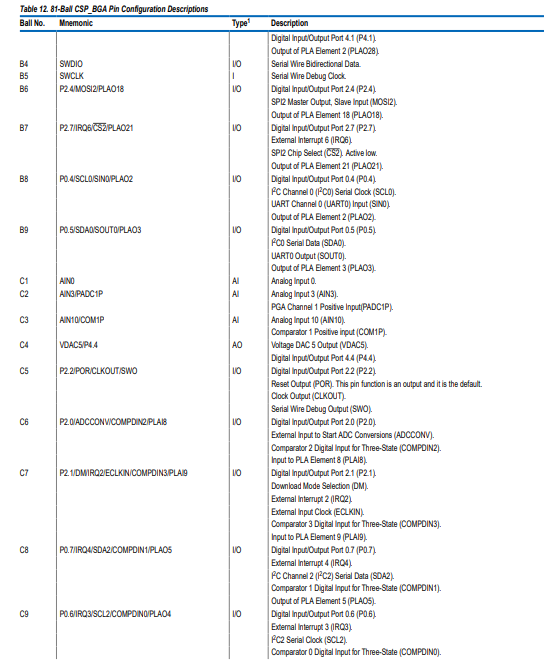

引脚配置描述

应用信息

电源供应

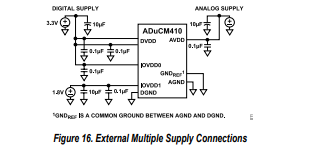

ADuCM410的工作电源电压范围为:AVDD和IOVDD0为2.85 V至3.6 V ;IOVDD1可以是1.2 V、1.8 V,或者与IOVDD0相同;DVDD范围是1.8 V至3.6 V。独立的模拟(AVDD)和数字电源引脚(IOVDD1和DVDD)可使AVDD在数字信号常出现噪声尖峰的系统中保持相对稳定。在此模式下,ADuCM410也可采用分离电源供电,即该器件的每个电源可使用不同电压电平(见表1 )。典型的分离电源配置如图16所示。

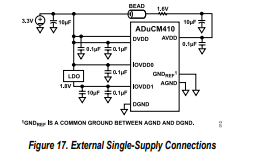

作为提供两个独立电源的替代方案,用户可在AVDD上放置小串联电阻和/或铁氧体磁珠来降低AVDD上的噪声,然后将模拟电源与AVDD和DVDD分别接地。此配置示例如图17所示。在这种配置中,其他模拟电路(如运算放大器和电压基准)也可从AVDD电源线路供电。

在图16和图17中,一个大容量(10 μF)储能电容连接到DVDD,一个单独的10 μF电容连接到AVDD。此外,在芯片上的每个AVDD、IOVDD0、IOVDD1和DVDD引脚附近放置本地小容量(0.1 μF)电容。应包括图中所示的所有电容,并确保较小的电容尽可能靠近每个电源引脚,且走线长度最短。将这些电容的接地端直接连接到底层接地层。

ADuCM410上的模拟和数字接地引脚必须始终参考同一系统接地参考点。

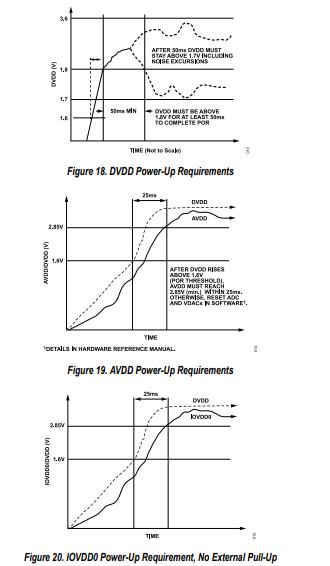

上电要求

图18和图19分别显示了DVDD和AVDD的上电要求。图20显示了如果P2.3/BMP/PLA10引脚没有外部上拉时,IOVDD0的上电要求。

使用电容对电源和稳压器进行充分去耦,这些电容连接在AVDD_REG、DVDD_REG和IOVDDx引脚及其相关的接地引脚(AGND和DGND)之间。表12和表13指出哪些接地引脚与哪些电源引脚配对。

- 相关推荐

- 热点推荐

- 微控制器

- ARM

- Cortex-M33

-

深度解析 ADuCM320i 精密模拟微控制器2026-03-31 225

-

ADuCM362/ADuCM363:低功耗精密模拟微控制器的卓越之选2026-03-24 151

-

Analog Devices Inc. ADUCM356精密模拟微控制器数据手册2025-06-12 1123

-

ADUCM420具有MDIO接口的12位模拟输入/输出、Arm Cortex-M33 的精密模拟微控制器技术手册2025-05-08 1342

-

ADuCM360/ADuCM361低功耗、精密模拟微控制器中文手册2025-04-09 726

-

ADUCM356 带有化学感应器接口数据表的精密模拟微控制器 ADUCM356 带有化学感应器接口数据表的精密模拟微控制器2023-10-07 93

-

ADuCM320i:精密模拟微控制器,带MDIO接口的14位模拟I/O,ARM Cortex-M3数据表2021-04-28 1180

-

ADuCM362-EP:低功耗、高精度模拟微控制器,带双Sigma-Delta ADC,ARM Cortex-M3数据表2021-03-22 1041

-

ADuCM320:精密模拟微控制器,14位模拟I/O, 带MDIO接口、ARM Cortex-M3处理器2021-03-21 1318

-

ADuCM360/ADuCM361:集成双通道∑-△型ADC和ARM Cortex-M3的低功耗精密模拟微控制器2021-03-19 1169

-

ADuC70xx 系列:精密模拟微控制器,12位模拟输入、输出,ARM7TDMI®MCU 数据手册2021-03-18 864

-

ADuCM410: Precision Analog Microcontroller, 16-Bit Analog Input/Output with MDIO Interface, Arm Cortex-M33 Data Sheet2021-01-29 1411

-

ADuCM420: Precision Analog Microcontroller, 12-Bit Analog Input/Output with MDIO Interface, Arm Cortex-M33 Data Sheet2021-01-27 1327

全部0条评论

快来发表一下你的评论吧 !