CMOS第一层互联的结构与作用

描述

文章来源:半导体与物理

原文作者:jjfly686

本文介绍了CMOS工艺中第一层互联的作用、材料及工艺步骤。

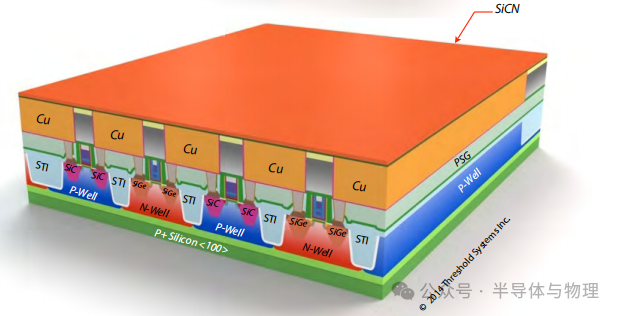

芯片中的晶体管(如NMOS和PMOS)需要通过金属线连接才能形成完整电路。 第一层互联 (通常称为M0或Local Interconnect)是直接连接晶体管源极、漏极和栅极的金属层,位于晶体管上方,距离硅衬底仅几十纳米。它的核心任务是 在器件层建立最短、最密集的连接通道 ,避免信号绕行到高层金属,从而提升芯片性能和集成密度。

第一层互联的结构与作用

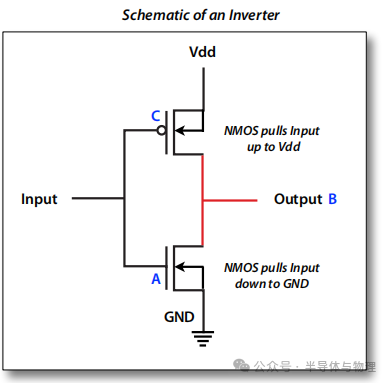

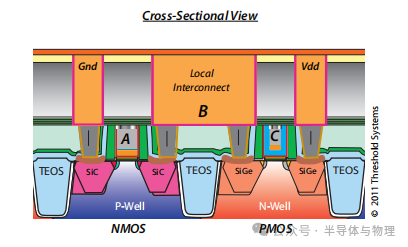

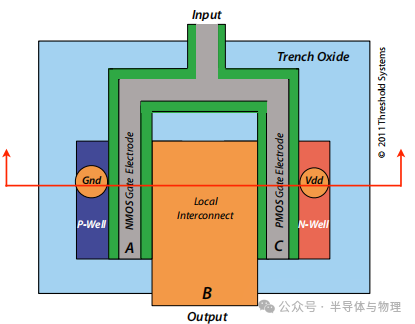

以最简单的CMOS反相器为例(如下图),NMOS和PMOS的漏极与源极需要通过金属线直接相连:

物理结构 :

NMOS漏极 (A)与 PMOS源极 (C)通过第一层铜线(B)直接连接,形成输出端;

栅极 (Input)通过多晶硅或金属线接收输入信号;

电源(Vdd) 和 地线(GND) 通过局部互连分别连接到PMOS和NMOS。

缩短路径 :信号直接在晶体管间传输,无需绕行至更高层金属(如M1-M10),延迟降低15%-20%;节省面积:在7 nm芯片中,第一层互联使逻辑单元面积缩小30%以上;简化设计:减少布线交叉点,降低电路复杂度。

材料与工艺

第一层互联的金属线宽度通常在10-30 nm(约为头发丝的万分之一),需采用特殊材料和工艺:铜(Cu):电阻率低(1.68 μΩ·cm),但需搭配氮化钽(TaN)阻挡层防止铜扩散;钴(Co):在5 nm以下节点逐步替代铜,填充深宽比>5:1的纳米沟槽时无空隙缺陷;阻挡层:2 nm厚的钽(Ta)或钛(Ti),增强金属与介质层的结合力。

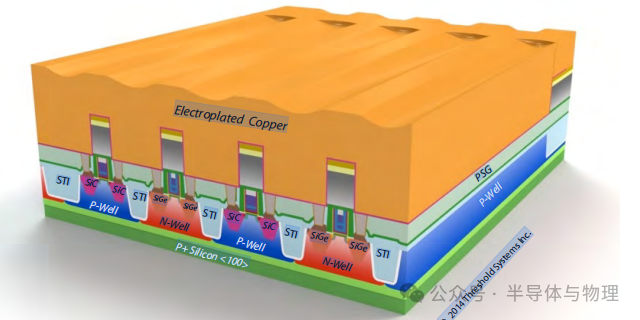

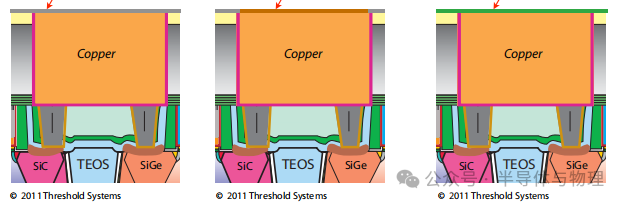

工艺步骤

刻蚀沟槽 :在氧化层中刻蚀出纳米级凹槽(深度50-100 nm,宽度10-20 nm);沉积阻挡层:用物理气相沉积(PVD)或原子层沉积(ALD)生成2 nm厚的TaN;铜种子层与电镀:PVD沉积铜种子层,电镀填充铜;化学机械抛光(CMP):磨平表面,确保金属线平坦化。

-

OSI七层模型的每一层功能2024-11-24 3469

-

神经网络三层结构的作用是什么2024-07-11 3134

-

卷积神经网络每一层的作用2024-07-02 4440

-

PADS设计4板,第一层基板挖一个大矩形槽,露出第二层基板,再在第二层基板挖一个小矩形槽。请问怎么实现?2023-03-24 24827

-

C语言单片机等待询问_单片机程序设计有十层功力,你现在在哪一层?2021-11-24 534

-

为什么画线时一直在第一层上?2019-08-13 1595

-

控件快捷菜单选择事件,能不能选择不是最低一层的菜单?2016-04-14 5374

-

单片机程序设计的十层功力,你练到那一层了?2015-11-01 6877

-

请教一下如何用protel画实验用的结构?2012-04-22 1609

全部0条评论

快来发表一下你的评论吧 !