肖特基势垒二极管选择及应用指南

电子说

描述

肖特基势垒二极管(SBD)的选择

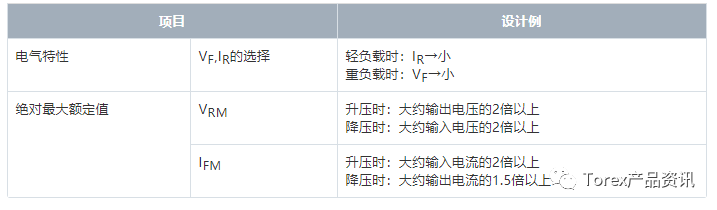

有关绝对最大额定值,根据与FET同样的理由,应选择相对于使用条件的1.5倍~2倍左右的产品。SBD的损失为正向热损失VF×IF和反向漏电流IR引起的热损失的合计值。因此,选择VF、IR都小的产品比较理想。但是,VF与IR成反比关系,一般要视负载电流而选用。VF在重负载时大,考虑到IR与负载无关为一定的值,所以轻负载时选择IR小的产品对提高效率的效果较好,重负载时选择VF小的产品效果较好。将上面的内容归纳于下面的表6中。

图表6 选择SBD的要点

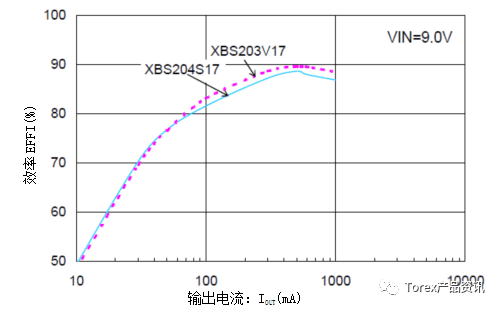

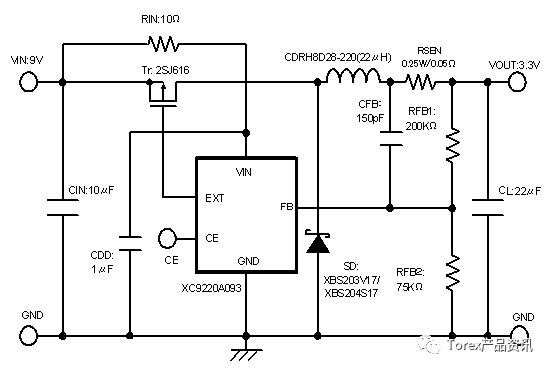

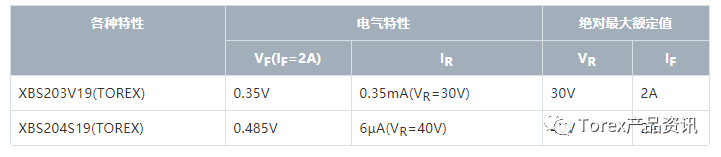

图17所示是图18所示的XC9220A093电路中只用表7所示的SBD变更时的效率变化。可看到与XBS203V17相比, XBS204S7的IR小,所以轻负载时的效率高,而因VF较大,所以重负载时效率低。

图

图17. XC9220A093SBD的选择与效率的不同

图18. 图17的测试电路

XC9220A093(降压时)

表7 测试了图17的SBD的各种特性

CL的选择

CL越大则纹波越小,但过分大的话,电容器的形状也大,成本提高。CL由所需的纹波大小而定。首先,大致以10mV~40mV的纹波大小为目标,升压时从表8的电容值开始,降压时从表9的电容值开始。但是,不支持低ESR电容器的DC/DC有异常振荡的危险,以连续模式使用时要想采用低ESR电容器的话,应预先检查负载瞬态响应,确认输出电压能否及时稳定(振荡大致在2次以内即收敛)。

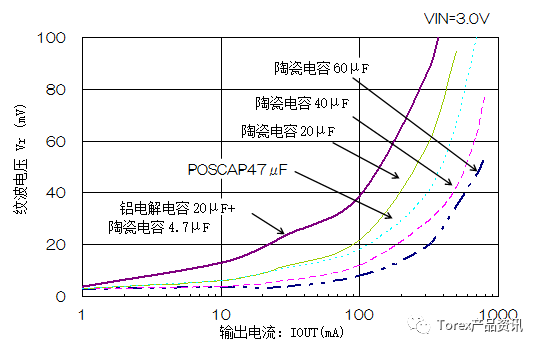

图19是图20所示的XC9104D093中只更换了CL后测试的输出纹波变化。纹波与ESR成正比,与电容值成反比地增大。铝电解电容时,没有并联的陶瓷电容的话,ESR过大难以获得输出电流。

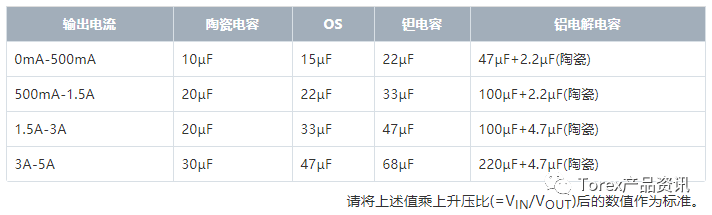

图表8 升压时CL的标准

表9 降压时CL的标准

图19.随CL值变化的输出侧纹波例(XC9104D093)

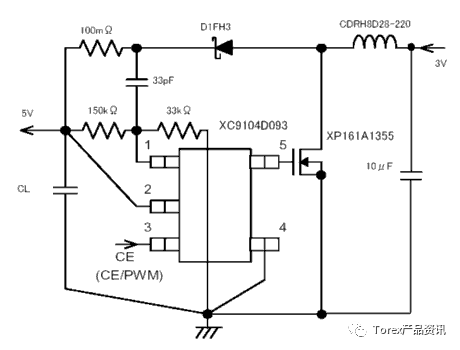

图20. XC9104D093 图19的测试电路

-

【科普小贴士】肖特基势垒二极管(SBD)的反向恢复特性2023-12-13 2077

-

肖特基势垒二极管的作用 肖特基势垒二极管的工作原理2023-09-02 4224

-

肖特基势垒二极管-1PS10SB822023-02-20 570

-

肖特基势垒二极管-BAT754_SER2023-02-17 383

-

肖特基势垒二极管-BAT54C-Q2023-02-16 461

-

肖特基势垒二极管-RB751V40-Q2023-02-15 484

-

SiC肖特基势垒二极管和Si肖特基势垒二极管的比较2023-02-08 1444

-

肖特基势垒二极管电路设计2021-01-19 4069

-

肖特基势垒二极管的特点2019-04-30 3219

-

浅析肖特基势垒二极管2019-04-11 1748

-

肖特基势垒二极管的特征2018-12-03 2064

-

什么是肖特基势垒二极管2010-03-05 2562

-

肖特基势垒二极管,肖特基势垒二极管原理/结构2010-02-26 3961

全部0条评论

快来发表一下你的评论吧 !