半导体芯片中的互连层次

描述

文章来源:半导体与物理

原文作者:jjfly686

本文介绍了芯片中金属互连线的各个层级的不同设计。

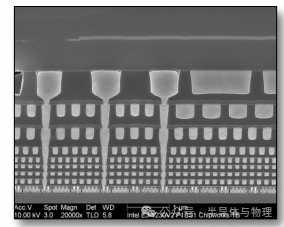

在半导体芯片中,数十亿晶体管需要通过金属互连线(Interconnect)连接成复杂电路。随着制程进入纳米级,互连线的层次化设计成为平衡性能、功耗与集成度的关键。芯片中的互连线按长度、功能及材料分为多个层级,从全局电源网络到晶体管间的纳米级连接,每一层都有独特的设计考量。

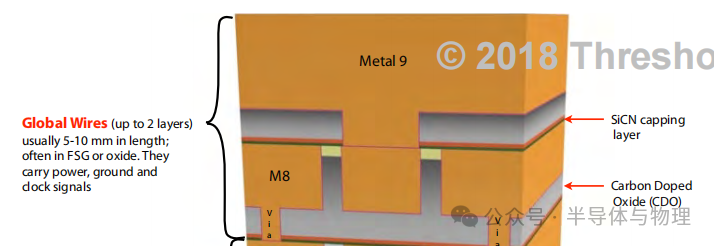

全局互连(Global Wires)

层级范围:通常为最高层金属(如M8、M9),最多2层。

长度:5-10mm,覆盖整个芯片区域。

功能:传输电源(Vdd)、地线(GND)及全局时钟信号。

材料:采用掺氟硅酸盐玻璃(FSG,k≈3.5)或传统氧化物(SiO₂,k≈3.9)作为绝缘介质,铜(Cu)为导体。

设计优势:高层金属厚度可达1-3μm,电流承载能力是低层金属的2-3倍,适合大电流传输。

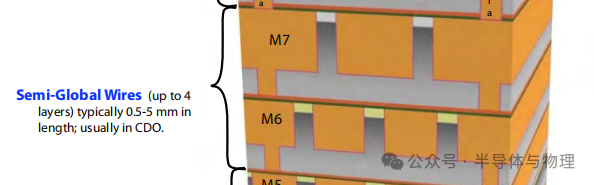

半全局互连(Semi-Global Wires)

层级范围:中间层金属(如M4-M7),最多4层。

长度:0.5-5mm,连接不同功能模块(如CPU核心与缓存)。

材料:绝缘介质为碳掺杂硅氧化物(CDO,k≈2.8-3.2),铜互连搭配氮化钽(TaN)阻挡层。

性能优化:CDO的碳掺杂降低介电常数,减少信号串扰,同时保持机械强度。

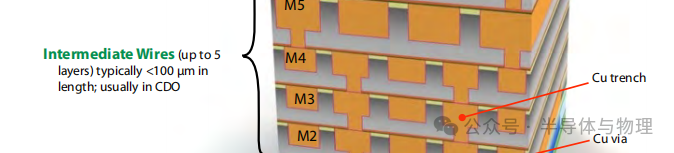

中间互连(Intermediate Wires)

层级范围:低层金属(如M2-M3),最多5层。

长度:<100μm,实现模块内局部连接。

材料:同样使用CDO介质,铜互连需更薄的阻挡层(1-2nm TaN)。

工艺挑战:深宽比>5:1的通孔需原子层沉积(ALD)铜籽晶层,避免电镀空洞。

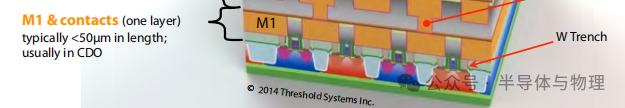

局部互连(M1 & Contacts)

层级范围:最底层金属(M1),直接连接晶体管源/漏极。

长度:<50μm,纳米级线宽(10-20nm)。

材料:CDO介质,钴(Co)或钌(Ru)逐步替代铜,减少电阻飙升问题。

关键技术:选择性外延填充接触孔,结合化学机械抛光(CMP)确保平坦化。

-

半导体封装革新之路:互连工艺的升级与变革2025-02-10 2133

-

半导体芯片的制作和封装资料2023-09-26 1204

-

高压连接线互连层次2023-07-22 1599

-

半导体工艺之金属互连工艺2023-07-03 5021

-

半导体元件与芯片的区别有哪些2021-11-01 6829

-

半导体的定义及其作用2021-09-15 2991

-

半导体芯片内部结构是由哪些部分组成的2021-07-29 8774

-

半导体芯片 半导体芯片公司排名2021-07-13 19592

-

半导体芯片产业的发展趋势2021-02-04 12794

-

半导体芯片内部结构详解2020-11-17 5351

-

半导体的芯片测试2020-10-20 15618

-

芯片,半导体,集成电路,傻傻分不清楚?2020-04-22 7990

-

芯片,集成电路,半导体含义2020-02-18 6476

-

半导体芯片的制造技术2011-10-26 18622

全部0条评论

快来发表一下你的评论吧 !