TPL7407L 40V、7 通道 NMOS 阵列低侧驱动器数据手册

描述

TPL7407L 是一种高电压、大电流 NMOS 晶体管阵列。该设备包括 7 个 NMOS 晶体管,具有高压输出和共阴极箝位二极管,用于 切换感性负载。单个 NMOS 通道的最大漏极电流额定值为 600 mA。新增功能 增加了调节和驱动电路,可在所有 GPIO 范围 (1.8 V – 5.0 V)。晶体管可以并联以获得更高的电流能力。

*附件:tpl7407l.pdf

TPL7407L 的主要优点是其更高的电源效率和更低的泄漏 双极达林顿实现。使用较低的 V老用户是 功耗不到电流小于 250 mA 的传统继电器驱动器的一半 每个通道。

特性

- 600mA 额定漏电流(每个通道)

- 7 通道

达林顿阵列的 CMOS 引脚对引脚改进(例如 ULN2003A) - 功率效率高(极低的 V

老)- V 电压降低不到 4 倍

老在 100 mA 时比达林顿阵列

- V 电压降低不到 4 倍

- 每通道 < 10 nA 的极低输出泄漏

- 扩展环境温度范围:T

一个= –40°C 至 125°C - 高压输出 40 V^^

- 与 1.8V 至 5.0V 微控制器

和逻辑接口兼容 - 内部续流二极管,用于感应反冲

保护 - 输入下拉电阻器允许对

输入驱动器进行三态 - 输入 RC 缓冲器可消除嘈杂环境中的

杂散作 - 电感式负载驱动器应用

- ESD 保护超过 JESD 22

- 2kV HBM、500V CDM

- 采用 16 引脚 SOIC 和 TSSOP 封装

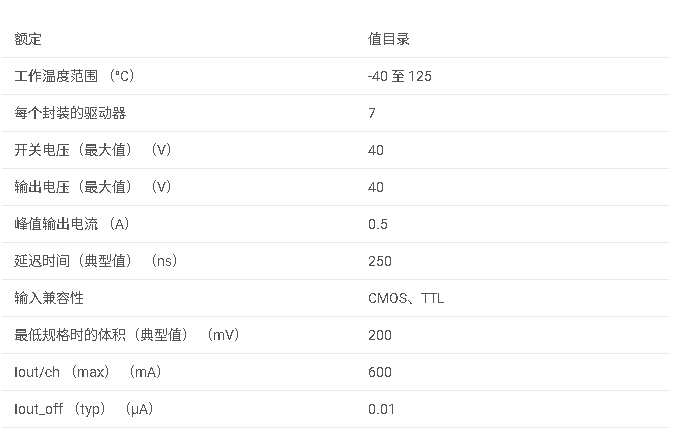

参数

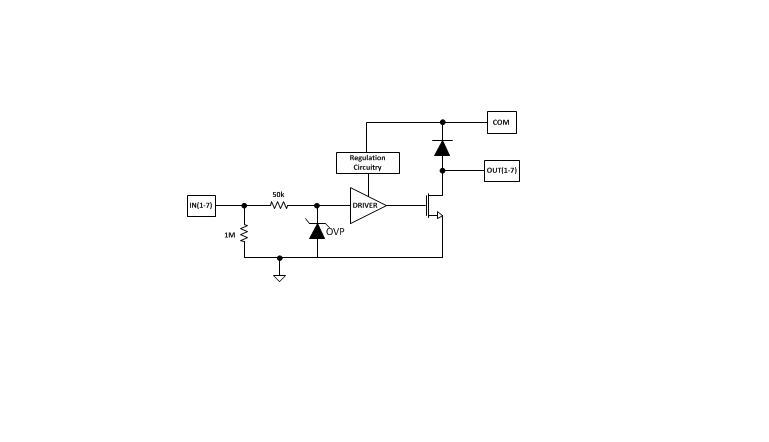

方框图

1. 产品概述

TPL7407L是一款高电压、高电流NMOS晶体管阵列,包含7个独立的NMOS晶体管通道,适用于驱动各种感性负载和电阻性负载。

2. 主要特性

- 高电压输出:最高可达40V

- 高电流能力:每个通道最大可驱动600mA

- 低输出泄漏:每个通道小于10nA

- 宽温度范围:工作温度从-40°C至125°C

- 低功耗:在100mA时,VOL低于4倍于传统达林顿阵列

- ESD保护:符合JESD 22-A114标准,HBM ±2kV,CDM ±500V

- 封装选项:提供16引脚SOIC和TSSOP封装

3. 应用领域

- 感性负载驱动(如继电器、步进电机、直流电机、电磁阀)

- LED驱动

- 逻辑电平转换

- 门极和IGBT驱动

4. 功能描述

- 内部自由轮二极管:提供感性负载反激保护

- 输入下拉电阻:允许输入驱动器三态化

- 输入RC吸收器:消除噪声环境中的虚假操作

- 内部LDO:为门极驱动电路供电

5. 电气特性

- 绝对最大额定值:输出引脚对地电压-0.3V至40V,输入引脚对地电压-0.3V至30V,连续漏电流每通道600mA

- 推荐操作条件:输出引脚电压0V至40V,COM引脚电压8.5V至40V,连续漏电流每通道500mA

- 电气参数:

- VOL(VDS):在VIN ≥ 1.5V,ID = 100mA时,典型值为0.32V

- IOUT(OFF):输出关断状态泄漏电流,在VOUT = 24V,VIN ≤ 1.0V时,典型值为10nA

- VF:钳位正向电压,在IF = 200mA时,典型值为1.4V

6. 封装与尺寸

- SOIC封装:9.90mm x 3.91mm

- TSSOP封装:5.00mm x 4.40mm

7. 布局指南

- 输入引脚:使用细线迹,尽可能分离输入通道以减少串扰

- 输出引脚:使用粗线迹以驱动高电流

- COM引脚:建议使用旁路电容以限制COM引脚电压的瞬态变化率

8. 热考虑

- 最大结温:150°C

- 热阻:SOIC封装为91.9°C/W,TSSOP封装为115.2°C/W

- 散热:通过PCB布局优化θJA值,或使用外部散热片和冷却机制

9. 设计资源

- 提供详细的应用信息和典型应用电路图

- TI E2E在线社区提供设计支持和快速解答问题的服务

通过以上总结,可以全面了解TPL7407L的主要特性、功能描述、电气特性、封装尺寸、布局指南、热考虑以及设计资源。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

TPS929120AQPWPRQ1 12 通道 40V 高侧 LED 驱动器2025-12-30 40

-

Texas Instruments TPS1213-Q1智能高侧驱动器数据手册2025-07-18 642

-

ULN2003V12 20V、7 通道 NMOS 阵列低侧驱动器数据手册2025-05-13 1478

-

TPL7407LA 30V、7 通道 NMOS 阵列低侧驱动器数据手册2025-05-10 821

-

TPL7407LA-Q1 30V、7 通道汽车级 NMOS 阵列低侧驱动器数据手册2025-05-09 737

-

TPL7407L通道继电器和感性负载吸收器驱动器EVM2024-12-21 456

-

TPL7407L提高了外围驱动的散热和能效2024-10-08 344

-

具有FlexWire™接口的24通道汽车类40V高侧 (O)LED 驱动器TPS929240-Q1数据表2024-04-01 482

-

具有FlexWire™ 接口的16通道汽车类40V高侧(O)LED 驱动器TPS929160-Q1数据表2024-03-29 623

-

具有FlexWire接口的TPS929120-Q1 12通道汽车40V高侧LED驱动器数据表2024-03-28 564

-

30V 7 通道低侧驱动器TPL7407LA-Q1数据表2024-03-19 372

-

TPL7407L 40V、7 通道、高功率灌电流驱动器2018-10-16 1463

-

标准驱动器怎么变得更好2018-09-14 2886

全部0条评论

快来发表一下你的评论吧 !