ADSP1802 SHARC处理器技术手册

描述

概述

ADSP1802 是一款数字信号处理器 (DSP),具有 Analog Devices, Inc. 超级哈佛架构单芯片计算机 (SHARC) 的 S PackageADSP1802 是一个 32 位/40 位浮点处理器 针对具有大型 片上 RAM,多个内部总线以消除 I/O 瓶颈, 并具有创新的数字应用程序接口 (DAI)。

应用

- 机舱内的音频和声学处理,包括主动声音设计、高级蜂鸣、免提和语音预处理、主动降噪和音频路径管理。

- 消费类应用中的音频处理,包括 UI 通信、专业视听、耳戴式设备和家庭影院。

- 具有安全性和监控功能的智能建筑。

数据表:*附件:ADSP1802 SHARC处理器技术手册.pdf

特性

- 高性能 32 位/40 位浮点处理器,用于高性能音频处理

- SIMD 计算架构

- 片上存储器

- 5 Mb L1 片上 RAM

- 8 Mb L2 内存

- 最大指令速率高达 400 MHz

- 支持 VISA

- 支持 FIR、IIR、FFT 加速器

- 8 项运动

- 4 个 PCG

- 1 个 S/PDIF 收发器

- 4 个 ASRC,具有 −140 dB SNR 性能

- 1 个 IDP/PDAP

- 1 个 DAI SRU

- DPI

- 2 个 SPI

- 1 串

- 12 标志

- 1 TWI

- 3 个 MOLD 模块(MOLD1、PWM2 和 PWM3)

- 2 个通用定时器

- 1 DPI SRU2

- 1 个热敏二极管

- 符合 AEC-Q100 标准,适用于汽车应用

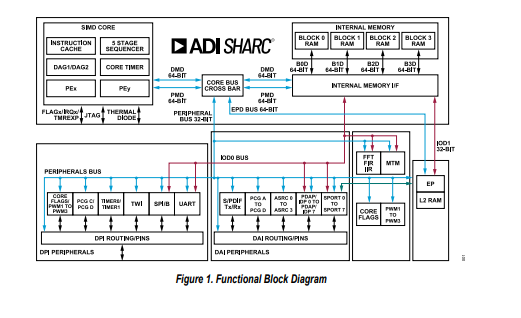

框图

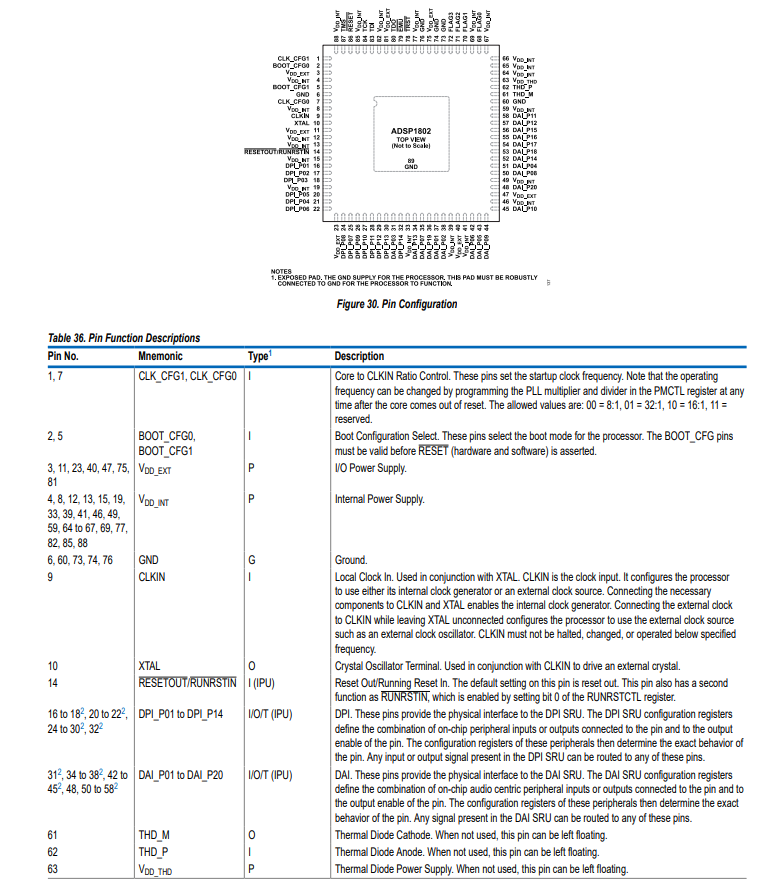

引脚配置描述

典型性能特性

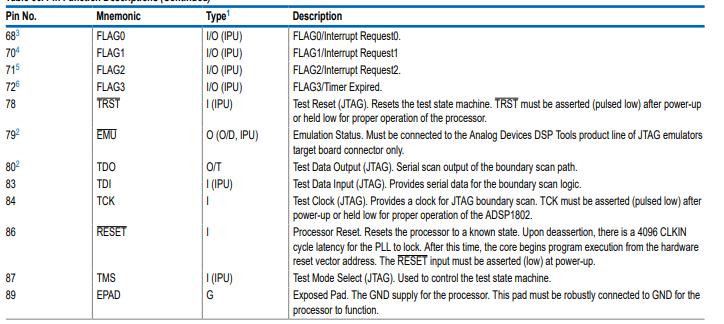

输出驱动电流

ADSP1802输出驱动器的典型电流 - 电压特性如图31所示。相关引脚包括FLAG0至FLAG3、EMU、TDO、RESETOUT、DP1至DP14以及DA1至DA20。这些曲线表示输出驱动器的电流驱动能力与输出电压的函数关系。

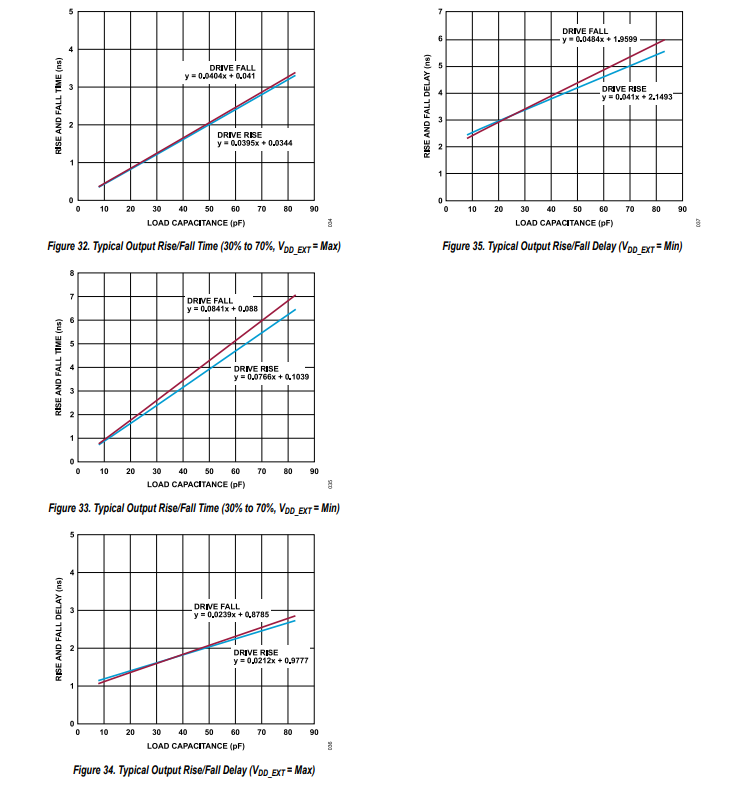

图 32 和图 33 展示了典型的上升沿和下降沿时间与负载电容的关系。图 34 和图 35 以图形方式呈现了输出延迟和保持时间如何随负载电容变化。

应用信息

系统设计

以下部分介绍系统设计选项和电源供应相关问题。

程序启动

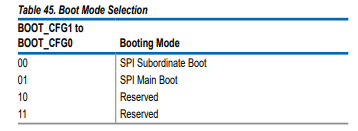

ADSP1802的内部存储器在系统上电时,可通过SPI主模式或SPI从模式启动。

运行复位功能允许用户在不重置锁相环(PLL)或执行启动操作的情况下,对处理器内核和外设进行复位。RESETOUT/RUNRSTIN引脚的功能还扩展到可作为启动运行复位的输入。

电源供应

ADSP1802为内部((V_{DD_INT}))和外部((V_{DD_EXT}))电源分别设有连接。内部电源必须满足(V_{DD_INT})规格要求,外部电源必须满足(V_{DD_EXT})规格要求。所有外部电源引脚必须连接到相同的电源供应。

为减少噪声耦合,印刷电路板(PCB)必须为(V_{DD_INT})和GND使用一对平行的电源层和接地层。

目标板JTAG仿真器连接器

亚德诺半导体(Analog Devices)SHARC DSP工具产品线中的JTAG仿真器,使用ADSP1802的IEEE 1149.1 JTAG测试访问端口,在仿真期间监测和控制目标板处理器。亚德诺半导体DSP工具产品线中的JTAG仿真器可在全处理器速度下进行仿真,支持检查和修改内存、寄存器以及处理器堆栈。ADSP1802的JTAG接口可确保仿真器不会影响目标系统的加载或定时。

有关亚德诺半导体SHARC DSP工具产品线中JTAG仿真器操作的完整信息,请参阅相应的仿真器硬件用户指南。

表面贴装设计

外露焊盘需在电气和热方面连接到GND。通过将外露焊盘焊接到PCB焊盘来实现这一点。此焊盘的尺寸应与PCB上的GND焊盘相匹配,且必须牢固连接到PCB中的GND平面,以实现最佳电气和热性能。封装中未单独设置GND引脚。

开发工具

亚德诺半导体为其处理器提供完整的软件和硬件开发工具产品线,包括集成开发环境、CrossCore® Embedded Studio、评估产品、仿真器以及各种软件插件。

-

ADSP1802 SHARC处理器:高性能音频处理的理想之选2026-03-23 314

-

Analog Devices Inc. ADSP1802 SHARC®处理器数据手册2025-05-29 1808

-

ADSP-21160M/ADSP-21160N:SHARC数字信号处理器数据手册2025-01-03 497

-

SHARC处理器的编程手册无法下载是为什么?2023-11-30 18767

-

ADSP-21261/ADSP-21262/ADSP-21266 SHARC嵌入式处理器2021-05-13 882

-

ADSP-21371/ADSP-21375 SHARC处理器数据表2021-04-30 975

-

ADSP-SC58x/ADSP-2158x SHARC+处理器硬件参考(1.0版)2021-04-26 897

-

SHARC处理器的评估系统2020-03-16 2243

-

ADI SHARC处理器有哪些应用案例2018-10-31 4795

-

SHARC处理器的编程手册无法下载2018-10-22 2660

全部0条评论

快来发表一下你的评论吧 !