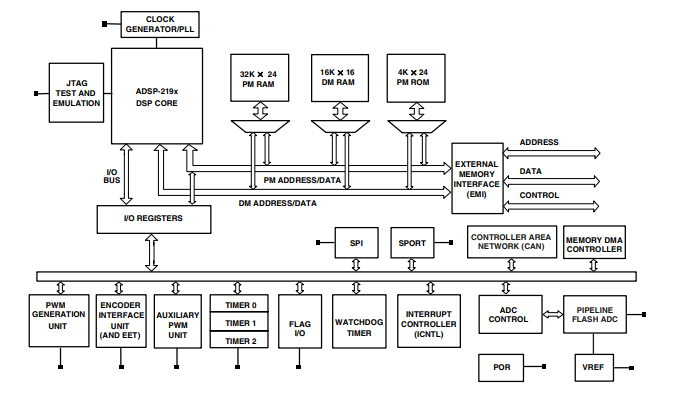

ADSP-21992高性能混合型信号DSP,160MHz,32K字程序存储器RAM,16K字数据存储器RAM技术手册

描述

概述

ADSP-21992进一步扩展了ADSP-2199x混合信号DSP产品系列的性能,可提供32K字程序存储器RAM和16K字数据存储器RAM。此外,ADSP-21992还可提供片上CAN通信端口,支持全CAN 2.0B,内置可配置邮箱和单个验收滤波器。集成CAN接口可实现将嵌入式控制和信号处理以及现场总线通信接口整合在一起的单芯片方案。

数据表:*附件:ADSP-21992高性能混合型信号DSP,160MHz,32K字程序存储器RAM,16K字数据存储器RAM技术手册.pdf

特性

- 160 MHz,ADSP-219x DSP内核

- 8通道、14位、20 MSPS ADC,内置片上电压基准

- 集成控制器区域网络(CAN)接口

- 外部存储器接口(达1 M字)

- 带双辅助PWM输出的三相PWM发生单元

- 32K字程序存储器RAM,16K字数据存储器RAM

- 三相PWM发生单元

- 增量编码器接口单元

- 3个32位通用定时器

- 16位通用标识I/O端口

- 同步串行(SPORT)和SPI通信端口

- CROSSCORE™工具支持

框图

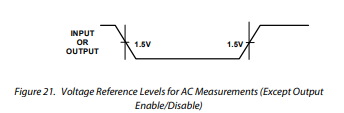

测试条件

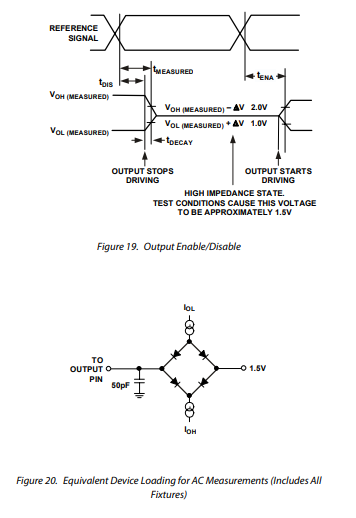

对数字信号处理器(DSP)的输出使能、禁用和保持时间进行测试。

输出禁用时间

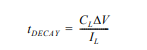

当输出引脚停止驱动并进入高阻抗状态时,视为输出引脚被禁用。从输出引脚停止驱动到总线上电压开始下降的时间,以及电压从测量输出下降(Delta V)所需的时间,取决于电容负载(C_{L})和负载电流(I_{L}) 。下降时间可通过以下公式近似计算:

输出禁用时间(t_{DISO})是(t_{MEASURED})和(t_{DECAY})之间的差值,如图19所示。时间(t_{MEASURED})是参考信号切换到输出电压从测量输出高电平或输出低电平下降(Delta V)时的时间间隔。(t_{DECAY})是在测试负载(C_{L})和(I_{L}) 下,(Delta V)等于0.5V时计算得出的。

输出使能时间

当输出引脚从高阻抗状态转变为开始驱动时,视为输出引脚被使能。输出使能时间(t_{ENA})是从参考信号达到高电平或低电平,到输出达到指定的高电平或低跳变点的时间间隔,如图19(输出使能/禁用图)所示。如果多个引脚(如数据总线)被使能,测量值为第一个开始驱动的引脚的值。

示例系统保持时间计算

要确定特定系统中的数据输出保持时间,首先使用第51页“输出禁用时间”中的公式计算(t_{DECAY}) 。选择(Delta V)为ADSP - 21992输出电压与设备所需保持时间的输入阈值之间的差值。典型的(Delta V)为0.4V。(C_{L})是总总线电容(每条数据线),(I_{L})是总泄漏或三态电流(每条数据线)。保持时间将是(t_{DECAY})加上最小禁用时间(即写周期的(t_{DATWRH}) )。

-

ADSP - 21992:高性能混合信号 DSP 控制器的深度剖析2026-03-23 692

-

ADSP-21990高性能混合型信号DSP,160MHz,4K字程序存储器RAM技术手册2025-05-12 1502

-

外部存储器是ROM还是RAM2024-08-06 5514

-

ram内部存储器电路组成2024-02-19 3799

-

ram是什么存储器断电后会丢失吗2024-01-12 5224

-

单片机外扩ram数据存储器2023-07-25 2337

-

MCS51 数据存储器(RAM)2021-11-23 1019

-

请用16K 8 的静态RAM存储芯片和32K 16的ROM芯片2021-07-28 2811

-

单片机中的数据存储器ram2020-05-13 4108

-

ADSP-21992 高性能混合型信号DSP,160 MHz,32K字程序存储器RAM,16K字数据存储器RAM2019-02-22 608

-

dsp与外扩展存储器的连接方法2017-12-04 3305

-

求助 数据存储器 FLASH程序存储器 FLASH数据存储器的区别2011-11-29 7227

-

几种DSP与外接存储器的连接方法2009-12-03 689

全部0条评论

快来发表一下你的评论吧 !