ADSP-BF531/ADSP-BF532/ADSP-BF533 400MHz低成本Blackfin处理器技术手册

描述

概述

ADI公司早期的ADSP-BF531、ADSP-BF532和ADSP-BF533产品系列具备Blackfin处理器的所有简单易用和架构上的特性。这三个处理器全部完全引脚兼容,仅在其性能和片上存储器方面有所不同,从而降低了风险,并提供根据终端应用要求进行灵活扩展的能力。所有这三个处理器都具备低功耗以及从低成本到极高性能的可扩展性能。

ADSP-BF531是Blackfin处理器系列的低成本切入点。它实现了性能、外设集成和价格之间的完美平衡,非常合适用于便携式测试设备、嵌入式调制解调器、生物特征识别和消费类音频等大多数对成本敏感的应用。

数据表:*附件:ADSP-BF531 ADSP-BF532 ADSP-BF533 400MHz低成本Blackfin处理器技术手册.pdf

高集成度

- 52KB片上L1存储器,可配置为

- 32KB L1指令存储器SRAM/高速缓存

- 16KB L1数据存储器SRAM/高速缓存

- 4 KB L1便笺式SRAM

- 并行外设接口,支持ITU-R 656视频数据格式

- 两个双通道全双工同步串行端口,支持八个立体声I^2^S通道

- 12个DMA通道,支持一维和二维数据传输

- 存储器控制器,提供与多组外部SDRAM、SRAM、闪存或ROM的无缝连接

- 3个定时器/计数器,支持PWM、脉宽和事件计数模式

- UART,支持IrDA®

- SPI兼容端口

- 事件处理器

- 实时时钟

- 看门狗定时器

- 具备1至63倍倍频能力的锁相环

- 160焊球(12mm x 12mm)小型BGA封装、176引脚(24mm x 24mm)LQFP封装和169焊球(19mm x 19mm)无铅Sparse PBGA封装

特性

- 400MHz/800MMAC的性能可实现多媒体应用中的多通道音频和CIF视频处理

- 具备片上内核电压调节功能的增强型动态电源管理可实现0.8V的工作电压,从而延长便携应用中的电池使用寿命

- 针对数据采集应用而优化的外设,提供与通用转换器的无缝连接

- 低成本且引脚和代码兼容的系列衍生产品,使得在成本敏感的消费类应用中的软件差异化成为可能

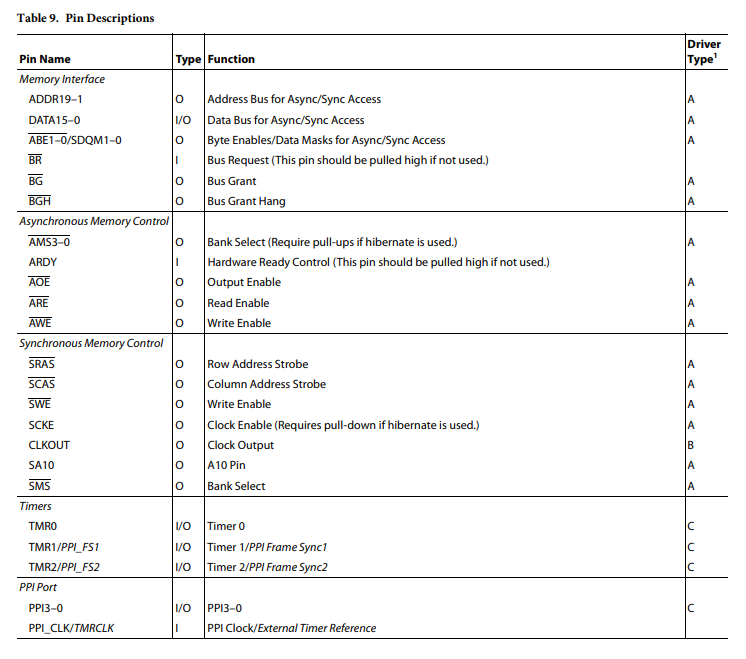

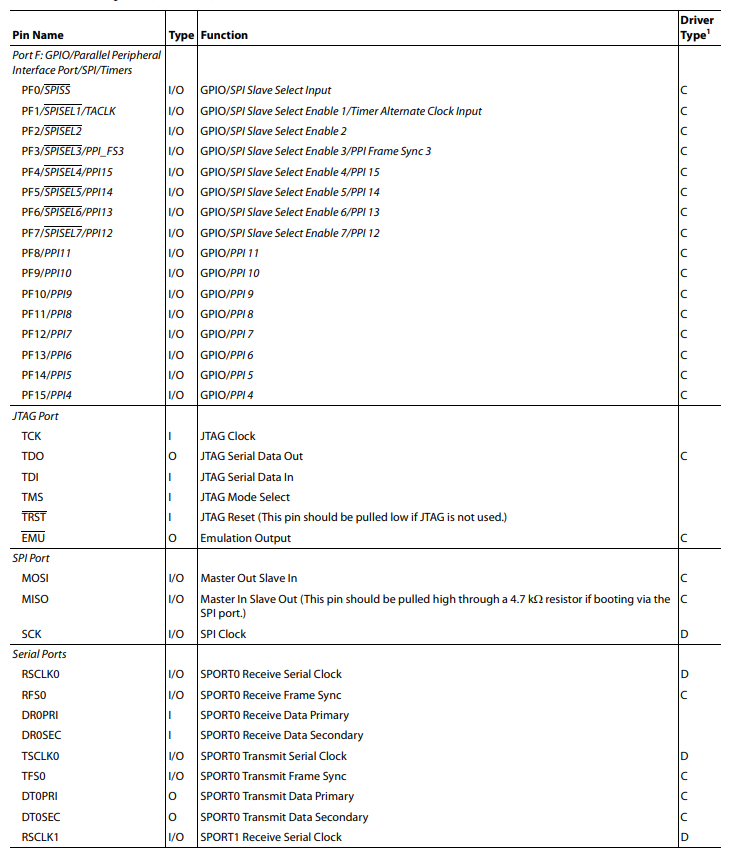

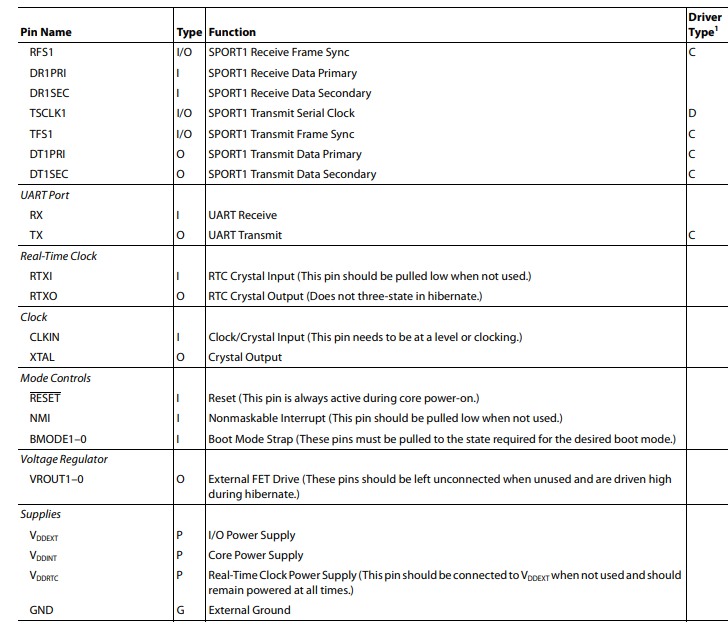

引脚说明

ADSP - BF531/ADSP - BF532/ADSP - BF533处理器的引脚定义见表9。

复位后,所有引脚均为三态,除了那些在系统时钟期间异步控制内存的引脚,以及同步控制内存的引脚。这些引脚由CLKOUT驱动,在系统时钟之外会进行翻转,除非另有说明。表9中注明的所有输出在复位期间均为三态。

如果(overline{BR})有效(无论(overline{RESET})是否置位 ),内存引脚也为三态。所有未使用的输入/输出(I/O)引脚的输入缓冲器已禁用,除了那些需要上拉或下拉的引脚,具体见表中说明。

为了保持最大功能和减少封装尺寸及引脚数量,一些引脚具有双重复用功能。在引脚功能可配置的情况下,默认状态以普通字体显示,备用功能以斜体显示。

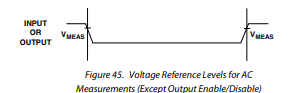

测试条件

本数据手册中出现的所有定时参数均在本节所述条件下测量。图45展示了交流测量(输出使能/禁用除外 )的测量点。测量点(V_{MEAS}),对于(V_{DDEXT})(标称值 ) = 3.3V时为0.95V,对于(V_{DDEXT})(标称值 ) = 1.8V时为1.5V,对于(V_{DDEXT})(标称值 ) = 2.5V时为1.5V 。

输出使能时间测量

当输出引脚从高阻抗状态转变为开始驱动时,视为输出引脚被使能。

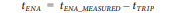

输出使能时间(t_{ENA})是从参考信号达到高电平或低电平,到输出开始驱动的时间间隔,如图46右侧所示。

时间(t_{ENA_MEASURED})是参考信号切换到输出电压达到(V_{TRIP})(高 )或(V_{TRIP})(低 )的时间间隔。

对于(V_{DDEXT})(标称值 ) = 1.8V,(V_{TRIP})(高 ) = 1.3V,(V_{TRIP})(低 ) = 0.7V 。

对于(V_{DDEXT})(标称值 ) = 2.5V/3.3V,(V_{TRIP})(高 ) = 2.0V,(V_{TRIP})(低 ) = 1.0V 。

时间(t_{TRIP})是输出从开始驱动到输出电压达到(V_{TRIP})(高 )或(V_{TRIP})(低 )的时间间隔。

(t_{ENA})按以下公式计算:

如果多个引脚(如数据总线)被使能,测量值为第一个开始驱动的引脚的值。

图46. 输出使能/禁用

输出禁用时间测量

当输出引脚停止驱动并进入高阻抗状态时,视为输出引脚被禁用。

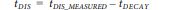

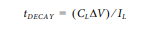

输出禁用时间(t_{DIS})是输出高电平或低电平开始从测量值下降(Delta V)的时间,它取决于电容负载(C_{L})和负载电流(I_{L}) 。此下降时间可通过以下公式近似计算:

时间(t_{DIS_MEASURED})和(t_{DECAY})如图45左侧所示。

示例系统保持时间计算

要确定特定系统中的数据输出保持时间,首先使用上述公式计算(t_{DECAY}) 。选择(Delta V)为处理器输出电压与所需保持时间的设备输入阈值之间的差值。(C_{L})是总总线电容(每条数据线 ),(I_{L})是总泄漏或三态电流(每条数据线 )。保持时间为(t_{DECAY})加上各种输出禁用时间,如第27页“定时规格”中指定的时间(例如SDRAM写周期中的(t_{DSWAT}) ,见第30页“SDRAM接口定时” )。

(t_{DECAY})在测试负载(C_{L})和(I_{L}) 下计算,对于(V_{DDEXT})(标称值 ) = 1.8V,(Delta V)等于0.1V;对于(V_{DDEXT})(标称值 ) = 3.3V,(Delta V)等于0.5V 。

时间(t_{DEC_MEASURED})是参考信号切换到输出电压从测量输出高电平或输出低电平下降(Delta V)的时间间隔。

-

ADSP - BF531/ADSP - BF532/ADSP - BF533:高性能嵌入式处理器的深度剖析2026-03-23 889

-

EE-197:ADSP-BF531/532/533 Blackfin处理器多周期指令和延迟2025-01-08 584

-

AN-813: ADSP-BF533/ADSP-BF561 Blackfin处理器与高速并行ADC接口2025-01-06 437

-

ADSP-BF531BF532BF533 2.53.3V IO Blackfin处理器IBIS数据文件160-Ball CSP BGA封装(092005)2021-06-09 986

-

BF533-EZ ADSP-BF533 EZ-Kit Lite评估硬件为评估ADSP-BF531、ADSP-BF532和ADSP-BF533 Blackfin处理器系列提供低成本硬件解决方案。2021-06-03 1082

-

ADSP-BF531/BF532/BF533修订版0.5、0.6的Blackfin异常列表2021-05-27 1103

-

ADSP-BF531/BF532/BF533黑丙烯BSDL 176-Pin LQFP包(02/2004)2021-05-21 957

-

ADSP-BF531/BF532/BF533黑球BSDL 169球PBGA包(02/2004)2021-05-20 824

-

ADSP-BF531/ADSP-BF532低功耗通用Blackfin处理器2021-05-16 1498

-

EE-197:ADSP-BF531/532/533 Blackfin®处理器多周期指令和延迟2021-04-26 1218

-

ADSP-BF531/ADSP-BF532/ADSP-BF533:Blackfin嵌入式处理器数据表2021-04-15 1003

-

ADSP-BF531/BF532/BF533 Blackfin®功耗估算(Rev 4, 12/2007)2021-03-19 1196

-

ADSP-BF531 400MHz低成本Blackfin处理器2019-02-22 980

全部0条评论

快来发表一下你的评论吧 !