QDMA Subsystem for PCI Express v5.0产品指南

描述

AMD QDMA Subsystem for PCI Express( PCIe )旨在利用多队列的概念实现高性能 DMA,以搭配 PCI Express Integrated Block 一起使用,它与 DMA/Bridge Subsystem for PCI Express 的不同之处在于,后者使用多个 AMD 卡到主机( C2H )和主机到卡( H2C )通道。

本指南适用于面向 AMD UltraScale+ 器件的 QDMA Subsystem for PCIe。

功能特性

AMD UltraScale+ 器件中支持 PCIe Integrated Block( PCIe 集成块)。

支持 64、128、256 和 512 位数据路径。

支持 x1、x2、x4、x8 或 x16 链路宽度。

支持 Gen1、Gen2 和 Gen3 链路速度。Gen4 用于 PCIE4C 和 PCIE4CE 块。

支持 AXI4 存储器映射接口和 AXI4-Stream 接口(按队列)。

2048 个队列集合

2048 个 H2C 描述符环。

2048 个 C2H 描述符环。

2048 个 C2H 完成( CMPT ) 环。

支持轮询模式(状态描述符写回)和中断模式。

中断

2048 个 MSI-X 矢量。

每个功能最多 8 个 MSI-X。

中断聚合。

C2H 串流中断调制。

C2H 串流完成队列条目合并。

通过用户逻辑进行描述符和 DMA 自定义

允许定制描述符格式。

流量管理。

支持含最多 4 个物理功能( PF )和 252 个虚拟功能( VF )的 SR-IOV

精简虚拟机管理器型号。

QID 虚拟化。

仅允许有特权的功能/物理功能对上下文和寄存器进行编程。

支持功能级别复位( FLR )。

邮箱。

基于队列的丰富可编程性,例如,AXI4 存储器映射接口对比 AXI4-Stream 接口。

概述

Queue-based Direct Memory Access( QDMA )基于队列的直接存储器访问子系统是基于 PCI Express ( PCIe )的 DMA 引擎,该引擎专为满足高带宽和高包计数数据传输需求而优化。QDMA 由 AMD UltraScale+ Integrated Block for PCI Express 以及广泛的 DMA 和 Bridge 基础架构组成,可实现卓越的性能和灵活性。

QDMA Subsystem for PCIe 提供了广泛的设置和使用选项,大部分设置和选项均可按队列来选择,例如存储器映射 DMA 或串流 DMA、中断模式和轮询。该子系统提供了诸多选项,用于通过用户逻辑来自定义描述符和 DMA,以提供复杂的流量管理功能。

QDMA 引擎可凭借使用 QDMA 进行数据传输的主要机制来对主机操作系统所提供的指令(描述符)进行操作。QDMA 可使用描述符在主机到卡( H2C )方向或卡到主机( C2H )方向进行数据移动。您可基于逐个队列选择 DMA 流量 是进入 AXI4 存储器映射( MM )接口还是进入 AXI4-Stream 接口。此外,QDMA 可以选择实现 AXI4 MM 主端口或实现 AXI4 MM 从端口,从而允许 PCIe 流量完全绕过 DMA 引擎。

QDMA 与其他 DMA 产品的主要区别在于队列的概念。队列的概念源自高性能计算( HPC )互连的远程直接存储器访问( RDMA )的“队列集”概念。这些队列可以通过接口类型进行单独配置,并且能够在许多不同的模式下工作。基于单个队列加载 DMA 描述符的方式,每个队列均可提供极低开销的建立时间选项和连续更新功能。通过将队列作为资源分配给多个 PCIe 物理功能( PF )和虚拟功能( VF ),即可在各种多功能和虚拟化应用空间中使用同一个 QDMA 核与 PCI Express 接口。

QDMA 架构

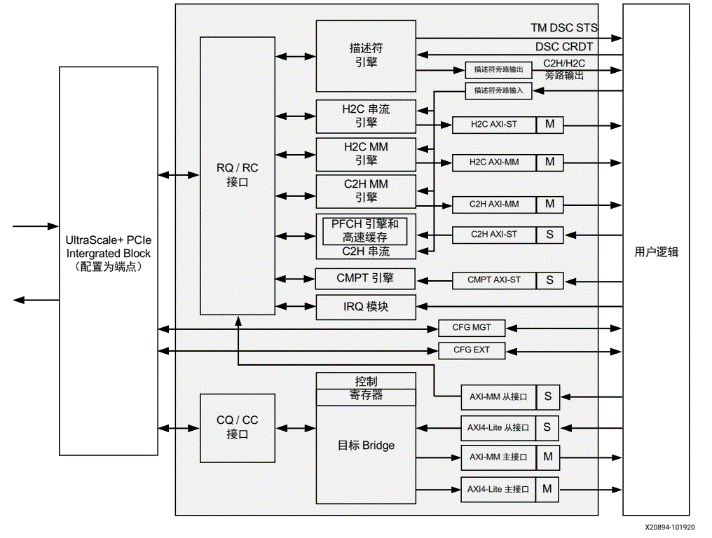

下图显示了 QDMA Subsystem for PCIe 的模块框图。

- 相关推荐

- 热点推荐

- amd

- 存储器

- UltraScale

-

STM32电机控制SDK v5.0入门2024-03-11 818

-

Multi-Channel PCIe QDMA&RDMA IP应用介绍2024-02-22 808

-

UltraScale+器件用于PCI Express的集成模块产品指南2023-09-14 1429

-

UltraScale+器件Integrated Block for PCI Express v1.3产品指南2023-09-13 526

-

力科推出PCI Express 5.0开放网络接口卡3.0信号采集卡2022-05-16 3587

-

DLC美国能效V5.0标准的测试内容2020-04-21 614

-

DLC发布V5.0版本增加哪些测试要求2020-02-24 1004

-

PCI Express逻辑分析仪探测设计指南2019-08-07 1717

-

Sprint-Layout V5.0免安装中文版2013-03-11 1356

-

PCI Express插槽,什么是PCI Express插槽2009-04-26 5611

-

PCB工具箱 V5.0 Protel实用外挂程式2006-03-12 2184

全部0条评论

快来发表一下你的评论吧 !