DS28E54 1-Wire SHA3-256安全认证器,兼容DS2431/DS28E07技术手册

描述

概述

DS28E54 安全身份验证器结合了 FIPS 202- 合规的安全哈希算法 (SHA-3) 质询和 响应身份验证,带 Secured Electrically 可擦除可编程只读存储器 (EEPROM)。

该设备提供了一组核心加密工具 源自集成模块,包括 SHA-3 引擎、2.25Kbit 安全用户 EEPROM、一个 仅递减计数器和唯一的 64 位 ROM 标识号 (ROM ID),同时保留 反向兼容于DS2431/DS28E07。

唯一的 ROM ID 用作基波输入 参数进行加密作,并用作 应用程序中的电子序列号。

该器件通过单触点 1- 进行通信 Wire^®^ 总线。

通信遵循 1-Wire 协议,其中 ROM ID 在 多器件1-Wire网络。

数据表:*附件:DS28E54 1-Wire SHA3-256安全认证器,兼容DS2431 DS28E07技术手册.pdf

应用

- 医疗工具/配件鉴定和校准

- 附件和外设安全认证

- 电池认证和充电周期跟踪

- 模拟传感器校准

特性

- DS2431/DS28E07反向兼容

- 2.25Kb EEPROM 存储器,分为 11 个 256 位的用户页(兼容前 5 页)

- 64 位暂存器缓冲器,用于兼容具有偏移和单独寻址的安全写入

- ±8kV HBM ESD 保护(典型值)用于 IO 引脚

- 用于验证外设的高效安全哈希算法

- 符合 FIPS 202 标准的 SHA-3 算法,用于质询/响应身份验证和设备禁用

- 符合 FIPS 198 的密钥哈希消息身份验证代码 (HMAC)

- 可选的 HMAC SHA3-256 认证的 EEPROM 写保护

- 易于集成到终端应用的补充功能

- 17位、一次性可设置、非易失性仅递减计数器,具有经过验证的读取功能

- 密钥的安全存储

- 2.25KBits 的安全 EEPROM,用于用户数据和密钥

- 唯一且不可更改的工厂编程 64 位标识号 (ROM ID)

- 先进的 1-Wire 协议最大限度地减少了与单个触点的接口

- 标准和高速通信速度

- 内部寄生电源电容器

- 工作范围:2.8V 至 5.25V,-40°C 至 +85°C

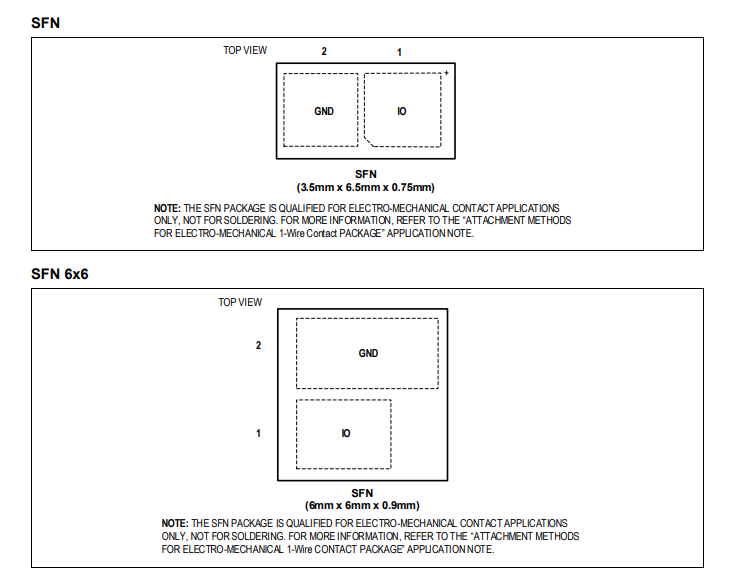

- SFN、SFN 6x6、TDFN-EP、TSOC、TO92 封装

- 4.0μA (典型值) 输入负载电流

简化应用程序图

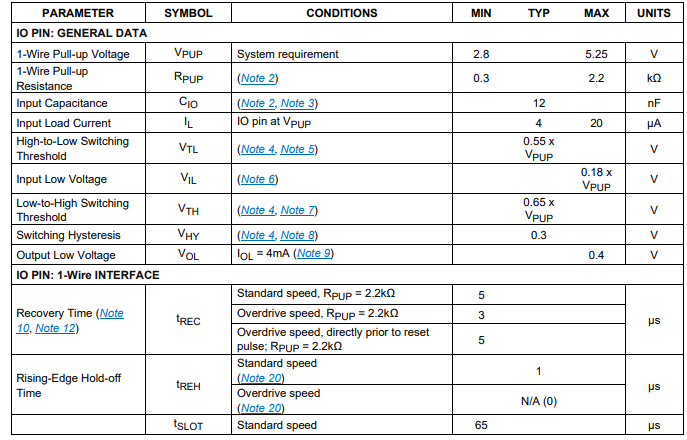

电特性

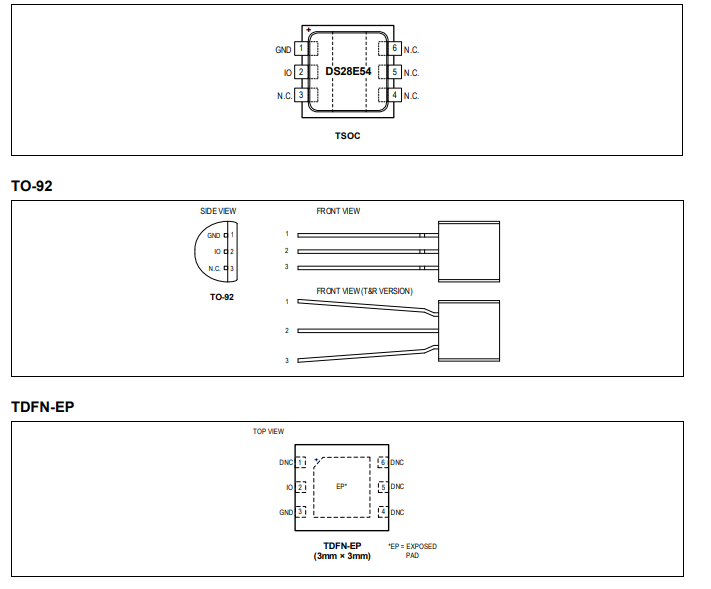

引脚配置

一线制信号传输与时序

DS28E54需要严格的协议来确保数据完整性。该协议包括在单线上的四种信号类型:带有复位脉冲和存在脉冲的复位序列、写0、写1和读数据。除存在脉冲外,总线控制器发起所有下降沿。DS28E54可在两种速度下通信:标准速度和超速。除非明确设置为超速模式,否则DS28E54以标准速度通信。在超速模式下,快速时序适用于所有波形。

要从空闲状态变为活动状态,一线制总线上的电压需要从VpUp下降到阈值VT_L以下。要从活动状态变为空闲状态,电压需要从VILMAX上升到阈值VT_H以上。电压完成此上升所需的时间在图4中表示为ε,其持续时间取决于所使用的上拉电阻(RpU)以及连接的一线制网络的电容。VILMAX电压在确定DS28E54的逻辑电平时相关,而非用于触发任何事件。

图4展示了与DS28E54开始任何通信所需的初始化序列。一个复位脉冲后跟一个存在脉冲表明DS28E54已准备好接收数据,前提是发送了正确的ROM和设备功能命令。如果总线控制器在下降沿使用斜率控制,则必须将线路拉低持续时间为tRSTL + tF,以补偿边缘效应。tRSTL的持续时间在标准速度下为480µs,在超速模式下为80µs,之后设备恢复到标准速度。对于DS28E54,在超速模式下tRSTL不能超过80µs,否则设备将保持在超速模式。如果设备处于超速模式且tRSTL在80µs到480µs之间,设备将复位,但通信速度不确定。

总线控制器释放线路后,其进入接收模式。然后,一线制总线通过上拉电阻被拉高到VpUp,或者在特殊情况下,通过有源电路拉高到VpUp。接下来,一线制总线被拉低VpUp,通过将线路拉低来触发下降沿。当跨越阈值VT_H时,DS28E54等待1µs,然后传输存在脉冲。为检测存在脉冲,控制器必须在1µs时测试一线制线路的逻辑状态。

tRSTH过期后,DS28E54立即准备好进行数据通信。在混合设备网络中,tRSTH在标准速度下应至少延长至480µs,在超速速度下应至少延长至48µs,以适应其他一线制设备。

-

DS28E16 1-Wire Secure SHA-3 Authenticator:安全认证的理想之选2026-04-01 126

-

DS28E83 DeepCover耐辐射1-Wire安全认证器技术手册2025-05-14 1085

-

DS28E16 1-Wire SHA-3安全认证器技术手册2025-05-13 1274

-

DS28E40: Deep Cover Automotive 1-Wire Authenticator Data Sheet DS28E40: Deep Cover Automotive 1-Wire Authenticator Data Sheet2023-10-17 65

-

DS28E25: DeepCover Secure Authenticator with 1-Wire SHA-256 and 4Kb User EEPROM Data Sheet DS28E25: DeepCover Secure Authenticator with 1-Wi2023-10-16 51

-

DS2431和DS28E07的区别2023-02-07 4106

-

DS2431芯片概述2022-02-11 2057

-

DS28E35 DeepCover安全认证器的特点及应用介绍2018-10-09 5122

全部0条评论

快来发表一下你的评论吧 !