这个时钟是谁的啊!?

描述

一背景

各位工程师你们好,相信各位在入门整改时都被这个问题困扰过,绕过几次弯路后,成功晋升大佬。大家对于时钟问题的排查也越发熟练了,那是否有一套连招,可以快速帮我们捋清楚整改排查的思路呢?

结果是必然的,是可以总结借鉴的。持续精进一直是我司价值观之一,把问题简单化,思路具象化是我们可以快速提升的方法之一。无论是时钟问题还是电源问题,对于问题的排查思路是我们整改工程师最需要具备的能力,这里没有之一!因为当我们复盘案件时,会发现大部分时间都在排查阶段。吉德林法则:把难题清清楚楚地写出来,便已经解决了一半。今天我们一起讨论一下时钟问题的排查思路。

二案例分析

话不多说,举个例子!

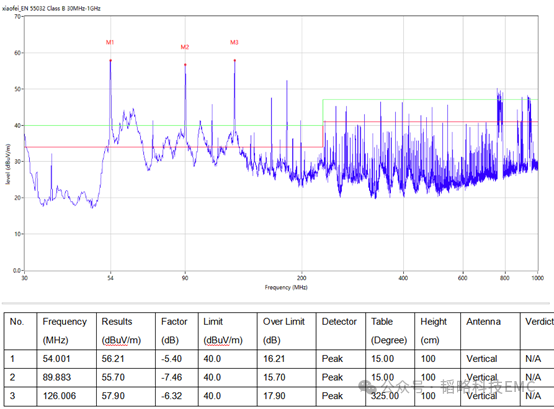

1.案例的产品是一款全金属外壳的户外红外安防摄像头,主要的问题当然是时钟问题超标,摸底测试数据如下:

看一下受害人笔录:

在那次失败的认证场地中,凶手就是他们仨!54!90!126!

(锁定超标时钟频率)

也不知道他们仨是不是同宗同源的一家人,间隔36mhz。

(找寻时钟间隔规律)

事发当时好像还有其他人,也不知道他们是不是一伙的!

(多个时钟的排查,则需要弄清楚时钟相互间隔关系,给他们分别记在小本本上面)

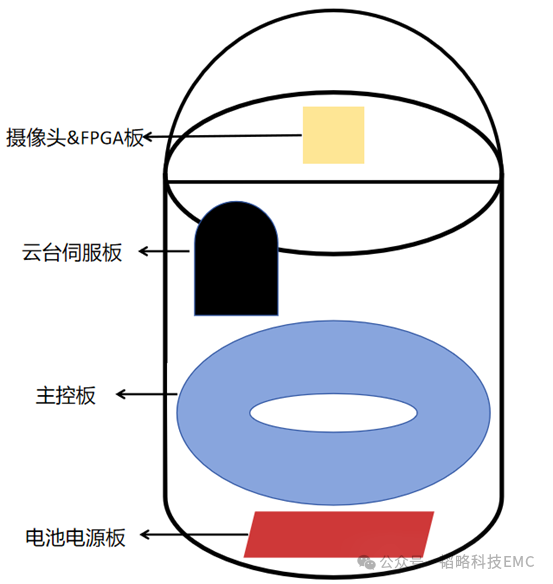

2.场面一度混乱,我们还是看一下案发当地情况吧,一起看看产品结构吧。

好的,进入谁是卧底环节了,本来是想一个一个拎出来,掏出我们的频谱仪审讯。但是武功秘籍第二页说:一个一个扫多慢啊,直接给他们电掐掉!(非常高效的措施:从外部断模块,找到接插件就是一顿插拔!)

先是切断电池电源板出来的线束,虽然机器本身是电池供电,是干净的,但是防止时钟噪声从线束耦合辐射出来。这一步时钟是有所下降的,证明时钟噪声的路径多数是从线束出去,但是数据仍然超标。

接下来我们拔掉主控板上的线束,主控板有三个接插件,分别是:

(1)向上连接的主板与云台信号的通讯线;

(2)向上连接FPGA板的通讯和电源线;

(3)向下连接的通讯和电源线。

我们对比着数据依次拔掉,发现拔掉连接FPGA的接插件时,数据有明显下降。虽然已经基本锁定嫌疑人了,但是本着对排查思路的严谨性,在整改的过程中时时刻刻抓住整改三要素:

(1)噪声源;

(2)耦合路径;

(3)敏感设备。

需要更多的信息排除其他可能性,追根溯源,让切断模块进行的更彻底,让噪声源头更具体,让耦合路径也更清晰。

继续拔!一路向上!第三块板云台伺服板,这个板上除了控制电机部分,就是传输FPGA板信号通讯和电源转接路过的接插件。分别断开有关云台的通讯和电源后,数据毫无变化,进一步佐证噪声源头不是云台伺服板。

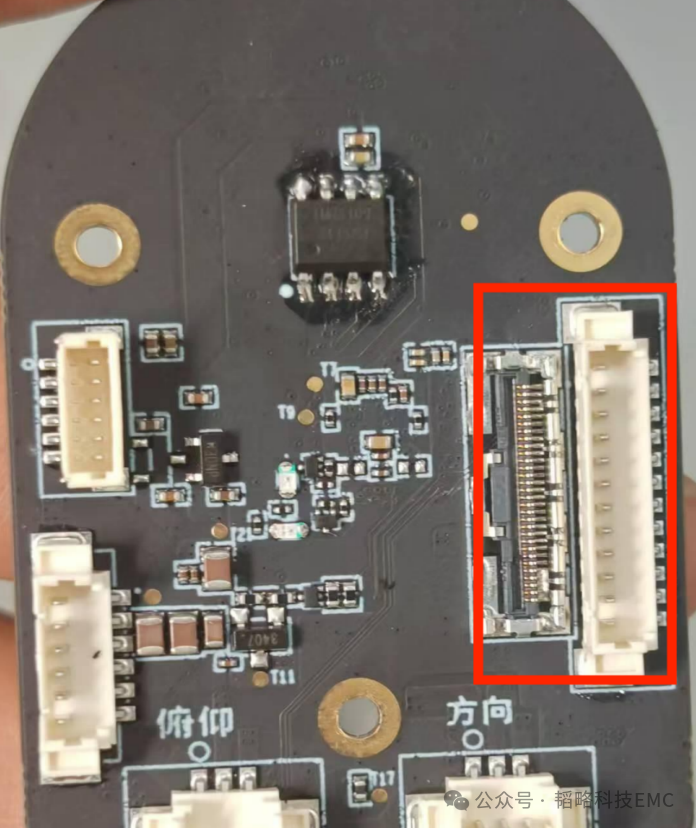

最后一块板子,在拔掉FPGA板向下传输的线束后,时钟信号就没有了。通过频谱仪探测,在FPGA板上找到了源头DVP信号,设置的基准值为18MHz。端口输出到云台伺服板是红框左边的金属结构件,再通过红框右边的塑胶端口座子向下传输,且整条链路只有一条地线。单点接地,接地质量地,阻抗突变,导致链路成为主要耦合路径,自上而下污染其他线束。

当然在我们实际的整改中走了不少弯路,通过各种简单或复杂的手段验证,武功秘籍中还记载了:排除法、频谱分析仪频点搜索法、元件固有频率分析法等等,例如在外部通过绕磁环、区域断模块、区域接地降低阻抗,区域屏蔽模块,频谱找点,模块固定频率点筛查等,这些都是为了更快速的锁定噪声源,也可更好的区分主次要耦合路径。

三整改措施

我们找到噪声源头是:FPGA 板传输的DVP 信号,设置的基准值为18MHZ。

耦合路径是:FPGA输出DVP信号的所有路径,竖直方向从板内接插件向下传输的线束以及被耦合的所有路径。

根据这两点我们有以下措施可以做:

1.噪声源:

在源头做处理,使用我司的王牌产品——展频晶振;为FPGA提供已经有展频(扩频)的时钟。后续输出时钟自带展频效果,从而降低时钟尖峰的能量强度,这也是最简单最高效的手段。

2.耦合路径:

在耦合路径上有诸多环节,武功秘籍上说越靠近源头越有效果,例如:

(1)滤波:DVP信号输出的地方,增加RC或LC滤波。

(2)吸收:串磁珠、绕磁环和贴吸波材料,注意要根据各自的吸收频率范围来选择。

(3)接地:时钟信号包地、单点接地变多点接地、加强接地质量,降低噪声回路阻抗。

(4)屏蔽:屏蔽罩、金属外壳屏蔽、屏蔽线束。

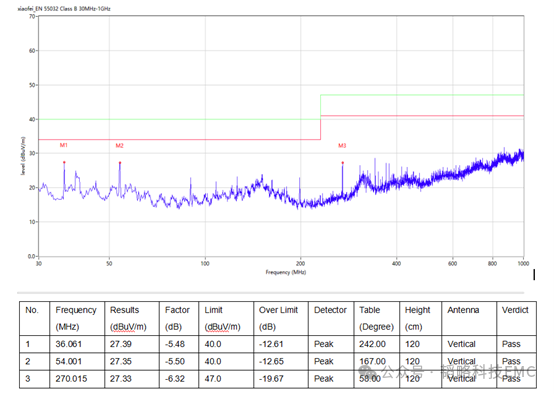

最后的数据如下:

四总结

时刻牢记EMC整改三要素,解决措施都是次要,整改排查的思路才是主要的。在排查验证的时候切记手段一定要考虑周全,一定要排查彻底。面对单板甚至多板的情况,思路则要更加清晰具体,控制好变量逐一对比。另外很多时候噪声源和耦合路径并不止一个,所以发现验证的手段没有改善,一般不用改回去。我们大可在得到有改善的数据时,一步步做减法,找到最关键的手段或措施即可。

-

CMEMS,谁吃过这个螃蟹?2014-03-28 6541

-

HX711这个AD的软件 51 c 谁用过啊,求代码!2015-10-25 2926

-

谁可以帮忙设计一个同时实现时钟和倒计时功能的时钟,有酬2017-02-20 3495

全部0条评论

快来发表一下你的评论吧 !