DS28E50具有ChipDNA PUF保护的DeepCover安全SHA-3认证器技术手册

描述

概述

DS28E50安全认证器将FIPS202兼容安全散列算法(SHA-3)质询和响应认证与Maxim拥有专利的ChipDNA ^™^ 技术结合在一起,后者的物理不可克隆功能(PUF),为实现针对安全攻击的终极保护提供了经济有效的解决方案。ChipDNA方法利用半导体器件在晶圆制造期间自然发生的随机特征变化,ChipDNA电路生成一个唯一输出值,该值在时间、温度和工作电压上是可重复的。任何探测或观测ChipDNA操作的尝试都将改变底层电路特征,防止侦测芯片加密功能使用的唯一值。DS28E50利用ChipDNA输出作为密钥内容,对器件储存的全部数据进行安全加密。利用ChipDNA能力,器件提供一组基于集成电路的核心加密工具,包括SHA-3引擎、FIPS/NIST兼容真随机数发生器(TRNG)、2Kb安全EEPROM、仅递减计数器和唯一的64位ROM识别码(ROM ID)。唯一的ROM ID用作加密运算的基本输入参数,也作为应用中的电子序列号。DS28E50通过单触点1-Wire®总线通信,支持标准速率和高速率。通信采用1-Wire协议,ROM ID作为多器件1-Wire网络中的节点地址。

数据表:*附件:DS28E50具有ChipDNA PUF保护的DeepCover安全SHA-3认证器技术手册.pdf

应用

- 医疗传感器和工具安全认证

- IoT节点安全认证

- 外设认证

- 打印机墨盒识别及安全认证

- 授权管理的参考设计

- 受限耗材安全管理

特性

- 可靠反制措施,防御安全攻击

- 拥有专利的物理不可克隆功能确保器件数据安全

- 主动监测芯片屏蔽,对企图入侵进行监测并做出反应

- 所有储存的数据采用加密保护,防止侦测

- 安全散列算法对外设进行认证

- FIPS 202兼容的SHA-3算法,支持质询/应答安全认证

- FIPS 198兼容的密钥散列信息验证代码(HMAC)

- TRNG具有NIST SP 800-90B兼容的熵源

- 附加特性便于集成到最终应用

- 17位一次性可设置、非易失仅递减计数器,带安全认证读操作

- 一个GPIO引脚,带有可选的安全认证控制

- 2Kb EEPROM,可用于用户数据、密钥和控制寄存器

- 唯一且不可更改的工厂编程64位识别码(ROM ID)

- 单触点,1-Wire接口与主机通信,速率为11.7kbps和62.5kbps

- 工作电压范围:3.3V ±10%,-40°C至+85°C

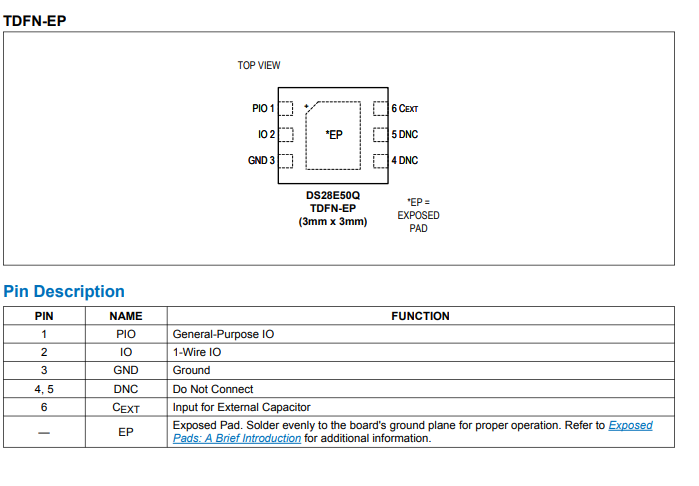

- 6引脚TDFN-EP封装(3mm x 3mm)

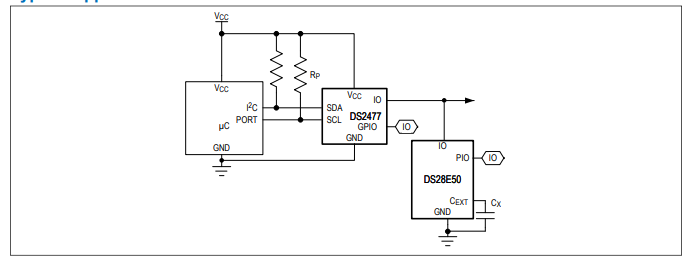

典型应用电路

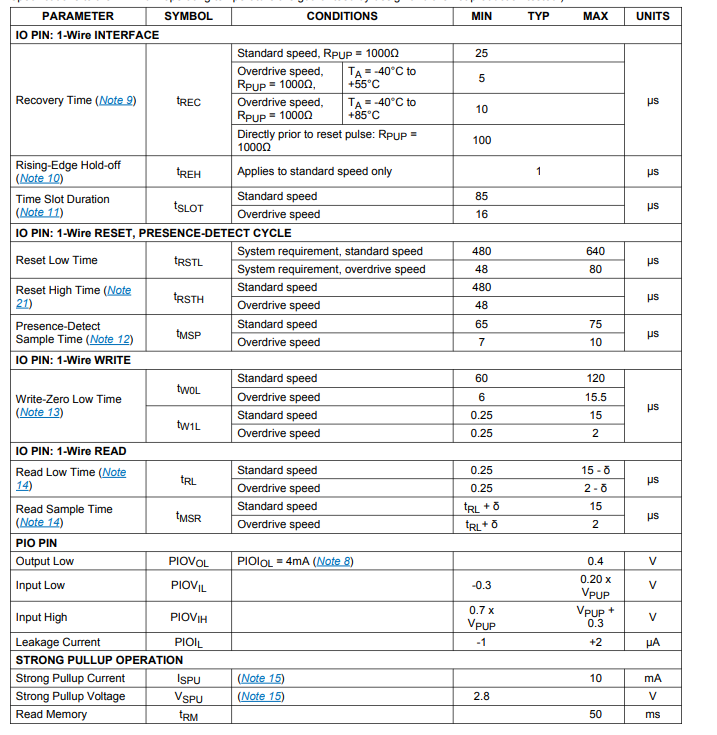

电特性

引脚配置描述

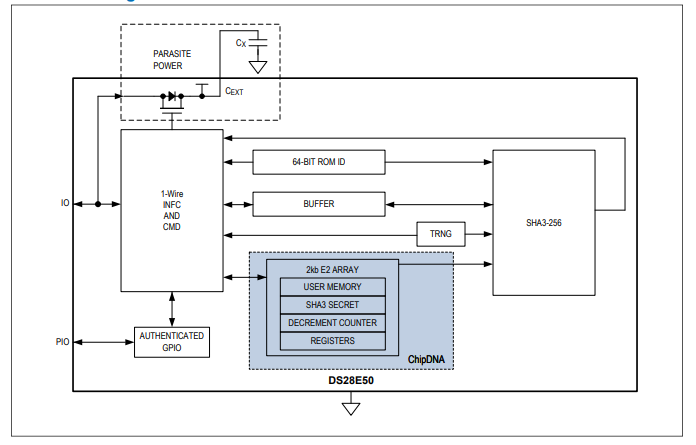

逻辑图

详细说明

DS28E50集成了亚德诺半导体(Analog Devices)的芯片DNA功能,可保护设备存储的所有数据不被侵入式获取。除了物理不可克隆功能(PUF)和用于签名的SHA - 3引擎外,该设备还集成了符合FIPS/NIST标准的真随机数发生器(TRNG)、2kb用于用户存储的电可擦可编程只读存储器(EEPROM)、SHA - 3保密存储区和控制寄存器。用户页面可选择指定为递减计数器。PIO引脚可在命令控制下独立运行,支持经过认证和未经认证的操作模式。该设备通过外部电容实现寄生供电,采用1 - 线接口。

设计资源概述

DS28E50的运行涉及设备EEPROM的使用以及设备功能命令的执行。以下部分提供了包括递减计数器在内的概述。详细信息请参考《DS28E50安全用户指南》。

存储器

一个2kb的安全EEPROM阵列,用于SHA - 3保密存储,还可用于递减计数器以及/或者通用的用户可编程存储器。根据存储空间的不同,有默认或用户可编程选项来设置保护模式。

通用目的输入/输出(GPIO)

开漏PIO引脚可以通过经过认证或未经认证的方式进行读取和控制。经过认证的操作包括防止重放攻击的措施。上电时,PIO引脚的默认状态为高阻抗。

功能命令

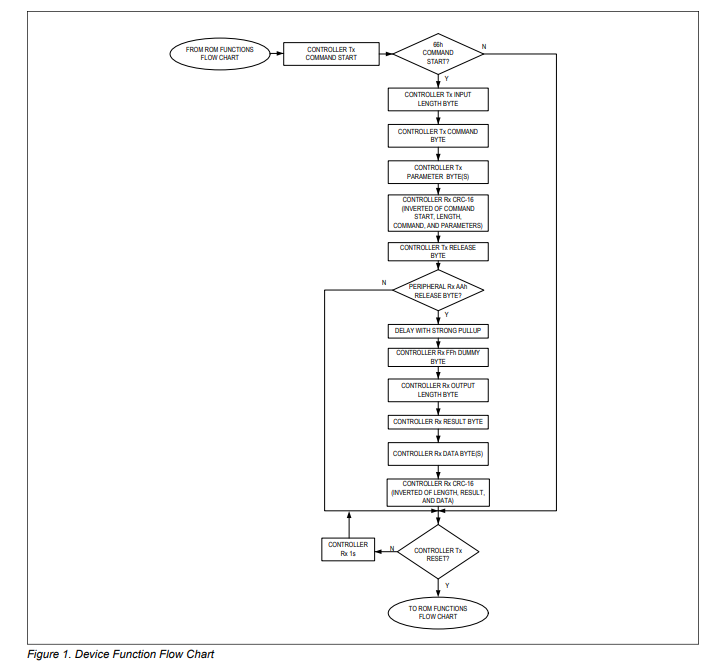

在1 - 线复位/存在脉冲周期以及ROM功能命令序列成功完成后,便可接收命令起始,随后是设备功能命令。一般来说,这些命令请参照图1。在此图表中,数据传输在写入和读取时通过16位循环冗余校验(CRC - 16)进行验证。CRC - 16的计算方法详见《使用循环冗余校验实现美信1 - 线和iButton产品中的数据验证》。

递减计数器

可选的17位递减计数器可对双用途存储页进行一次性写入。有一个专用的设备功能命令用于将计数值减1,且每次调用只减1 。当计数值达到0时,无法再进行递减操作。

1 - 线总线系统

1 - 线总线系统有一个总线控制器和一个或多个外设。在任何情况下,DS28E50都是外设设备。总线控制器通常是微控制器或像DS2477这样的协处理器。本系统的讨论分为三个主题:硬件配置、事务序列和1 - 线信号(信号类型和时序)。1 - 线协议根据总线控制器同步脉冲下降沿启动的特定时隙内的总线状态来定义总线事务。

-

深度解析DS28C39:具备ChipDNA PUF保护的安全双向认证器2026-04-01 125

-

DS28E39具有ChipDNA PUF保护的DeepCover安全ECDSA双向认证器技术手册2025-05-14 1069

-

DS28C16 I²C低电压SHA-3认证器技术手册2025-05-13 1125

-

SHA-3 Plus PUF形成强大的安全防护罩2022-05-25 2075

-

Maxim发布业界首款SHA3-256安全认证IC2018-10-21 5061

-

DS28E38 DeepCover安全认证器为IoT设计提供更好的攻击措施2018-10-12 3744

全部0条评论

快来发表一下你的评论吧 !