DS2476 DeepCover安全协处理器技术手册

描述

概述

DS2476为安全ECDSA和HMAC SHA-256协处理器,与DS28C36配套。协处理器可计算在DS28C36执行任何运算所必须的HMAC或ECDSA签名。DS2476提供一组核心的加密工具,集成非对称(ECC-P256)和对称(SHA-256)加密功能。除了硬件加密引擎提供的安全服务外,器件也集成FIPS/NIST真随机数发生器(RNG)、8Kb安全EEPROM、仅递减计数器、双引脚可配置GPIO和唯一的64位ROM识别码(ROM ID)。

ECC公钥/私钥功能采用NIST定义的P-256曲线,包括FIPS 186兼容的ECDSA签名发生和验证,支持双向对称密钥认证模式。SHA-256密钥功能兼容FIPS 180,可灵活地配合ECDSA使用或独立使用,实现多种HMAC功能。

两个GPIO引脚可通过命令控制独立工作,包括配置,支持安全认证和非安全认证操作,包括基于ECDSA的密码可靠模式,支持主机处理器安全引导。这种安全引导方法也可用于支持协处理器功能。

DeepCover®嵌入式安全方案采用多重先进的安全机制保护敏感数据,提供最高等级的密钥存储安全保护。为防止器件级安全攻击,实施了入侵和非入侵反制措施,包括有源芯片屏蔽、密钥存储器加密,以及基于算法的方法。

数据表:*附件:DS2476 DeepCover安全协处理器技术手册.pdf

应用

- 配件和外设安全认证

- 控制器

- IoT节点加密保护

- 参数

- 安全引导或下载固件和/或系统参数

- 安全储存主机的密钥

特性

- ECC-256计算引擎

- FIPS 186 ECDSA P256签名和验证

- ECDH密钥认证交换,防止中间人攻击

- ECDSA认证读/写可配置存储器

- FIPS 180 SHA-256计算引擎

- HMAC

- ECDH SHA-256 OTP (一次性密码本)加密读/写可配置存储器(使用ECDH生成的密钥)

- 两个GPIO引脚,带有可选的安全认证控制

- 漏极开路,4mA/0.4V

- 可选SHA-256或ECDSA安全认证开/关以及状态读取

- 可选ECDSA证书,在多块哈希算法之后设置为开/关,实现安全引导

- RNG带有NIST SP 800-90B兼容熵源,带有读出功能

- 可选芯片产生的私钥/公钥对,用于ECC运算

- 17位一次性可设置、非易失仅递减计数器,带安全认证读操作

- 8Kb EEPROM,用于用户数据、密钥和证书

- 唯一且不可更改的工厂编程64位识别码(ROM ID)

- 可选输入数据元素,用于加密和密钥运算

- I²C通信,100kHz和400kHz

- 工作范围:3.3V ±10%,-40°C至+85°C

- 6引脚TDFN封装

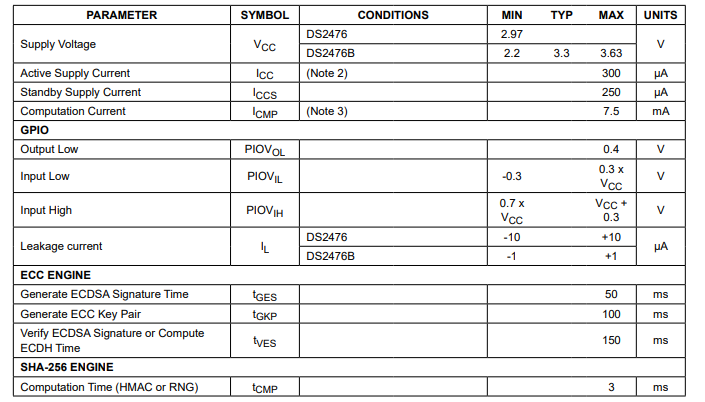

电特性

引脚配置描述

I²C

一般特性

I²C 总线由一条数据线(SDA)和一条时钟线(SCL)组成,用于通信。SDA 和 SCL 都是双向线路,通过上拉电阻连接到正电源电压。当没有通信时,两条线均为高电平。连接到总线的输出级设备必须具有开漏或集电极开路,以实现线与功能。I²C 总线上的数据以字节为单位传输,标准模式下速率高达 100kbps,快速模式下高达 400kbps。DS2476 在这两种模式下均可工作。

在总线上发送数据的设备定义为发送器,接收数据的设备定义为接收器。控制通信的设备称为主机。主机控制从机,当各个从机被单独访问时,每个从机都必须有一个不与总线上其他设备冲突的从机地址。

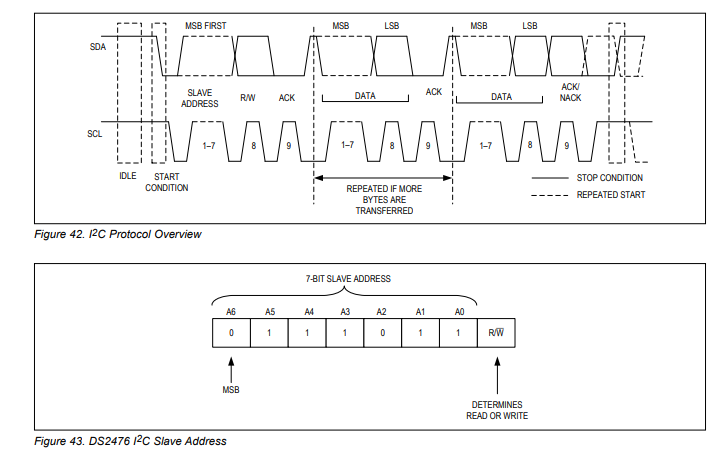

只有在总线不忙时才能启动数据传输。主机生成串行时钟(SCL),控制总线访问,生成起始(START)和停止(STOP)条件,并确定传输的数据字节数。数据在起始和停止条件之间传输(见图 42)。数据以字节为单位传输,最高有效位先发送。每个字节后面都跟随一个来自主机的确认位,以实现主机和从机之间的同步。

从机地址

DS2476 响应的从机地址如图 43 所示。从机地址是从机地址/控制字节的一部分。从机地址/控制字节的最后一位(R/W)定义数据方向。当设置为 0 时,后续数据从主机流向从机(写操作);当设置为 1 时,数据从从机流向主机(读操作)。

I²C定义

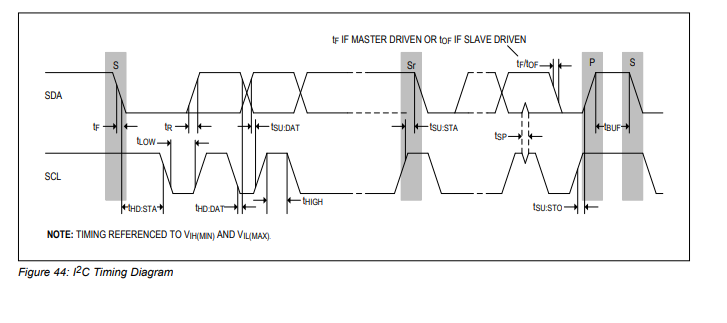

以下术语常用于描述I²C数据传输,其定时参考在图44中定义。

总线空闲或非忙状态

数据线(SDA)和时钟线(SCL)均处于非活动状态,且为逻辑高电平。

起始(START)条件

要与从机开始通信,主机必须生成一个起始条件。起始条件定义为:在时钟线(SCL)保持高电平期间,数据线(SDA)从高电平变为低电平。

停止(STOP)条件

要与从机结束通信,主机必须生成一个停止条件。停止条件定义为:在时钟线(SCL)保持高电平期间,数据线(SDA)从低电平变为高电平。

重复起始(Repeated START)条件

重复起始条件常用于在指定内存地址进行读访问后进行读操作。主机可以在数据传输结束时生成一个重复起始条件,以便紧接着启动新一轮数据传输。重复起始条件的生成方式与正常起始条件相同,但不会在停止条件后使总线进入空闲状态。

有效数据

除了起始和停止条件外,只有在时钟线(SCL)为低电平且稳定时,数据线(SDA)上的电平变化才有效。在整个SCL脉冲高电平期间,SDA上的数据必须保持稳定,且需满足建立时间(tSU_DAT )和保持时间(tHD_DAT )的要求(在SCL上升沿之前),见图44 。每个数据位对应一个时钟脉冲。在SCL脉冲上升沿期间,数据移入接收设备。

写操作完成时,主机必须在建立时间(最小tSU_DAT ,见图44 )之前释放SDA线,以便在SCL上升沿时有足够时间开始读操作。从机在SCL前一个脉冲的下降沿将每个数据位移出SDA线,并在SCL上升沿时将数据位的值锁存。主机必须生成所有SCL时钟脉冲,包括用于读操作的那些脉冲。

-

Analog Devices / Maxim Integrated DS2478 DeepCover®车用安全协处理器数据手册2025-06-22 583

-

DS2477具有ChipDNA PUF保护的DeepCover安全SHA-3协处理器技术手册2025-05-14 685

-

DS2478 DeepCover汽车安全协处理器技术手册2025-05-13 677

-

通过将DS5250用作安全协处理器来提高系统安全性2023-03-02 1520

-

DS2476Q+U 专用 IC2022-11-18 104

-

DS2476Q+T DS2476Q+T - (Maxim Integrated) - 专用 IC2022-11-16 95

-

RISC-V设计的基本安全协处理器2022-08-16 2176

-

RISC-V设计的基本安全协处理器PUFiot2022-06-01 4233

-

带有EEPROM的SHA1协处理器DS2460电子资料2021-04-20 1209

-

贸泽备货Maxim DS2477安全I2C协处理器 提供身份认证和物理安全性2019-06-02 1311

-

手机上的协处理器有什么作用_苹果协处理器是干什么的2018-04-24 22990

-

DS28EL25 DeepCover安全认证器 中文2013-08-23 1379

全部0条评论

快来发表一下你的评论吧 !