DS24L65 DeepCover安全认证器,具有SHA-256协处理器和1-Wire主机功能技术手册

描述

概述

DeepCover 嵌入式安全方案采用多重先进的物理安全机制保护敏感数据,提供最高等级的密钥存储安全保护。DeepCover安全认证器(DS24L65)是一款SHA-256协处理器,内置1-Wire ^®^ 主控制器,提供主机系统与1-Wire SHA-256从器件通信及操作所要求的SHA-256和存储器功能。此外,器件执行I²C主控制器与所连接的任何1-Wire SHA-256从器件之间的协议转换。对于1-Wire线驱动器,芯片内部用户可调定时器将系统主处理器从繁琐的1-Wire波形时序控制中解放出来,支持标准和高速1-Wire通信。1-Wire总线可通过软件控制关断。强上拉功能通过1-Wire总线为EEPROM等1-Wire器件供电。不使用DS24L65时,可将其置于休眠模式,降低功耗。

数据表:*附件:DS24L65 DeepCover安全认证器,具有SHA-256协处理器和1-Wire主机功能技术手册.pdf

应用

- 消费品认证

- 安全控制

特性

- SHA-256引擎,支持基于对称加密的双向安全认证模式

- 两页32字节用户EEPROM,带有多种可编程保护选项

- 1-Wire主控端口,带有可选的有源或无源1-Wire上拉

- 内部低阻信号通路提供1-Wire强上拉

- 1-Wire端口可通过软件控制关断

- I²C工作(上拉)电压:1.8V±5%

- IO与GND之间提供±8kV ESD保护(JESD22-A114 HBM,典型值)

- 工作范围:1.8V±5%,-40°C至+85°C

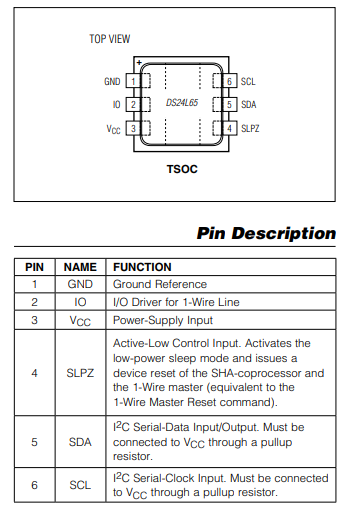

- 6引脚TSOC封装

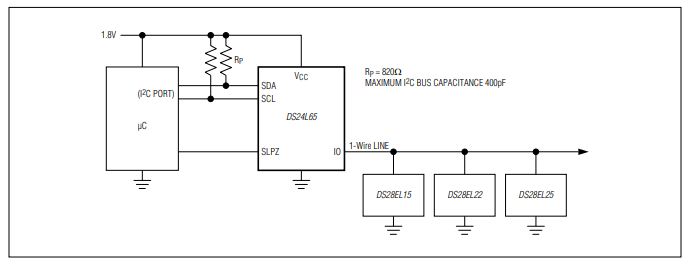

典型应用电路

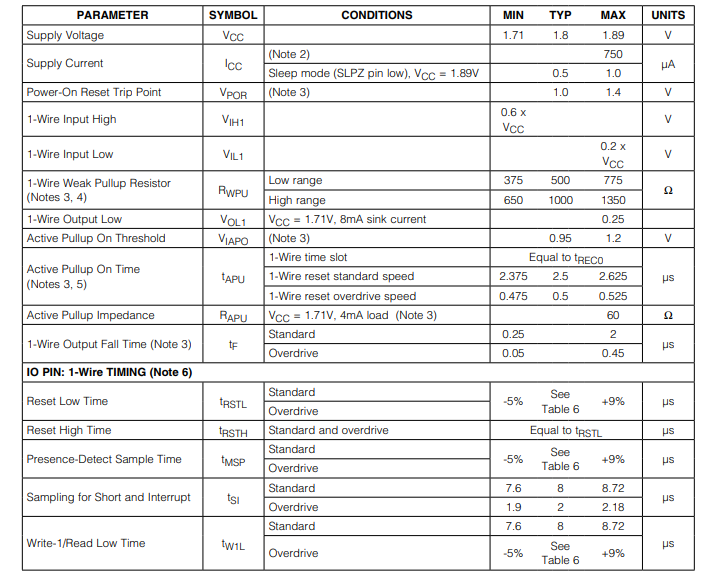

电特性

引脚配置描述

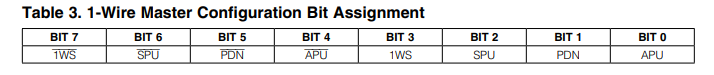

一线主设备配置寄存器(67h)

DS24L65支持四项一线特性,可通过一线主设备配置寄存器(表3)启用或选择。这些特性包括:有源上拉(APU)、一线供电(PDN)、强上拉(SPU)、一线速度(1WS)。APU和1WS可在任何通信周期内单独选择。而PDN和1WS在闲置时会恢复到非活动状态(如设置强上拉时)。

设备复位后(上电周期、SLPZ低电平脉冲,或通过一线主设备复位命令触发),一线主设备配置寄存器读取值为00h。向该寄存器写入数据时,仅当高四位(位7至位4 )与低四位(位3至位0 )互补时,新数据才会被接受。读取时,高四位始终为0。

位3:一线速度(1WS) :1WS位决定DS24L65发起的任何一线通信的时序。大多数一线从设备支持标准速度(1WS = 0 )。许多一线设备也能以更高的数据速率(称为超速)进行通信。部分一线设备,包括DeepCover SHA - 256系列从设备,仅支持超速,对于这些设备,1WS应始终设为高电平。要从标准速度切换到超速,一线设备需接收超速跳过ROM或超速匹配ROM命令,如一线设备数据表所述。在接收到速度变更命令代码后,DS24L65必须参与此速度变更以保持同步。这可通过在一线设备改变速度后,立即向一线主设备配置寄存器写入1WS位为1来实现。随后跟一个一线字节命令。向一线主设备配置寄存器写入1WS位为0 ,并跟随一线复位命令,可将DS24L65及总线上的任何一线设备的活动一线线路恢复到标准速度。

位2:强上拉(SPU) :SPU位用于在一线写字节、一线读字节或一线单比特命令之前激活强上拉功能。强上拉常用于一线EEPROM设备,在将暂存区数据复制到主存储器或执行SHA计算时。相应设备的数据手册会明确说明强上拉应在哪个通信协议步骤后应用。SPU位必须在向一线设备发送内部上拉以提供所需一线电压之前立即设置。强上拉使用与有源上拉相同的内部上拉晶体管。参考电气特性中的(R_{APU})参数来确定在给定负载电流和电源电压下,电压降是否足以维持活动一线电压。

如果SPU为1 ,DS24L65会将活动上拉时隙的上升沿视为强上拉,即内部上拉晶体管保持导通,如图3所示,直到出现以下四种情况之一:DS24L65接收到发起一线通信的命令(典型情况);SPU位在一线主设备配置寄存器中被写为1 ;PDN位在一线主设备配置寄存器中被写为0 ;或DS24L65接收到一线主设备复位命令。当强上拉结束时,SPU位会自动复位为0。使用强上拉功能不会改变一线主设备配置寄存器中APU位的状态。

-

DS1964S DeepCover安全认证器iButton,带SHA-256技术手册2025-05-14 1074

-

MAX66300带SHA-256和RFID读卡器的DeepCover安全认证器技术手册2025-05-13 1257

-

DS28EL22: DeepCover Secure Authenticator with 1-Wire SHA-256 and 2Kb User EEPROM Data Sheet DS28EL22: DeepCover Secure Authenticator with 1-2023-10-17 78

-

DS28E25: DeepCover Secure Authenticator with 1-Wire SHA-256 and 4Kb User EEPROM Data Sheet DS28E25: DeepCover Secure Authenticator with 1-Wi2023-10-16 52

-

安全协处理器/1-Wire® 主控器实现SHA-256认证2021-06-20 2668

-

DS2465 SHA-256协处理器与1-Wire主机功能2012-06-12 7248

全部0条评论

快来发表一下你的评论吧 !